FPGA图像处理,Sobel边缘检测算法Verilog实现,AXI_stream接口,可讲解实现方法或直接卖现成模块。

附带对应的matlab原理程序和一个简易的设计说明,可供参考。

~~~~~~~~~~~~~~

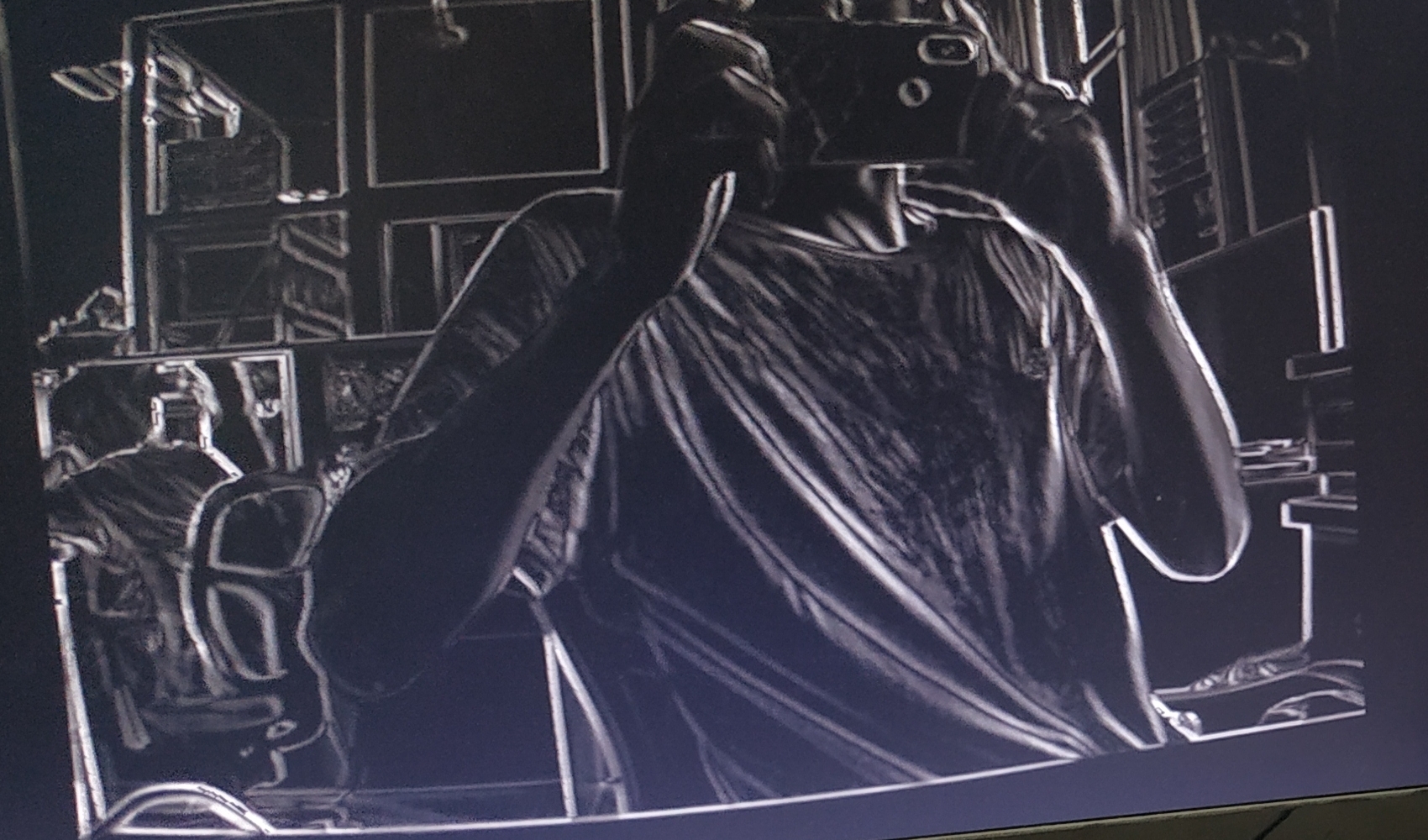

该模块是在Zynq的视频系统运行,axistream接口,其他情况可能需要修改接口,很早以前做的也没有写仿真,但确实如下图稳定运行的,因此没有仿真文件,特此说明。

ID:6960670512600283

白云黄鹤

FPGA图像处理在数字信号处理领域有着广泛的应用。本文将介绍使用Verilog语言实现Sobel边缘检测算法的FPGA图像处理模块,并通过AXI_stream接口与Zynq视频系统进行集成。文章还将提供相应的Matlab原理程序和设计说明以供参考。

一、引言

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具有高度灵活性和并行处理能力。图像处理是FPGA应用的一个重要领域,其快速且高效的特性使其成为实时图像处理的理想选择。Sobel边缘检测算法是常用的图像处理算法之一,具有简单、高效的特点。本文将通过Verilog语言实现Sobel边缘检测算法,并使用AXI_stream接口与Zynq视频系统进行集成。

二、Sobel边缘检测算法

Sobel边缘检测算法是一种基于图像梯度的算法,可用于检测图像中的边缘。该算法通过分别计算图像在水平和垂直方向上的梯度值,并对其进行组合,从而得到边缘图像。具体实现中,可以使用3x3的Sobel算子对图像进行卷积运算,得到水平和垂直方向上的梯度图像,然后通过计算梯度的幅值来确定边缘位置。

三、Verilog实现

本文使用Verilog语言来实现Sobel边缘检测算法。Verilog是一种硬件描述语言,适用于FPGA的设计和实现。通过使用Verilog语言,我们可以将Sobel算法的计算过程描述为硬件电路,并将其实现在FPGA芯片上。

在实现的过程中,我们将使用AXI_stream接口作为图像数据的输入和输出接口。AXI_stream是一种流式接口协议,可以实现高速、并行的数据传输。通过使用AXI_stream接口,我们可以实现Sobel算法与Zynq视频系统的连接。

四、集成与调试

在将Sobel边缘检测模块与Zynq视频系统进行集成时,需要根据实际情况进行接口的修改。在本文提供的设计说明中,我们对模块的接口进行了简要说明,并提供了一个可供参考的Matlab原理程序。通过参考设计说明和原理程序,可以帮助读者理解模块的使用方法以及与Zynq视频系统的集成方法。

在集成完成后,我们建议进行仿真验证,以确保模块的正确性和稳定性。然而,由于本模块是早期开发的成果,并没有提供仿真文件。但根据作者的说明,该模块在Zynq视频系统中稳定运行。因此,在使用该模块时,我们需要进行必要的修改和调试。

五、总结

本文介绍了FPGA图像处理中Sobel边缘检测算法的Verilog实现,并通过AXI_stream接口与Zynq视频系统进行集成。通过Verilog语言的硬件描述,我们可以将Sobel算法实现为一个FPGA模块,从而在图像处理方面提供高速、并行的计算能力。

在使用该模块时,我们需要根据实际情况进行接口的修改,并进行必要的调试和验证。尽管本文所提供的设计说明和Matlab原理程序可以作为参考,但读者仍需根据自己的需求和具体情况进行适当的修改和优化。

通过本文的介绍,读者可以了解到FPGA图像处理中Sobel边缘检测算法的实现方法以及与Zynq视频系统的集成技术。希望本文能为读者在图像处理领域的FPGA应用提供一些参考和启示。

相关的代码,程序地址如下:http://wekup.cn/670512600283.html

1419

1419

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?