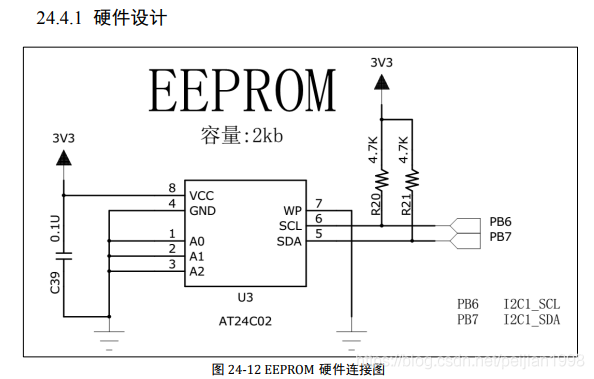

一、硬件设计

以上是EEPROM芯片AT24C02的硬件图。SCL和SDA引脚连接到了STM32对应的引脚上,结合

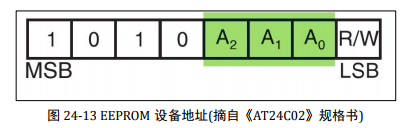

上拉电阻,构成了I2C通信总线。EEPROM芯片的设备地址一共由7位,其中高4位固定位1010b,

低3位则由A0/A1/A2信号线的电平决定。按照此图的连接,A0/A1/A2均为0,所以EEPORM的7位

设备地址是101 0000b。如下图所示,I2C通讯时地址跟读写方向一起构成一个8位数,当R/W位为

0时,表示写方向,电R/W位为1时,表示读方向。所以此处EEPROM芯片的写地址为0xA0,

读地址为0xA1。

EEPROM芯片还有一个WP引脚,具有写保护功能。当该引脚电平为高时,禁止写入数据,

当引脚电平为低时,可写入数据。此处直接接地,不使用写保护功能。

EEPROM芯片的最大特点是可按字节读写数据,掉电数据不丢失。

二、AT24C02时序

AT24C02共有2Kbit,256个字节的存储长度。其中,每8个字节一页,共32页。原文如下:

![]()

设备操作要求如下:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1049

1049

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?