1、A Multi-Step Incremental Analog-to-Digital Converter With a Single Opamp and TwoCapacitor SAR Extended Counting

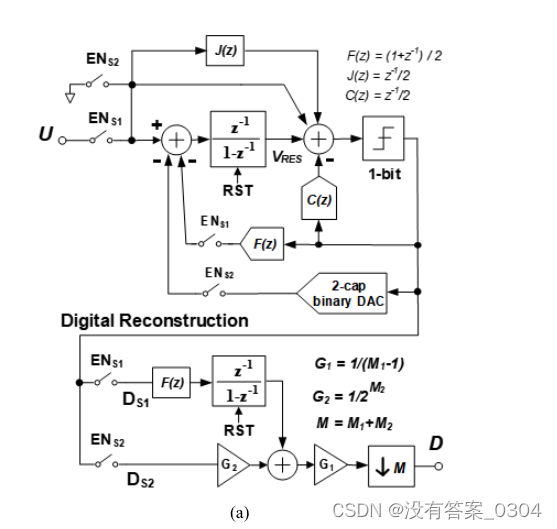

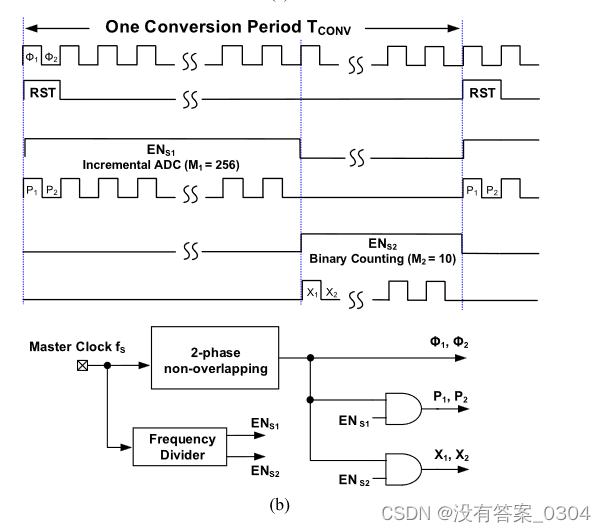

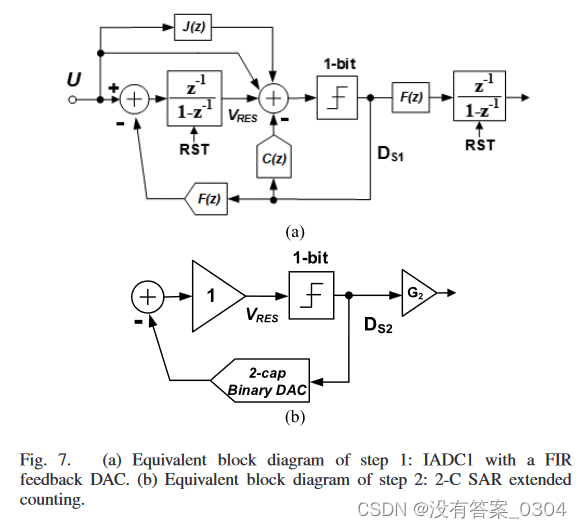

一阶IADC需要2N个过采样时钟周期才能达到N位分辨率。二阶或更高阶的调制器转换周期短,但稳定性较差,输入动态范围较窄。为了保留IADC1的优点,在IADC1之后使用奈奎斯特率ADC进行扩展计数可以非常显著地缩短转换时间,以较好的能效实现高分辨率。复位和FIR运算使得IADC更容易成为过采样和奈奎斯特率ADC的混合ADC。

对于高阶IADC,会引入会更大的噪声。为了维持相同的kT / C热噪声,输入采样电容尺寸必须相应增大。因此,增加的容性负载会耗散更多的功率。

OSR = 256的IADC1贡献8位分辨率,10位二进制搜索贡献额外的10位。整体SQNR为18 - bit。

为了减小积分器的输出步长,引入了两抽头FIR路径F ( z ) ,为了使信号传递函数( STF )恢复为1,加入了J ( z )

Conclusion:利用2 - C DAC的优势,提出了一种将IADC重构为2 - C SAR ADC进行扩展计数的方法。在两个步骤中只使用一个运放。0.18 μ m工艺,Fo M为175.8 d B,Walden Fo M为0.25 p J /转换步长,信噪比为96.6 d B。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?