现在电路设计中,信号发射无处不在,引起了各种信号完整性问题(过冲、回勾等),解决反射问题也是对硬件研发工程师的一项基本要求。

要了解信号反射必须先了解传输线和特征阻抗。在高速信号的视角,PCB走线是有损耗和延时的,一般常用RLGC模型表示。特征阻抗由PCB走线的宽度、PCB材质及厚度、以及走线形式(带状线或微带线)等共同决定的。

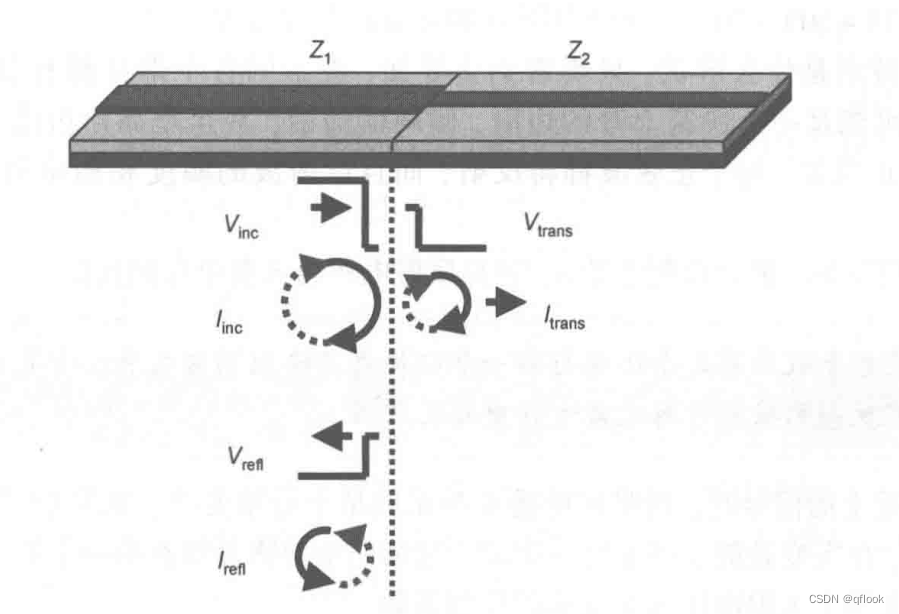

反射是怎么形成的呢?如下图所示,区域1和区域2阻抗不一致,则在接触位置产生了反射:

实际情况中,电压和电流肯定要连续,也决定了V1=V2和I1=I2,则Z1=V1/I1=V2/I2=Z2,但是Z1却不一定等Z2,那么哪里的问题呢?

实际情况中,电压和电流肯定要连续,也决定了V1=V2和I1=I2,则Z1=V1/I1=V2/I2=Z2,但是Z1却不一定等Z2,那么哪里的问题呢?

为了使整个系统稳定,在区域1引入了一个反向的反射电压Vrefl,和反射电流Irefl。则V2(Vtrans)=V1(inc)+Vrefl;I2(Itrans)=I1(Iinc)-Irefl,如下图:

推导公式则可计算出反射系数和传输系数:

推导公式则可计算出反射系数和传输系数:

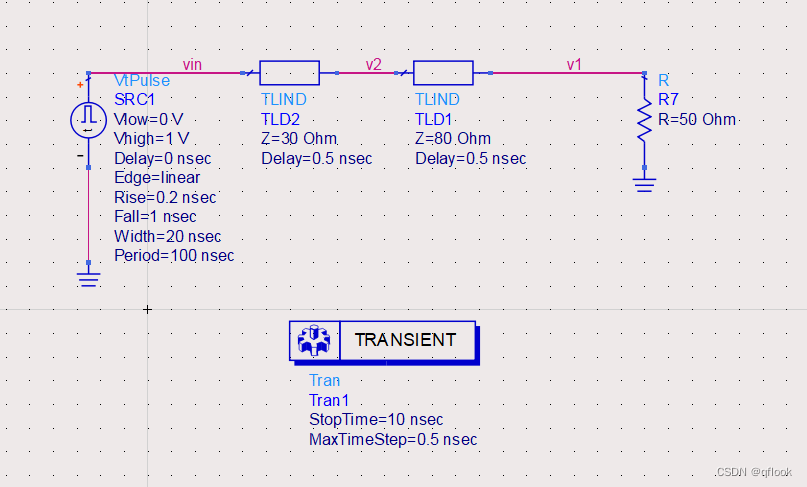

反射对电路影响是什么呢,用ADS仿真看一下,如下图有两段阻抗不一致的理想导线,分别监控输出V1和不联连续点V2处的电压波形:

仿真结果如下:

实际上手算也可以大概计算,例如V2第一个高峰,应该是1+(80-30)/(80+30)*1≈1.45V;V1的第一个高峰是1.45+(50-80)/(50+80)*1.45≈1.1V;

实际上手算也可以大概计算,例如V2第一个高峰,应该是1+(80-30)/(80+30)*1≈1.45V;V1的第一个高峰是1.45+(50-80)/(50+80)*1.45≈1.1V;

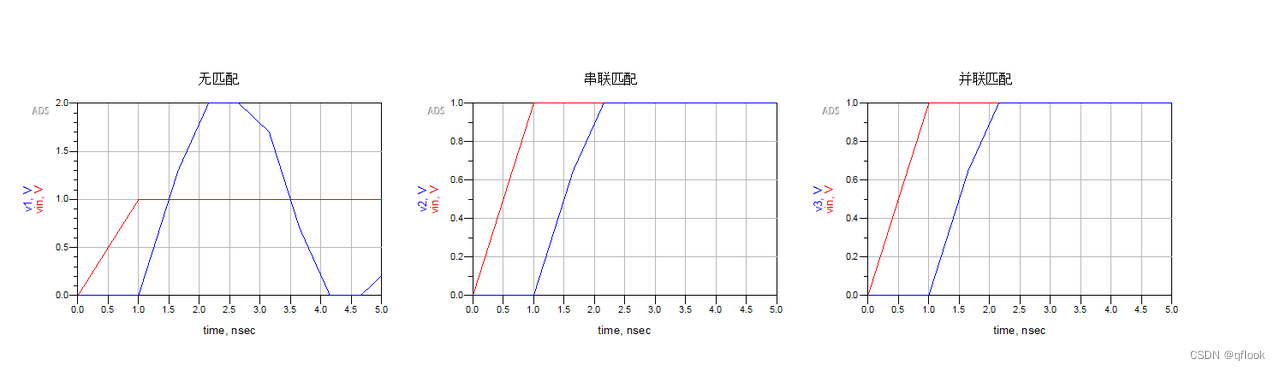

还有一种特殊但常见的情况是信号直连点对点传输,一般情况下是RX阻抗特别大(MΩ级别,仿真设为开路),如没有匹配和带匹配的差别有多大呢?第一个系统是无匹配的情况,第2个系统是源端串联匹配,第三个系统是重点并联匹配:

仿真结果如下:

仿真结果如下:

从仿真结果可以看出,如果没有匹配的话会在RX端产生全反射,也就是2倍输入的电压高峰;匹配的话常见有两种:源端串联匹配和终端并联匹配,从仿真结果来看都可以实现RX接收波形无畸变,一般来说低速总线(例如I2C、TDM、RGMII等)常用串联的方式,高速总线(例如USB、PCIE等)常用并联匹配。两种匹配方式各有优缺点(功耗、信号上升时间等影响),本文暂不展开,有兴趣的可以查阅相关资料。

从仿真结果可以看出,如果没有匹配的话会在RX端产生全反射,也就是2倍输入的电压高峰;匹配的话常见有两种:源端串联匹配和终端并联匹配,从仿真结果来看都可以实现RX接收波形无畸变,一般来说低速总线(例如I2C、TDM、RGMII等)常用串联的方式,高速总线(例如USB、PCIE等)常用并联匹配。两种匹配方式各有优缺点(功耗、信号上升时间等影响),本文暂不展开,有兴趣的可以查阅相关资料。

还有一种常见传输线中间容性负载的影响及其改善方案,第一个系统是无匹配,第2个系统是增加电感(电感大小根据阻抗RLGC模型计算):

仿真结果如下:

仿真结果如下:

从仿真结果来看,无匹配的情况下过冲10%左右,匹配后基本没有了,改善很明显。另外这种匹配建议如上图,把计算出的电感平均分两份,在电容两侧各放一个效果较好。在实际电路中,过孔或者TVS器件等一般都会产生容性负载。

从仿真结果来看,无匹配的情况下过冲10%左右,匹配后基本没有了,改善很明显。另外这种匹配建议如上图,把计算出的电感平均分两份,在电容两侧各放一个效果较好。在实际电路中,过孔或者TVS器件等一般都会产生容性负载。

1819

1819

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?