AXI总线

1 简介

ARM公司1995年推出自己的总线-高级微处理器总线架构(Advanced Microcontroller Bus Architecture,简称ARBA)。它独立于处理器和制造工艺技术,增强了各种应用中的外设和系统宏单元的可重用性,非常适合于现代大规模集成电路设计自动化的要求。AMBA3.0中新增加了一种总线——AXI(Advanced eXtensible Interface)。它是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持显著传输访问和乱序访问,并更加容易就行时序收敛。AXI 是AMBA 中一个新的高性能协议。

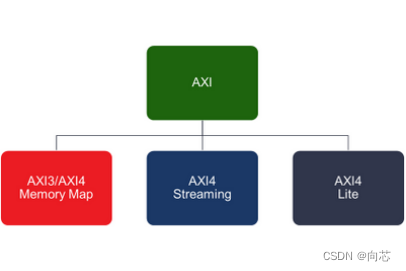

2 AXI总线分类

AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允许最大256轮的数据突发传输;

AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元。

AXI4-Stream:(For high-speed streaming data.)面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。

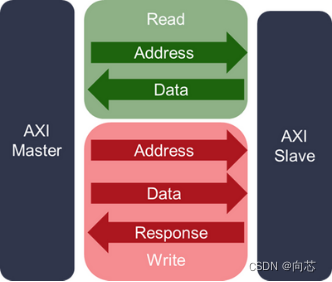

3 AXI 读写通道

AXI 协议定义了 5 条通道:

其中 2 条用于读取传输事务

读地址、读数据

另 3 条用于写入传输事务

写地址、写数据、写响应

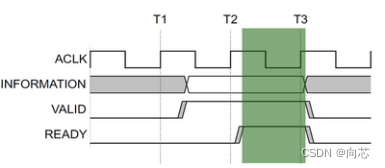

任一通道上发射的每一条数据都称为一次传输 (transfer)。当 VALID 和 READY 信号均处于高位并且时钟存在上升沿时,就会发生传输。例如,在下图中,在 T3 处正在发生传输:

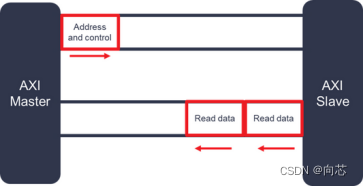

4 AXI 读取传输事务

AXI 读传输事务需要在 2 条读取通道上发生多次传输。

- 首先,地址读通道 (Address Read Channel) 从主接口 (Master) 发送到从接口 (Slave),以便设置地址和部分控制信号。

- 然后,此地址的数据通过读数据通道 (Read data channel) 从从接口发射到主接口。

请注意,根据下图所示,每个地址中可发生多次数据传输。此类型的传输事务称为突发 (burst)。

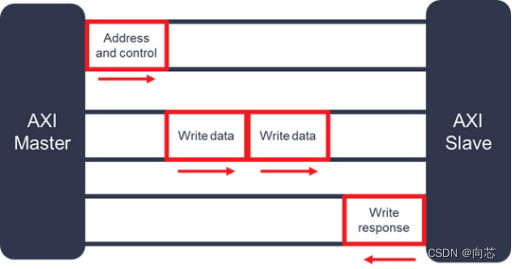

5 AXI 写入传输事务

AXI 写入传输事务需要在 3 条读取通道上存在多次传输。

- 首先,写地址通道 (Address Write Channel) 从主接口发送到从接口,以便设置地址和部分控制信号。

- 然后,此地址的数据通过写数据通道 (Write data channel) 从主接口发射到从接口。

- 最后,写入响应通过写响应通道 (Write Response Channel) 从从接口发送到主接口,以指示传输是否成功。

写响应通道 (Write Response Channel) 上可能的响应值包括:

- OKAY (0b00):正常访问成功。表示已成功完成正常访问

- EXOKAY (0b01):专属访问成功。

- SLVERR (0b10):从接口错误。已成功访问从接口,但从接口希望向发端主接口返回错误条件(例如,数据读取无效)。

- DECERR (0b11):解码器错误。通常由互连组件生成,用于指示传输事务地址处没有任何从接口

注:读取传输事务同样包含响应值,但此响应通过读响应通道 (Read Response Channel) 来发射

6 AXI4 接口要求

在 AXI4 规格中记录了部分要求。

最值得注意的是:

- 当 VALID (AxVALID/xVALID) 信号断言有效时,它必须保持处于已断言有效状态直至从接口断言 AxREADY/xREADY 有效后出现上升时钟沿为止。

- 发送信息的 AXI 接口的 VALID 信号不得从属于接收该信息的 AXI 接口的 READY 信号。但是,READY 信号的状态可从属于 VALID 信号

- 写响应必须始终位于所属的写入传输事务中最后一次写入传输之后

- 读数据必须始终位于数据相关的地址之后

- 从接口必须等待断言 ARVALID 和 ARREADY 有效后,才能断言 RVALID 有效以指示该有效数据可用

4098

4098

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?