4.16.1 CRC校验

DDR4支持写操作进行CRC校验(MR2A12),但是不支持读操作进行CRC校验。CRC校验的多项式为

x^8 + x^2 + x + 1

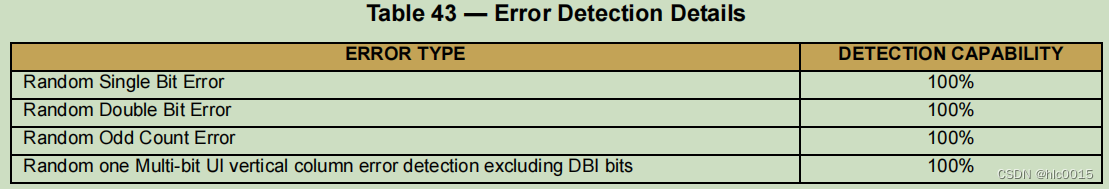

表43展示了CRC校验功能可以检测出的错误细节,其中最后一个不知如何翻译。

CRC的输出为8bit位宽,其具体算法详见手册。

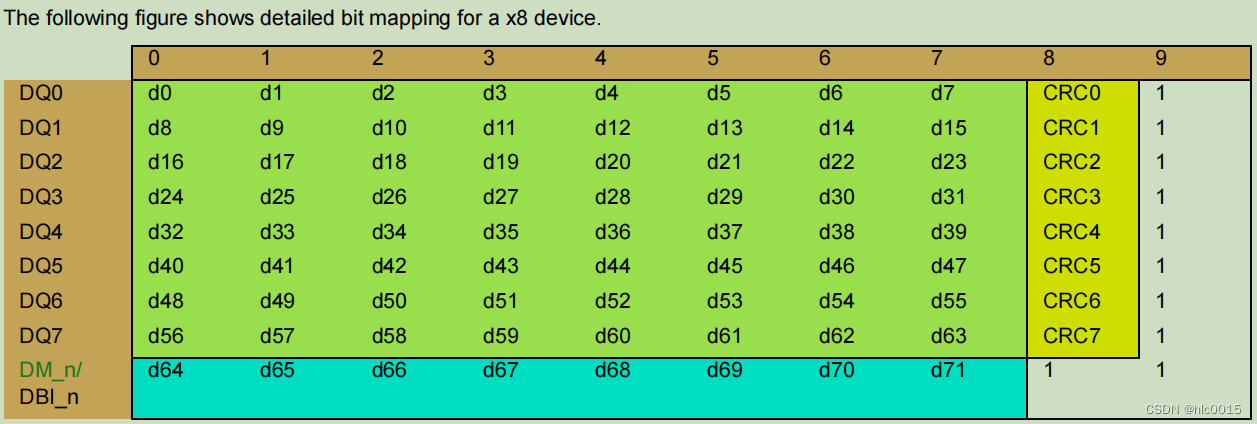

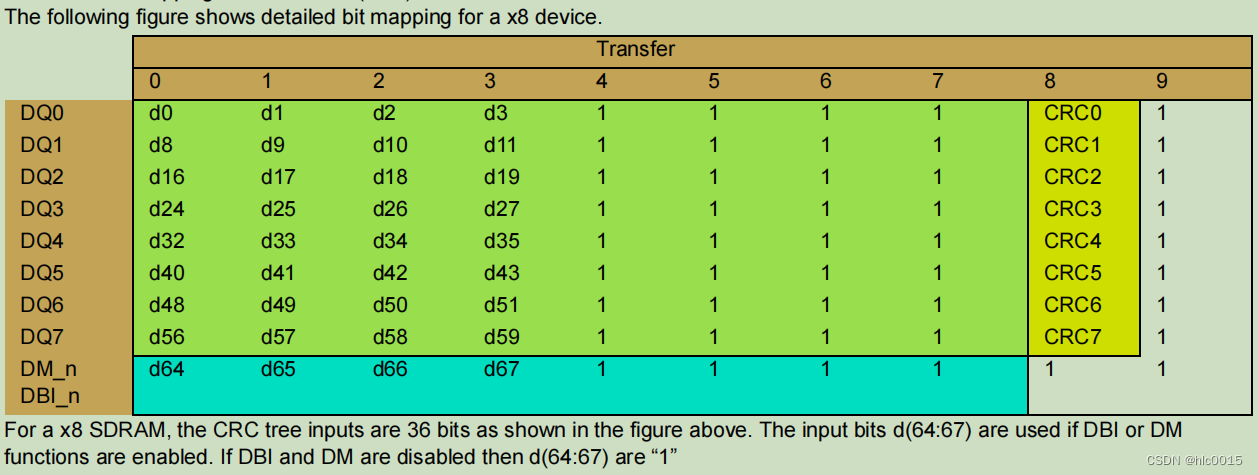

4.16.2 x8器件的CRC排列方式

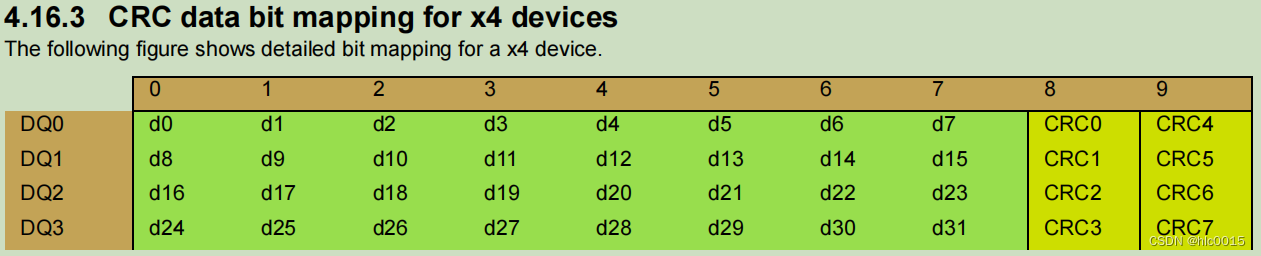

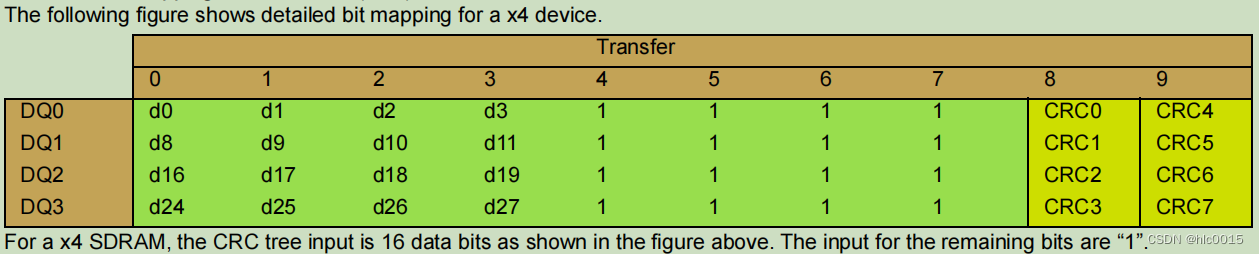

4.16.3 x4器件的CRC排列方式

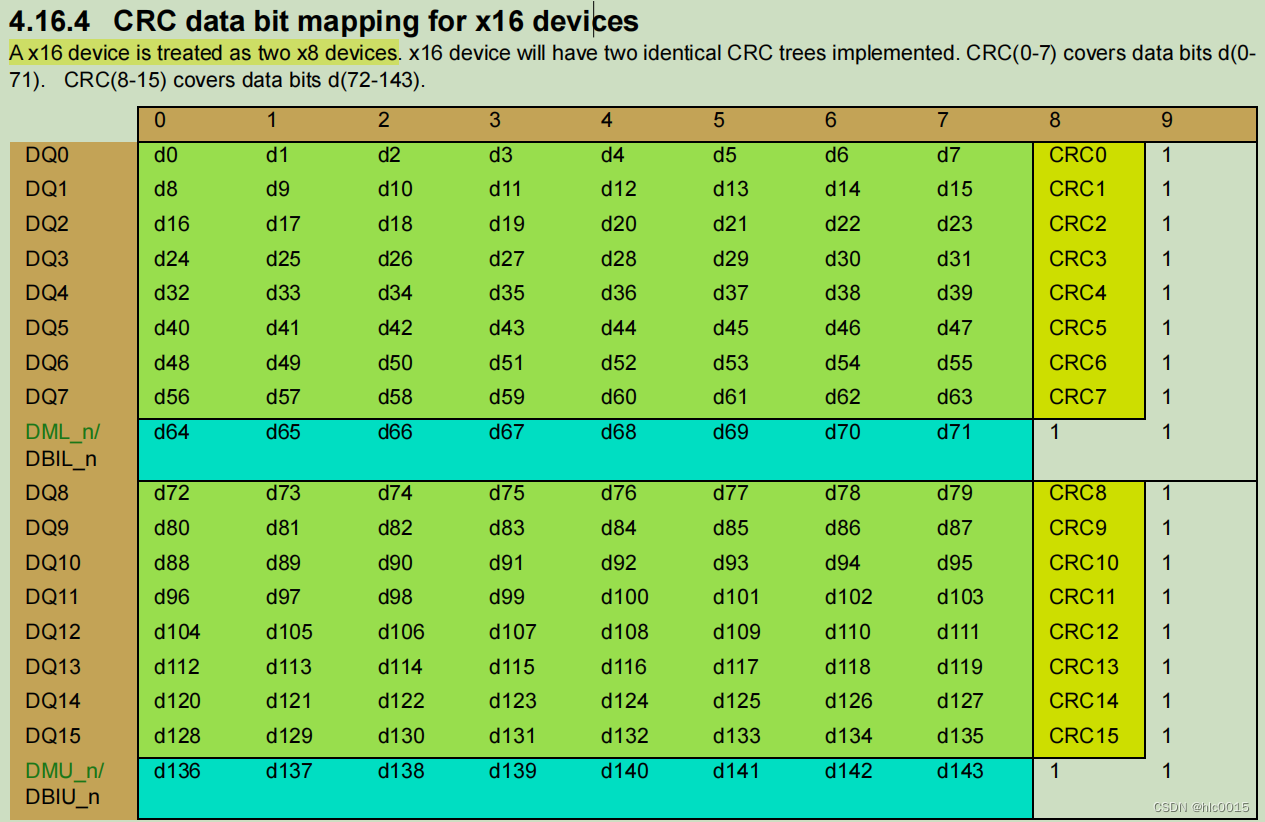

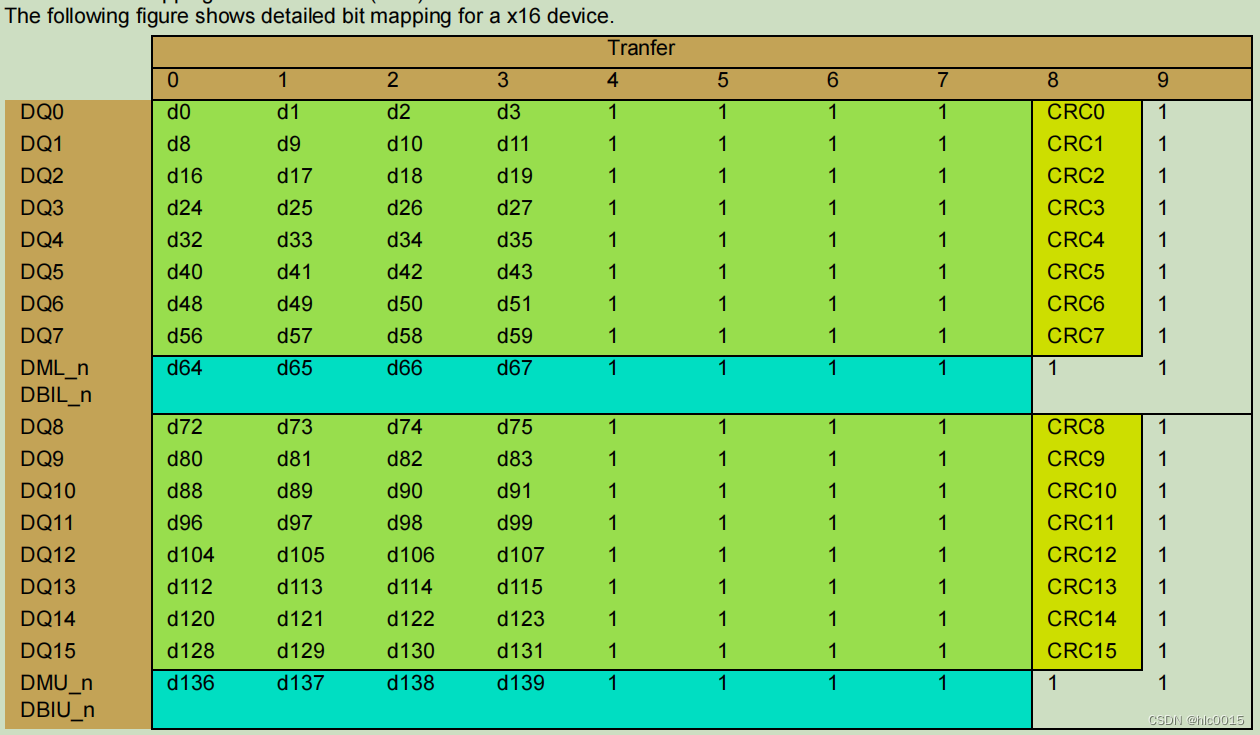

4.16.4 x16器件的CRC排列方式

4.16.5 对上述三点的总述

对于x8器件,如果CRC使能,内存控制器必须在第9个transfer处发送全1,如果DBI使能,则需要在DBI_n的第8和第9个transfer处发送1(must send 1’s in transfer 8 and transfer 9 of the DBI_n lane if DBI function is enabled)。

对于x16器件,其被当做两个x8器件。功能和x8一样。

当接收了72bit数据后(D[71:0]),DRAM通过校验码和接收到的数据进行比对,如果不匹配则会拉高ALERT_n信号。

x8器件有72bit的输入,高8bit用于DBI/DM(如果DBI或DM使能了)。需要注意的是写DBI和写DM不能同时使能,这一点在DBI/DM/TDQS引脚章节讲过。如果写DBI和DM都不使能,那么72bit输入的高8bit(D[71:64])应该为全1。

x16器件相当于两个x8器件,如果写DBI和DM都不使能,那么高8bit(D[143:136] (对应DBIU/DMU)和D[71:64] (对应DBIL/DML))应该为全1。

x4器件最简单,没有DBI/DM信号,只有32个输入,D[71:32]应该都设置为全1。

在写数据的过程中,即使DRAM没有完成CRC校验,数据也能全部写入到DRAM core中。如果DRAM core中被写入了错误的数据,内存控制器将会重新发送这笔传输,并覆盖掉之前的有误的数据。当然,内存控制器需要保证数据的一致性,也就是说当写入数据A0,传输过程中由于一些干扰出现了错误,DRAM core存储的数据为A1,再次传输时应该还是发送A0,而不是其它数据。

4.16.6 CRC出错时的处理

CRC Error机制共享相同的Alert_n信号(Alert_n和Parity信号在同一个pin上),故内存控制器无法直接区分CRC错误和CMD/ADDR/Parity错误,除非读取MR寄存器,具体来说是MPR寄存器。

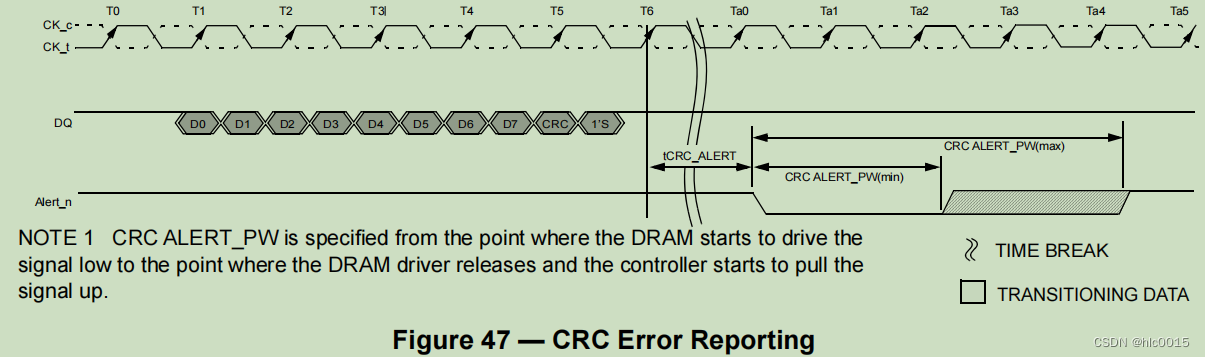

为了尽快恢复CRC错误,CRC错误会发送一个脉冲,该脉冲最小的脉宽为6个时钟周期。以x8为例,当发送完72bit数据后,延迟tCRC_ALERT时间后,Alert_n拉低。如图47所示。

内存控制器看到了错误后,将会重新发送此次写传输。在初始化期间,控制器知道Alter_n的最大延迟,并且控制器能备份其传输(transaction),更甚者,控制器能够将写入的CRC错误与特定的rank和特定的传输(transaction)关联起来。当然,控制器也需要保证能够打开任何page,并保持重新写的操作的一致性(这明显是DRAM标准定制者对控制器做出的要求,一旦控制器不支持使用CRC校验,DRAM颗粒也没办法)。

当出现多个CRC Error时,ALERT_n信号可能形成一个daisy链,即ALERT_n脉冲有可能大于6个周期。

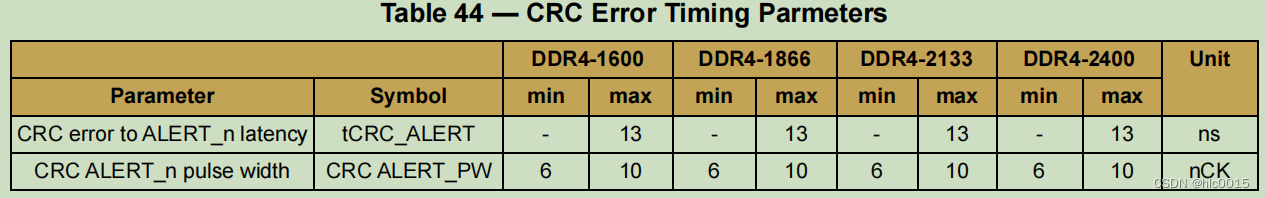

表44阐述了在不同的速率下,CRC Error的时序参数。但是这个明显是没写全的。

4.16.7 对于突发长度为BC4的CRC格式

无论是BL8传输还是BC4传输,当CRC使能后,所有的数据都被限定为10个UI。当CRC开启后,DDR4也支持on the fly的突发长度的改变。

对于x4器件,其数据分布如下:

对于x8器件,其数据分布如下。如果DBI或DM使能,则d(64:67)有效;如果DBI和DM不使能,则令d(64:67)为全1。

对于x16器件,其数据分布如下。如果DBIL或DML使能,则d(64:67)有效;如果DBIL和DML不使能,则令d(64:67)为全1,类似地,DBIU/DMU也一样,其对应d(136:139)。

关于DBI和CRC的说明:

假设DBI开启,在计算CRC校验码之前,数据是不会翻转的;在写入DRAM core时,数据才会根据DBI信号进行相应的翻转。

关于BC4的burst order和CRC说明:(这个说明里面有一个地址bit A2,但查阅手册发现普通命令的A2并无特殊含义,不知是指哪个MR的A2,于是这里暂不往下写了)

对于x8器件,BC4的传输中,由于A2取值的不同,其CRC的值也不同。

4.16.8 同时开启DM和CRC功能

当同时开启DM和CRC校验功能,在将数据写入DRAM阵列中,DRAM会先计算CRC校验值。如果有CRC Error,则DRAM将会阻止此次写操作并丢弃数据。对于x16器件,如果DRAM检查到CRC有误,那么DRAM将会mask所有的DQ数据(或mask一半的DQ数据,取决于制造商的规定)。如果仅仅是mask一半的DQ数据,则根据出错的CRC来mask对应的DQ(高8位的CRC出错则mask DQ0-7,低8位的CRC出错则mask DQ8-15)。

4.16.9 同时进行MPR写操作,PDA以及CRC功能

以下同时的操作不被允许:

- MPR写操作和CRC不能同时开启。

- PDA和CRC不能同时开启。

1818

1818

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?