文章目录

4.19 DDR4关键时序

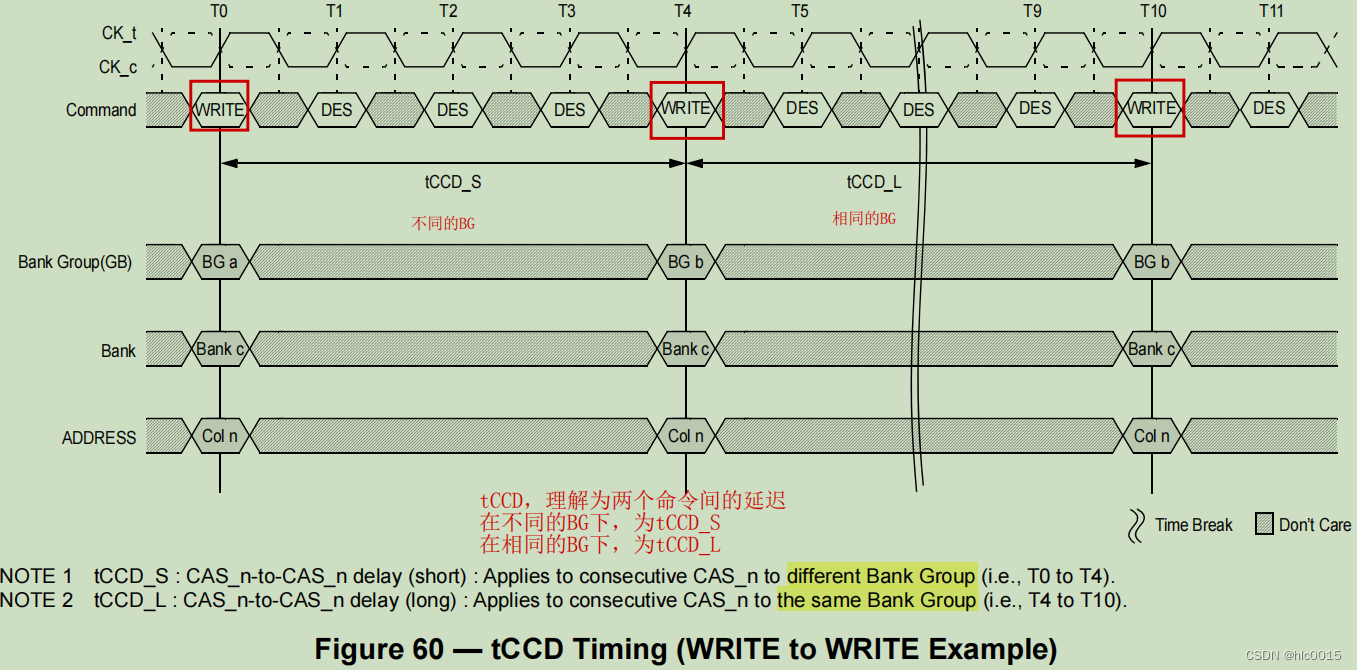

俩write命令间的间隔如下,由于是写命令,需要写到具体的位置当中,故其地址为列地址(在写命令发送之前应该发送ACT命令用于激活行地址)。

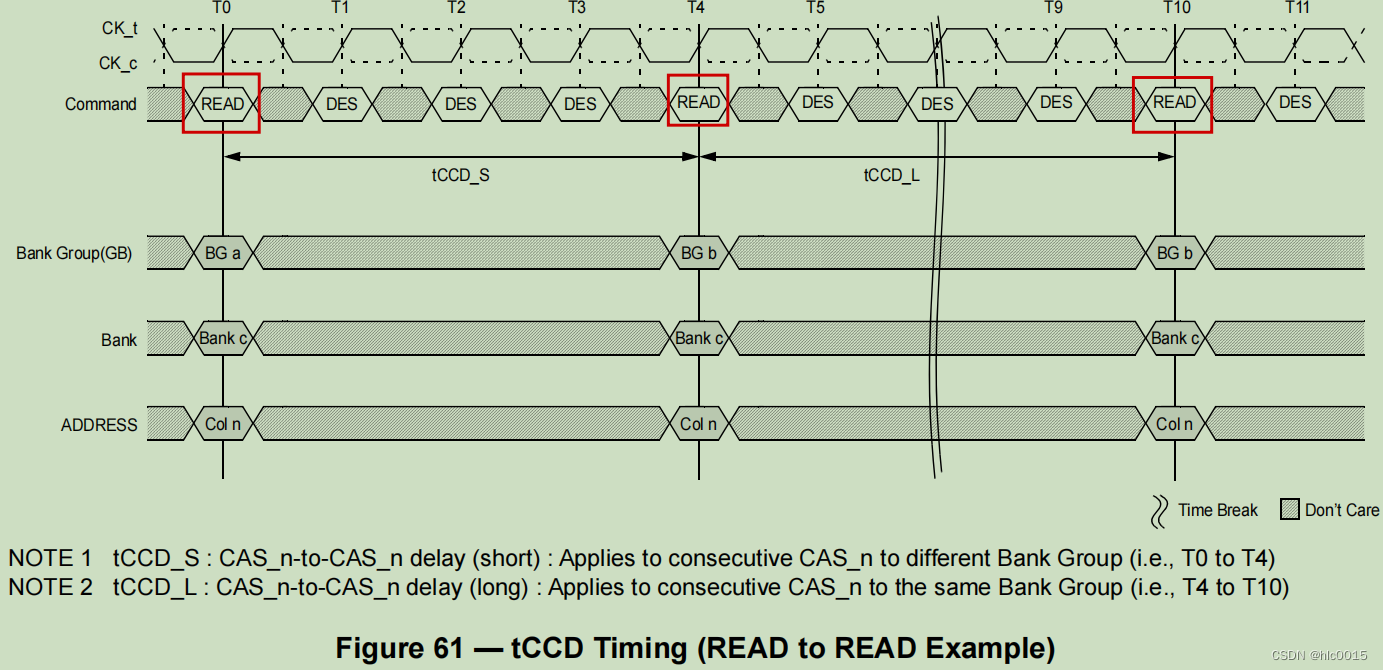

俩read命令间的间隔如下,由于是读命令,需要从具体的位置读出数据,故其地址为列地址。

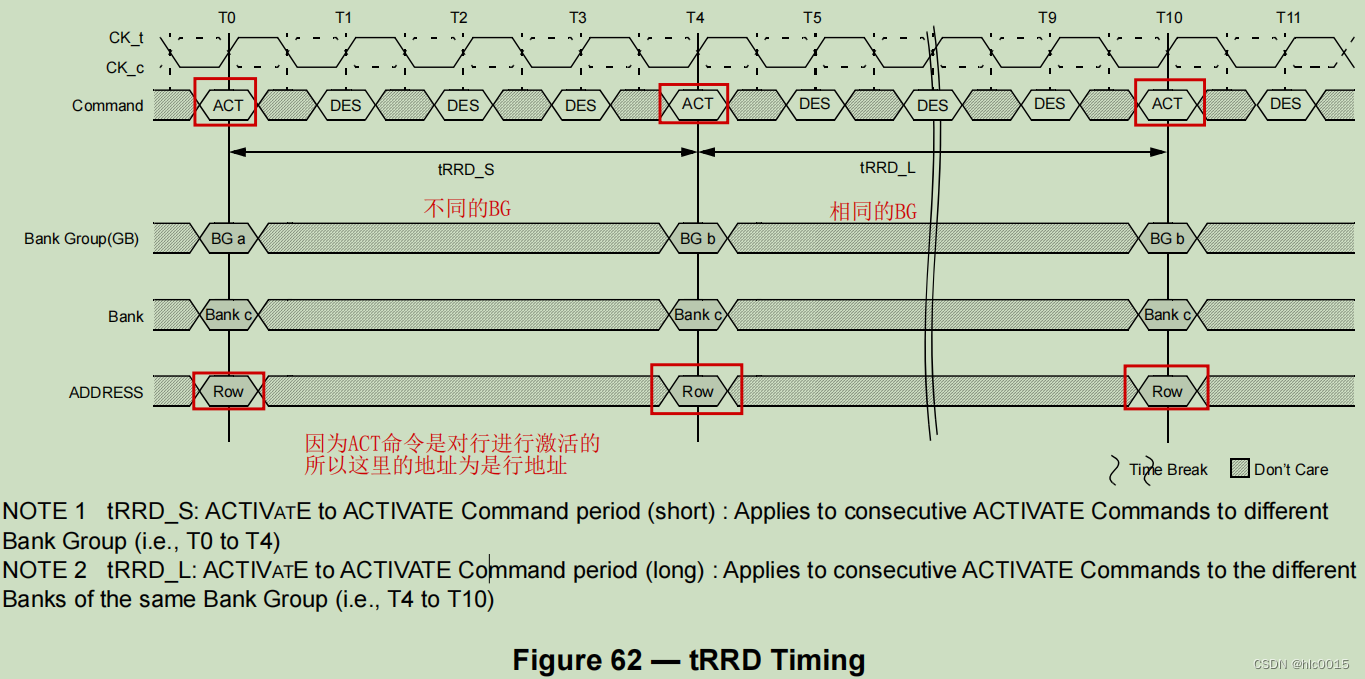

下图为相同BG和不同BG间的ACT命令时序。

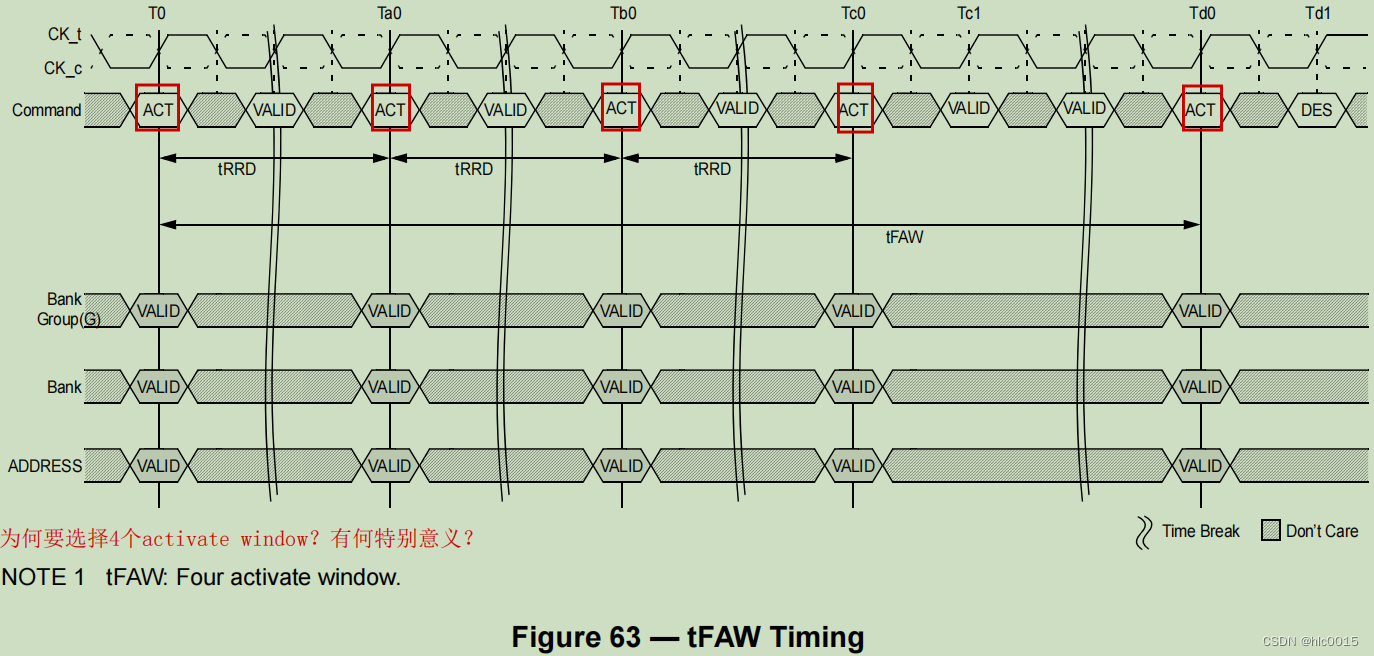

下图为4个ACT命令后,发送第五个ACT命令的时序参数tFAW,其中为何要选择四个ACT为一组?这样做有何意义?

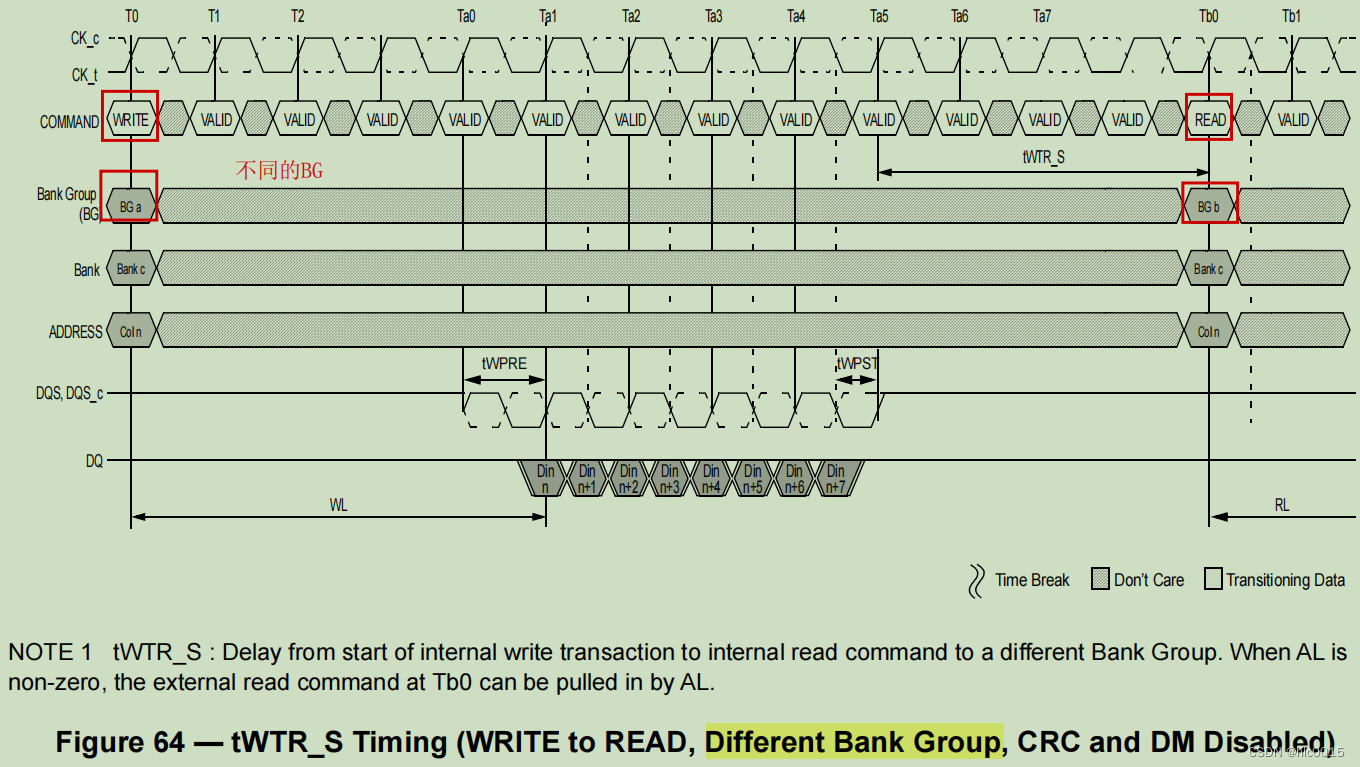

下图为从写到读的时序图,且俩bank group为不同的bank group,CRC和DM都已关闭。

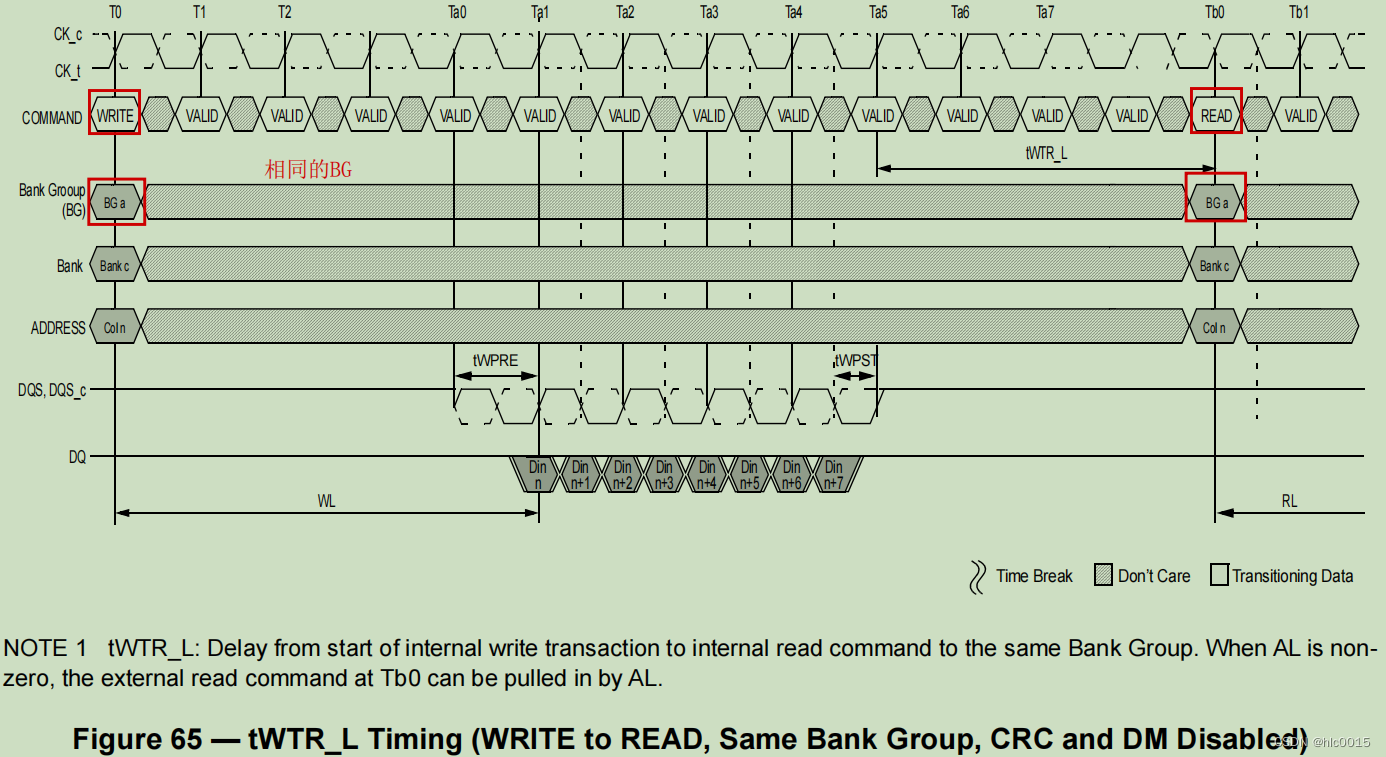

下图为从写到读的时序图,BG相同,CRC和DM都已关闭。

4.20可编程的前导时钟

前导时钟(简称前导)分为写前导和读前导,其含义是通知对方(一个系统或一个组件)有数据要来了,你要准备好接收数据。在网络通信中,例如以太网协议中的UDP协议,其报头(header)就相当于前导。

站在DDR4的角度来说,WR命令为从内存控制器写入DDR4中,内存控制器需控制DQS信号在真正的数据有效前拉高一到两个时钟周期。RD命令为从DDR4中发送到内存控制器,由DDR4控制DQS信号提前拉高一到两个时钟周期。

4.20.1 写前导

DDR4提供可编程的写前导时钟,通过MR4的A12bit来选择写前导时钟是持续一个tCK周期还是两个tCK周期。

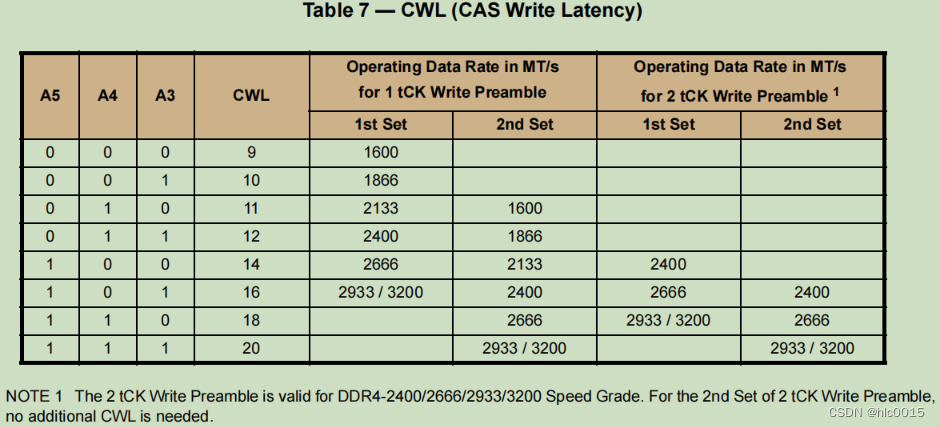

表7展示了MR2的CWL。

当处于写前导时钟为2tCK模式下,第一次设置的CWL(1st Set)需要再此基础上加2个nCK时钟周期,第二次设置的CWL(2nd)并不需要再此基础上进行增加,在speed bin表格中(第十章),tWRT必须增加一个时钟周期。WR必须被设置为1或2个时钟周期,具体WR的设置取决于具体的设置,但是肯定要比每个speed bin中规定的值要大。(WR这句话没理解,这里的WR指的是写命令吗?)

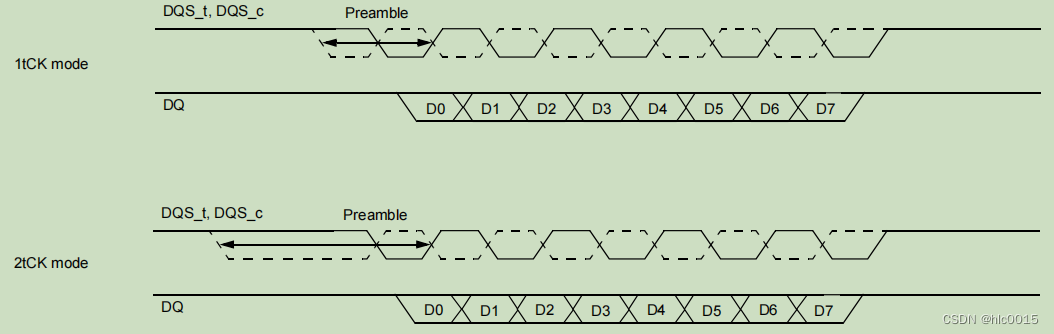

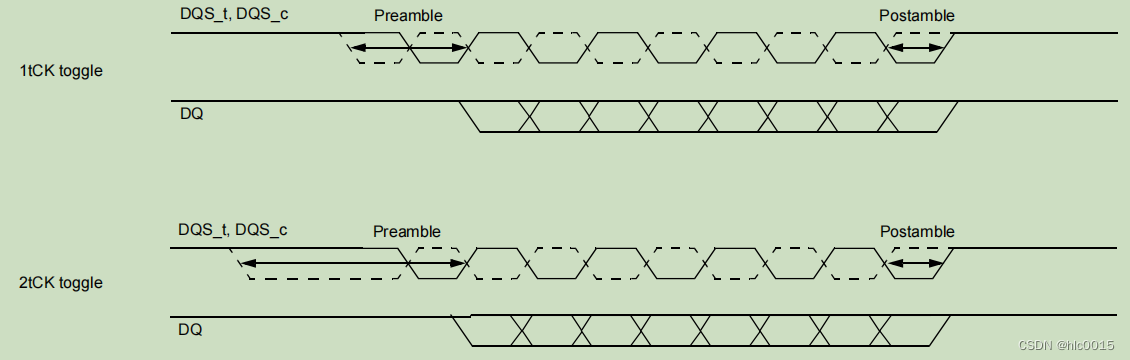

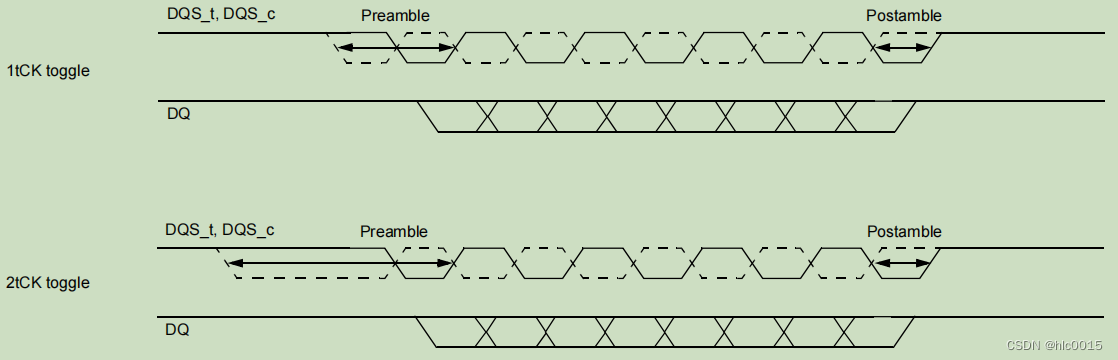

下图展示了写前导时钟的1tCK模式和2tCK模式,可见数据有效的时刻两者保持对齐,仅DQS信号开始摆动的位置不同。

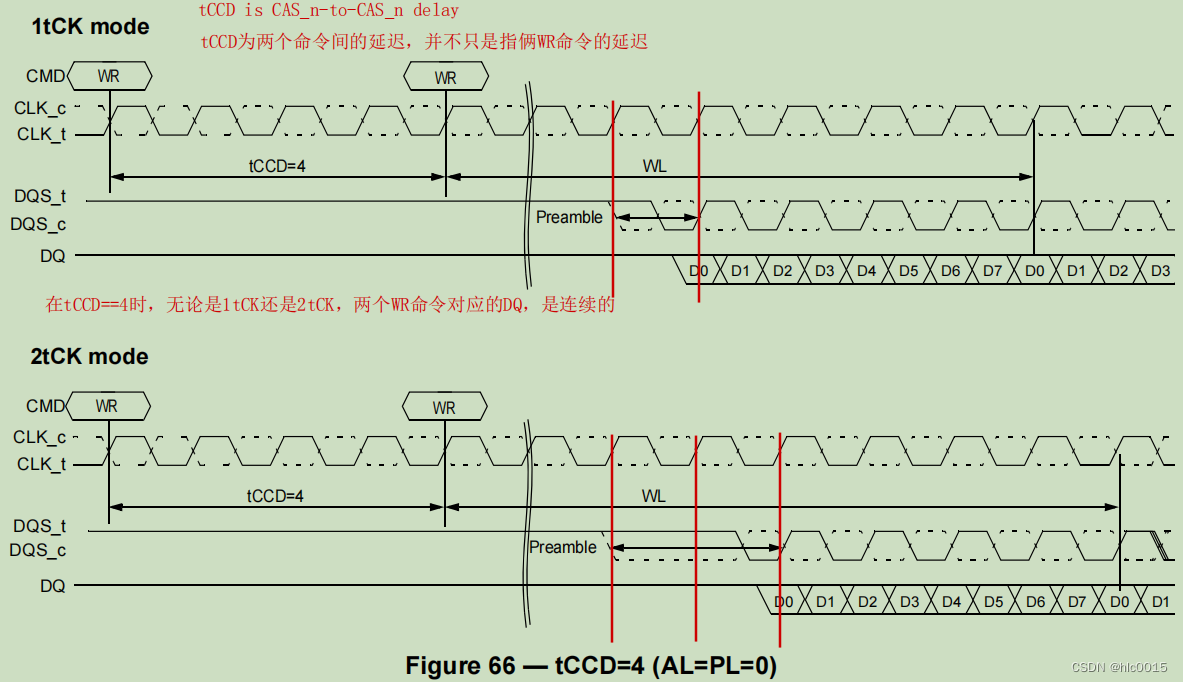

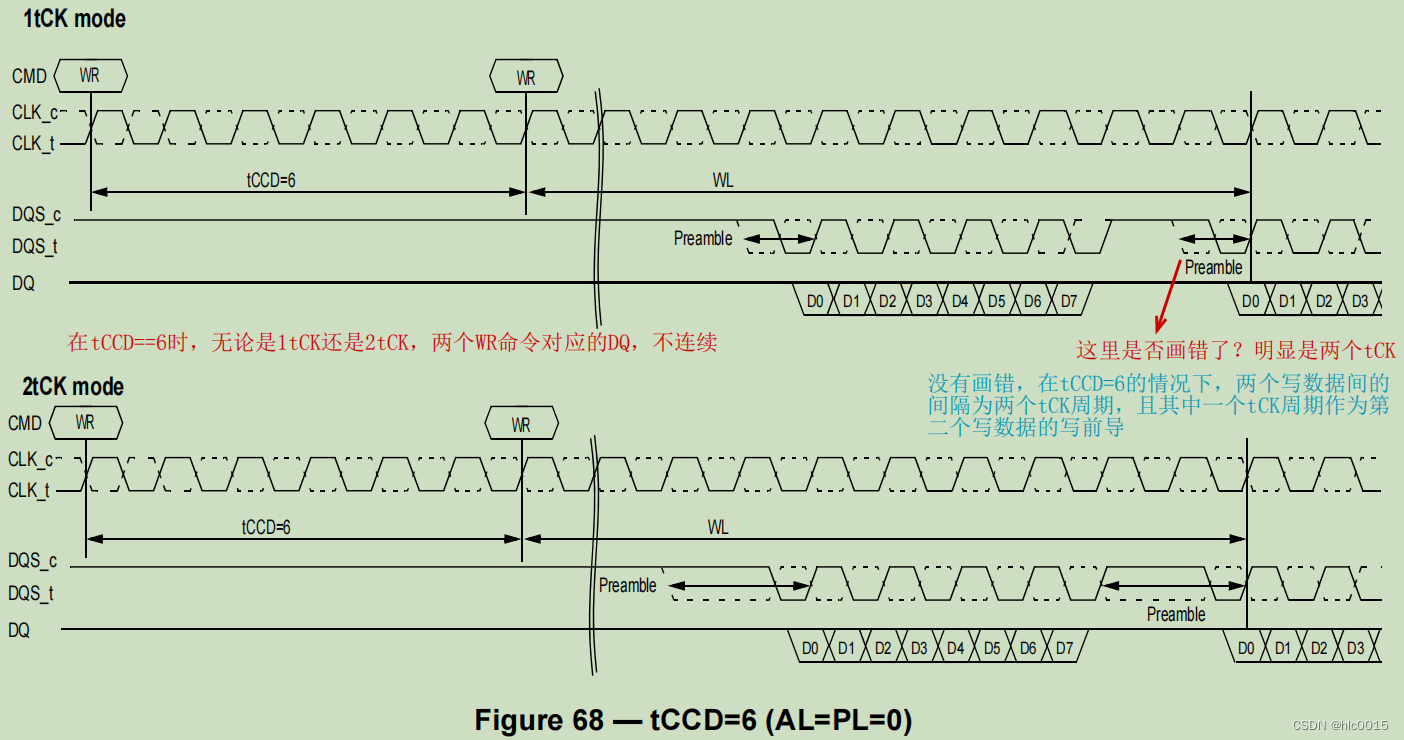

图66,图67,图68展示了写前导为1tCK和2tCK场景下的时序图,三者的tCCD时序分别为4,5,6个tCK周期。在tCCD为5nCK周期情况下,不支持2tCK的写前导模式,因为tCCD=5tCK的情况下,第二个WR命令所对应的写前导最多只能为一个tCK周期。

4.20.2 读前导

同样地,DDR4提供可编程的读前导时钟,通过MR4的A11bit来选择读前导时钟是持续一个tCK还是两个tCK周期。其示意图如下图所示。

4.20.3 读前导的训练

当DRAM处于MPR模式时,才能通过使能MR4的A10bit来进行读前导的训练。之前有单独一章节描述了write leveling,对应地,这里的读前导训练可以用于read leveling(处理DQS和CK边沿的关系)。

在读前导训练的时候,在’读’过程中或启动’读’过程中,不允许发送其它任何命令。这句话的翻译还需对照原文细看,还需斟酌。

下图展示了tSDO的时序以及DQS的变化。

4.21 后导

与前导相对应的是后导,前导可以理解成通信中的报头,后导则理解成通信中的报尾。DDR4仅支持固定的读写后导。

4.21.1 读后导

如下图所示,在读前导为1tCK或2tCK周期的情况下,读后导为0.5个tCK周期。

4.21.2 写后导

如下图所示,在写前导为1tCK或2tCK周期的情况下,写后导为0.5个tCK周期。

这俩图一模一样

4.22 ACTIVATE命令

ACTIVATE命令用于打开/激活某个特定bank中的行。在发送precharge命令之前或者发送precharge All命令之前,激活(或者说打开的)的行会一直保持激活/打开。当想访问同一个bank中的另一行,需要将当前行关掉(precharge),再去打开另一行。

4.23 Precharge命令(预充电命令)

Precharge命令可以理解为关闭打开的行的命令。Precharge的时序参数为tRP,但是注意,有两个命令自带precharge,分别是RDA和WRA(读后自动precharge和写后自动precharge),这俩命令中的precharge之后跟随的时间参数并不是tRP。一旦一个bank被precharge了,则说明该bank处于idle状态,并且在发送读写命令前必须先发送激活命令来激活该bank以及对应的row。当然,当某个bank的所有的row都关闭了,也可以对该bank发送precharge命令,这种情况下,precharge的周期取决于该bank中的上一个precharge命令。

如果在发送读写命令时,A10拉高,则读写命令后将跟随一个auto-precharge。这个特点可以允许在突发读周期内,将precharge操作部分地或完全的隐藏起来,从而在随机读取时提升系统的性能。RAS锁定电路内部延迟precharge操作,直到DRAM阵列恢复操作已经完成(通俗来讲就是满足时序tRAS后),以便auto precharge命令可以跟随任何读操作而发出。在写命令发送时,auto precharge命令也可以实现。写操作写完最后一个数据后,auto precharge命令才会执行。在对某bank发送auto precharge过后(也就是hidden precharge,被隐藏的precharge)的tRP时间后,对应的bank才能被使用(用来发送row ACTIVATE命令)。

5390

5390

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?