背景

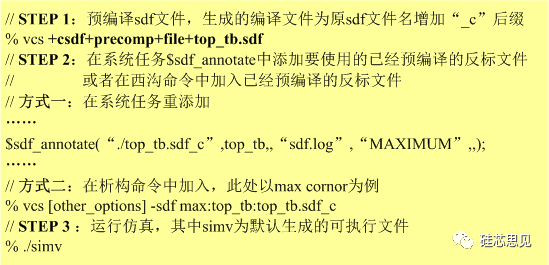

如果我们的设计代码进行了修改,但是sdf文件并没有修改,此时如果编译完后,在析构的时候还要再进行一次sdf文件的解析反标,将会比较耗费时间,为此,一般的EDA工具都提供了另外一种反标方式,即对sdf文件进行预编译,如果sdf文件并没有修改,仅设计文件进行修改,此时就可以采用sdf预编译方式,具体操作步骤如下示例。

【示例】

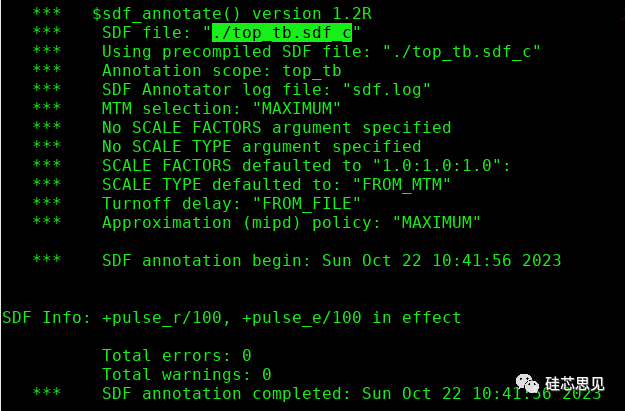

【反标信息一】在系统任务$sdf_annotate中添加要使用的已经预编译的反标文件

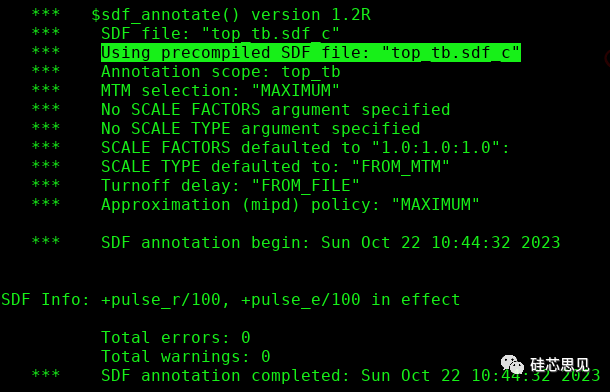

【反标信息二】在析构命令中加入已经预编译的反标文件,大家可以仔细观察下两者差异。

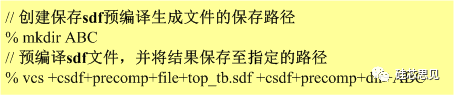

另外,在VCSMX中,还可以指定sdf预编译生成文件的保存路径,指定方式如下:

感谢大佬知识分享~~~

致敬!

451

451

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?