文章参考:差分布线 - 骏骏 - 博客园 (cnblogs.com)

USB2.0接口差分信号线设计

差分线由两根平行绘制在PCB板表层(顶层或底层)发生边缘耦合效应的微带线(Microstrip)组成的,其阻抗由两根微带线的阻抗及其和决定,而微带线的阻抗(Zo)由微带线线宽(W)、微带线走线的铜皮厚度(T)、微带线到最近参考平面的距离(H)以及PCB板材料的介电常数(Er)决定,其计算公式为:Zo={87/sqrt(Er 1.41)]}ln[5.98H/(0.8W T)]。影响差分线阻抗的主要参数为微带线阻抗和两根微带线的线间距(S)。当两根微带线的线间距增加时,差分线的耦合效应减弱,差分阻抗增大;线间距减少时,差分线的耦合效应增强,差分阻抗减小。差分线阻抗的计算公式为:Zdiff=2Zo(1-0.48exp(-0.96S/H))。微带线和差分线的计算公式在0.1<W/H<2.0以及0.2<S/H<3.0的情况下成立。为了获得比较理想的信号质量和传输特性,高速USB2.0设备要求PCB板的叠层数至少为4层,可以选择的叠层方案为:顶层(信号层)、地层、电源层和底层(信号层)。不推荐在中间层走信号线,以免分割地层和电源层的完整性。普通PCB板的板厚为1.6 mm,信号层上的差分线到最近参考平面的距离H大约为11mil,走线的铜皮厚度T大约为O.65mil,填充材料一般为FR-4,介电常数Er为4.2。在H、T和Er已确定的条件下,由差分线2D阻抗模型以及微带线和差分线阻抗计算公式可以得到合适的线宽W和线间距S。当W=16mil,S=7mil时,Zdiff=87Ω。但通过上述公式来推导合适的走线尺寸的计算过程比较复杂,借助PCB阻抗控制设计软件Polar可以很方便的得到合适的结果,由Polar可以得到当W=11mil,S=5mil时,Zdiff=92.2Ω。

在差分线对中,正负两边都必须始终在相同的环境下沿着传输路径传送。正负两边必须紧靠在一起,以使正负信号经由这些信号上相应点的电磁场而彼此耦合。差分线对是对称的,因此它们的环境也必须对称。

USB布线注意事项

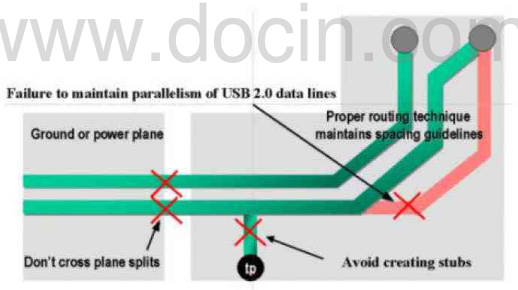

(1)如下图所示,USB信号线不能跨越多个参考地(或电源)平面。

(2)如下图所示,DP/DM差分信号线尽可能并行走线,走线应尽量短,等长等距等线宽,尽量少换层。

(3)如下图所示,。DP/DM信号线上应避免产生分支,如果分支不可避免,分支长度不能超过200mils。

(4)USB信号线必须在参考平面的相邻层走线,而且尽可能少走孔或者拐弯,这样会导致阻抗不连续,产生不必要的反射,如果存在过孔,过孔前后的走线必须参考同一信号平面;

(5)在布线需要90度拐弯的地方,用两个45度来代替,这样可以减少阻抗不匹配,较少反射。

(6)不要在晶体(无源),晶振(有源),时钟器件(例如外置PLL,时钟Buffer等),或磁性器件(如电感、磁珠等)下面走线,并且尽可能远离以上器件。

(7)为了避免串扰,高速时钟或者周期信号不要与DP/DM并行走线,建议DP/DM离高速时钟信号线的距离控制在50mils以上。

(8)同样是为了避免串扰,DP/DM与其他并行信号线的距离尽可能控制在20mils以上。

(9)DP/DM信号线离参考平面边沿的距离尽可能服从20*h规则;即信号线离参考平面边沿的距离不能小于(信号线与参考平面之间的)高度的20倍。例如信号线离参考平面的高度为4.5mils,那么信号线里参考平面的边沿不能小于90mils。

(10)尽可能将DP/DM的差分阻抗值控制在90欧姆,建议保持线距和线宽一致,并且都不小于8mils。

USB2.0总线接口端电源线和地线设计

USB接口有5个端点,分别为:USB电源(VBUS)、D-、D 、信号地(GND)和保护地(SHIELD)。上面已经介绍过如何设计D 、D-差分信号了,正确设计USB总线电源、信号地和保护地对USB系统的正常工作也是同样重要的。

USB电源线电压为5 V,提供的最大电流为500mA,应将电源线布置在靠近电源层的信号层上,而不是布置在与USB差分线所在的相同层上,线宽应在30 mil以上,以减少它对差分信号线的干扰。现在很多厂家的USB从控制芯片工作电压为3.3 V,当其工作在总线供电模式时,需要3.3~5 V的电源转换芯片,电源转换芯片的输出端应尽量靠近USB芯片的电压输入端,并且电源转换芯片的输入和输出端都应加大容量电容并联小容量电容进行滤波。当USB从控制芯片工作在自供电的模式时,USB电源线可以串联一个大电阻接到地。

USB接口的信号地应与PCB板上的信号地接触良好,保护地可以放置在PCB板的任何一层上,它和信号地分割开,两个地之间可以用一个大电阻并联一个耐压值较高的电容,

保护地和信号地之间的间距不应小于25mil,以减少两个地之间的边缘耦合作用。保护地不要大面积覆铜,一根100mli宽度的铜箔线就已能满足保护地的功能需要了。

在绘制USB电源线、信号地和保护地时,应注意以下几点:

①USB插座的1、2、3、4脚应在信号地的包围范围内,而不是在保护地的包围范围内。

②USB差分信号线和其他信号线在走线的时候不应与保护地层出现交叠。

③电源层和信号地层在覆铜的时候要注意不应与保护地层出现交叠。

④电源层要比信号地层内缩20D,D为电源层与信号地层之间的距离。

⑤如果差分线所在层的信号地需要大面积覆铜,注意信号地与差分线之间要保证35 mil以上的间距,以免覆铜后降低差分线的阻抗。

⑥在其他信号层可以放置一些具有信号地属性的过孔,增加信号地的连接性,缩短信号电流回流路径。

⑦在USB总线的电源线和PCB板的电源线上,可以加磁珠增加电源的抗干扰能力。

差分信号布线注意事项:

①在元件布局时,应将USB2.0芯片放置在离地层最近的信号层,并尽量靠近USB插座,缩短差分线走线距离。

②差分线上不应加磁珠或者电容等滤波措施,否则会严重影响差分线的阻抗。

③如果USB2.0接口芯片需串联端电阻或者D 线接上拉电阻时.务必将这些电阻尽可能的靠近芯片放置。

④将USB2.0差分信号线布在离地层最近的信号层。

⑤在绘制PCB板上其他信号线之前,应完成USB2.0差分线和其他差分线的布线。

⑥保持USB2.0差分线下端地层完整性,如果分割差分线下端的地层,会造成差分线阻抗的不连续性,并会增加外部噪声对差分线的影响。

⑦在USB2.0差分线的布线过程中,应避免在差分线上放置过孔(via),过孔会造成差分线阻抗失调。如果必须要通过放置过孔才能完成差分线的布线,那么应尽量使用小尺寸的过孔,并保持USB2.0差分线在一个信号层上。

⑧保证差分线的线间距在走线过程中的一致性,使用Cadence绘图时可以用shove保证,但在使用Protel绘图时要特别注意。如果在走线过程中差分线的间距发生改变,会造成差分线阻抗的不连续性。

⑨在绘制差分线的过程中,使用45°弯角或圆弧弯角来代替90°弯角,并尽量在差分线周围的150 mil范围内不要走其他的信号线,特别是边沿比较陡峭的数字信号线更加要注意其走线不能影响USB差分线。

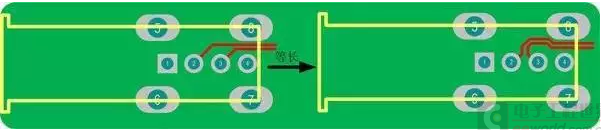

⑩差分线要尽量等长,如果两根线长度相差较大时,可以绘制蛇行线增加短线长度。

图文说明

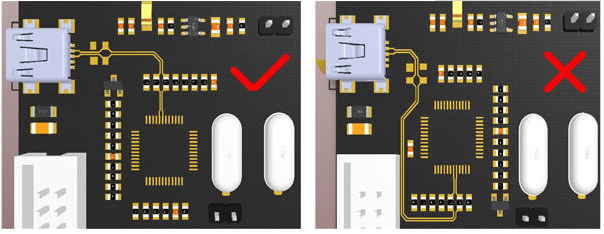

(1) 在元件布局时,尽量使差分线路最短,以缩短差分线走线距离(√为合理的方式,×为不合理方式)

(2)优先绘制差分线,一对差分线上尽量不要超过两对过孔(过孔会增加线路的寄生电感,从而影响线路的信号完整性),且需对称放置(√为合理的方式,×为不合理方式);

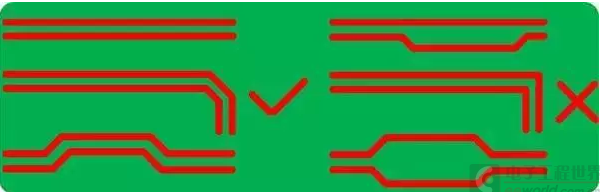

(3)对称平行走线,这样能保证两根线紧耦合,避免90°走线,弧形或45°均是较好的走线方式(√为合理的方式,×为不合理方式);

(4)差分串接阻容,测试点,上下拉电阻的摆放(√为合理的方式,×为不合理方式);

(5) 由于管脚分布、过孔、以及走线空间等因素存在使得差分线长易不匹配,而线长一旦不匹配,时序会发生偏移,还会引入共模干扰,降低信号质量。所以,相应的要对差分对不匹配的情况作出补偿,使其线长匹配,长度差通常控制在5mil以内,补偿原则是哪里出现长度差补偿哪里.

1055

1055

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?