在我们日常的使用中,宏定义一般如下:

`define DUT_TOP tb.dut_top如果需要用到信号的hierarchy,需要借助宏定义,代码会简洁很多,但是直接用下面代码表示

$display("%s", `DUT_TOP);会出现下面编译错误,是因为vcs直接把`DUT_TOP展开了

Error-[XMRE] Cross-module reference resolution error

a.sv, 8

Error found while trying to resolve cross-module reference.

token 'dut'. Originating module 'tb', first module hit 'tb'.

Source info: $display("path = %s", tb.dut);

此时需要将宏定义转义成string类型

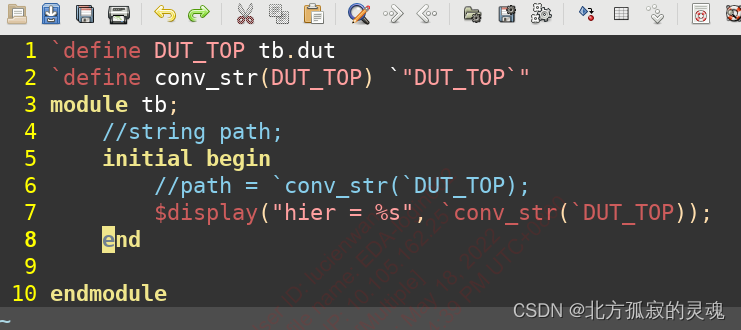

`define DUT_TOP tb.dut

`define conv_str(DUT_TOP) `"DUT_TOP`"这样就可以使用了,具体使用方法如下:

$display("hier = %s", `conv_str(`DUT_TOP));放在结果如下:

Chronologic VCS simulator copyright 1991-2021

Contains Synopsys proprietary information.

Compiler version S-2021.09_Full64; Runtime version S-2021.09_Full64; May 18 16:33 2022

hier = tb.dut

V C S S i m u l a t i o n R e p o r t

Time: 0

CPU Time: 0.200 seconds; Data structure size: 0.0Mb

Wed May 18 16:33:42 2022

详细测试代码如下:

本文介绍了在Verilog中如何使用宏定义来简化代码,特别是在处理信号层级引用时遇到的问题。当直接使用宏定义导致交叉模块引用错误时,通过将宏定义转换为字符串类型可以解决该问题。示例代码展示了如何定义和使用`conv_str`宏来避免编译错误,从而正确地显示信号层级。这种方法对于理解Verilog中的宏定义和字符串操作具有实践指导意义。

本文介绍了在Verilog中如何使用宏定义来简化代码,特别是在处理信号层级引用时遇到的问题。当直接使用宏定义导致交叉模块引用错误时,通过将宏定义转换为字符串类型可以解决该问题。示例代码展示了如何定义和使用`conv_str`宏来避免编译错误,从而正确地显示信号层级。这种方法对于理解Verilog中的宏定义和字符串操作具有实践指导意义。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?