我用的是modelsim SE-64 10.1c,希望能和各路大神多多交流。

首先是一个4位计数器。具体代码如下:

module counter(count,clk,rst,initial_value);

input clk,rst;

input [3:0] initial_value;

output [3:0] count;

reg [3:0] count;

always@(posedge clk,posedge rst)

if(rst)

count<=initial_value; //复位count被赋予初值

else if(count==4'b1111)

count<=4'b0000; //到了15归0,其实这段可以不加,15+1后会自动归0

else

count<=count+4'b0001;

endmodule

代码应该比较容易理解,下面开始写testbench。其实testbench这个东西有固定的模板,各种不同电路的testbench基本上差异不大,请看:

`timescale 1ns/1ns //仿真时间间隔1ns

module test_counter;

reg clk,rst;

reg [3:0] initial_value;

wire [3:0] count;

counter u1(count,clk,rst,initial_value);

initial clk=0;

initial initial_value=4'b0000;

initial

begin

rst=0;//复位

#5 rst=1;

#4 rst=0;

end

always #50 clk=~clk; //时钟频率 1/100ns=10MHZ

endmodule

就是模块里的wire,reg类型和testbench里面的是相反的(体现出一个闭环的感觉),实例化一个顶层module,然后initial,最后always就行了。

.v文件都写完啦,下面开始仿真,File->New->Project,新建一个工程,将两个.v文件加进去。

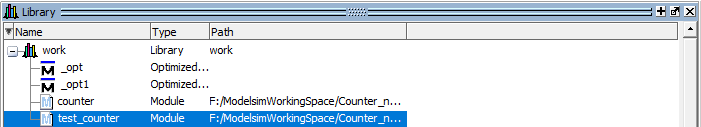

这里要注意,Library中一定得有个Project目录下的work库,否则会报错,如果没有,请新建一个。具体如下图:

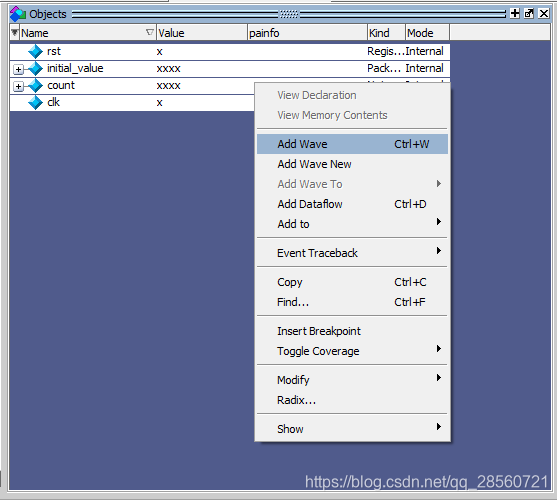

如上图,可以看到project下有两个v文件,Library栏的work显示了两个module,只要对test_counter仿真就行了,右键选中simulate(简单电路一般without optimization),进入仿真模式,选中想看的信号,右键add wave。如图:

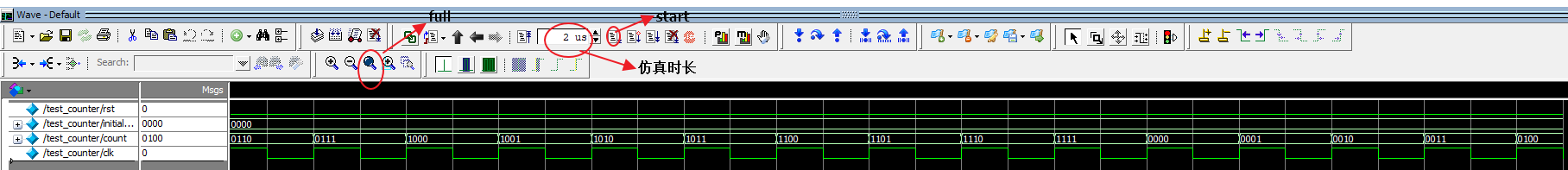

既然时钟周期是100ns,那么仿真时长选择20个周期,也就是2us,再点击开始按钮即可开始仿真。如下图:

有的时候仿真时间太长,不能在一个页面内同时显示,点击上图的full按钮即可。后面还会写一些别的模块。

2258

2258

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?