Lattice ddr3教程全攻略之仿真篇

对于这部分,首先建议安装好diamond3.1,modelsim se 10.1a这两个软件,如果想仔细分析DDR3的IP部分,可仔细阅读DDR3 SDRAM Controller IP Core User’s Guide,下面用ug代指。官网上可以download,还有DDR3的基本知识,可以到网上download《高手进阶,终极内存技术指南——完整进阶版》,这个文章值得一读。

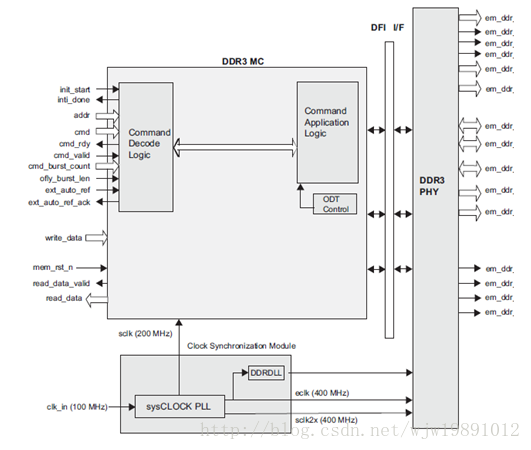

Lattice的ddr3控制器接口逻辑还是相对简单,比较好理解的,下面来看看DDR3 IP 的内部结构:

图:DDR3 IP逻辑框图

Initialization Module:根据JEDEC.的标准,在上电后对DDR3进行初始化配置,配置其相应的寄存器和工作方式等,具体配置的寄存器可以参看ddr3的协议文档,JEDEC规范写的很详细。当初始化配置完成后,该模块会给出一个done信号告诉用户。

sysCLOCK PLL:用于提供IP工作所需要的时钟,并提供给用户端一个时钟:k_clk。

Data Path Logic:用于从DDR3读取的数据转换到用户端,写入的数据不经过该模块,写入的数据从Command Application Logic (CAL)模块输入。

Command Decode Logic (CDL) :该模块用于译码命令,控制core按照设定的命令正确的访问ddr3芯片。

DDR3 PHY:用于转换单端的数据转换为差分给到ddr芯片端,和差分转单端输入。

以上部分有基础了解就行,不需要深究。

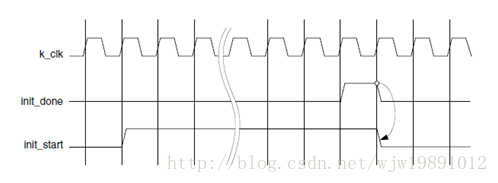

图:DDR初始化时序

当上电后,用户应该将init_start拉高至少200us,直到init_done被拉高一个周期,则将init_start拉低。用户检测到init_done被拉高后就表明芯片初始化完成了,也大概可以确定硬件是OK的。可以进行下一步操作。读和写控制非常简单,ug上说的很清楚,就不一一赘述了。

做DDR3设计之前当然是先仿真,这个毋庸置疑,那么仿真当然首选Modelsim,在仿真之前,先做好准备工作,那就是先编译好仿真所需要的库文件,编译库文件方法和Altera Xilinx类似,见《在Modelsim中建立LATTICE仿真库》一文,已共享。lattice的资料做的确实不如xilinx和altera。也是很多使用lattice fpga的工程师经常抱怨的一点,没有前人带的情况下使用lattice确实是非常恼火的。但是却也没有江湖传言的那么难用,其实很多时候并不是因为难,而是我们不愿意去了解,因为陌生而导致的恐惧,先入为主吧。那,废话不多说,开始进入主题。

现在假定你lattice库文件已经编译成功,那,我们当然要物尽其用,尽可能收集多的资源加快效率。。。此处省略一万字。首先说明,lattice的DDR3是带有Modelsim仿真例程的,只要在IP例化好了之后找到:***\ddr_p_eval\ddr3core\sim。然后在modelsim se中敲do ddr3core_eval.do就可以了,正常情况下是可以运行得到结果的,而且仿真初始化时间短,比altera快,这一点本人非常满意,而且激励写的很好懂,多以任务函数形式调度,这一点秒杀altera,altera还用的sys

本文是Lattice DDR3仿真教程,介绍了DDR3 IP的内部结构、初始化流程及仿真方法。建议使用Diamond 3.1和Modelsim SE 10.1a,文中详细讲解了如何配置DDR3 IP,包括DDR3 PHY、Command Decode Logic等模块。通过Modelsim进行仿真,提供仿真例程并指导用户进行IP配置,强调了DDR3设计的带宽计算和控制器策略对带宽的影响。

本文是Lattice DDR3仿真教程,介绍了DDR3 IP的内部结构、初始化流程及仿真方法。建议使用Diamond 3.1和Modelsim SE 10.1a,文中详细讲解了如何配置DDR3 IP,包括DDR3 PHY、Command Decode Logic等模块。通过Modelsim进行仿真,提供仿真例程并指导用户进行IP配置,强调了DDR3设计的带宽计算和控制器策略对带宽的影响。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?