二进制加法器

1. 基础知识

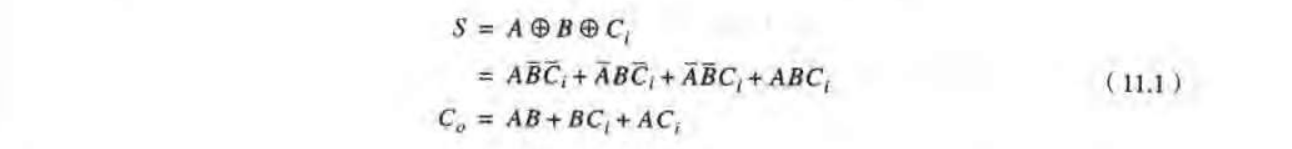

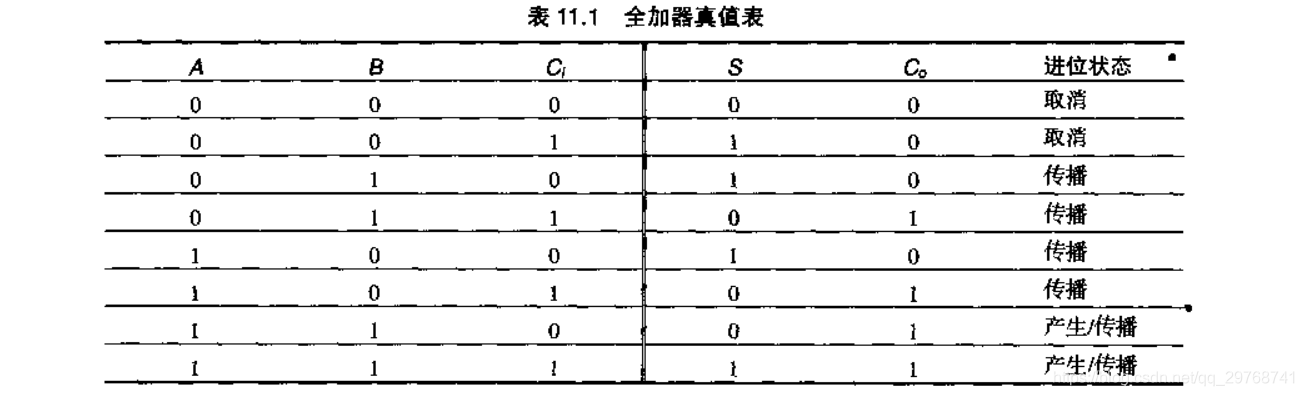

A、B为输入,Ci为进位输入,S为和,Co为进位输出

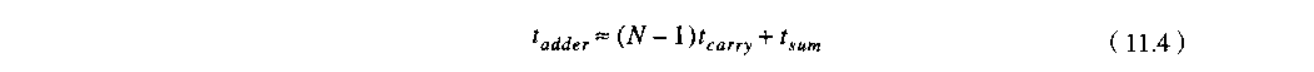

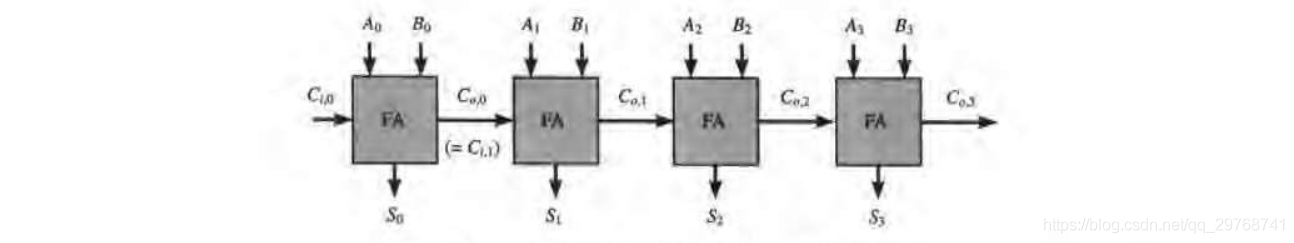

基础的加法器:逐位进位加法器 或 行波进位加法器(ripple carry adder) , 进位路径为关键路径,critical path

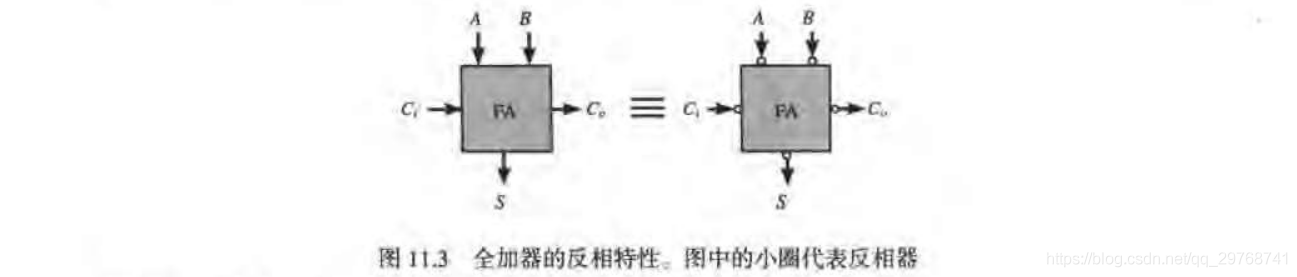

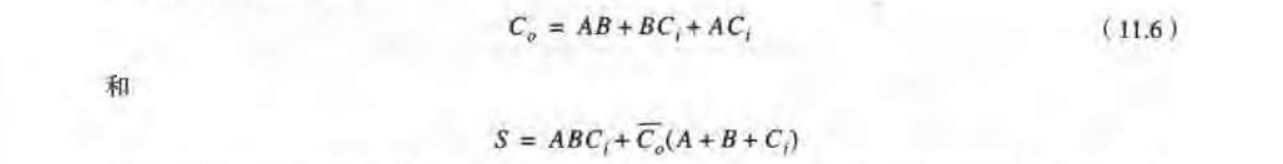

2. 加法器的反向特性

3. 加法器们

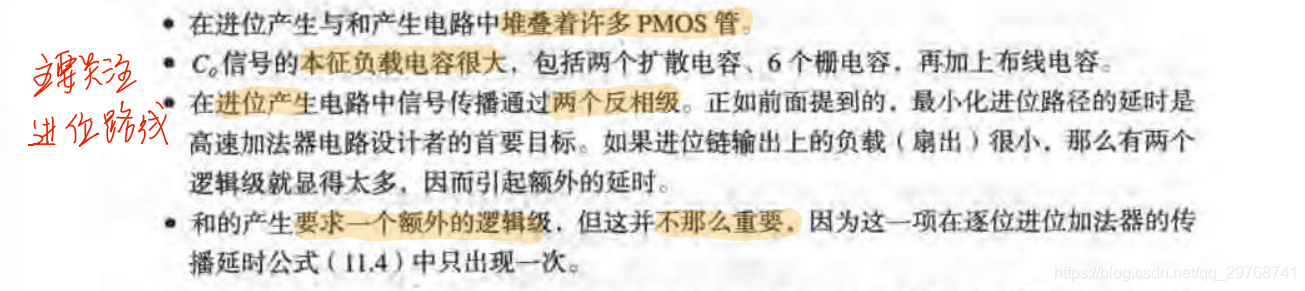

1. 静态加法器 —— 用互补CMOS

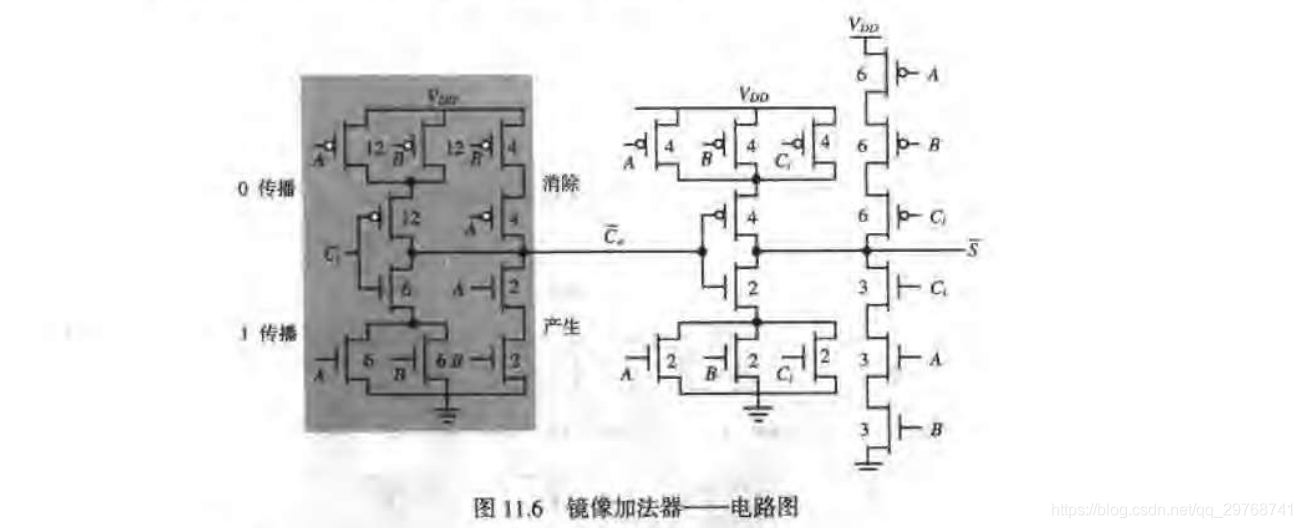

2. 镜像加法器

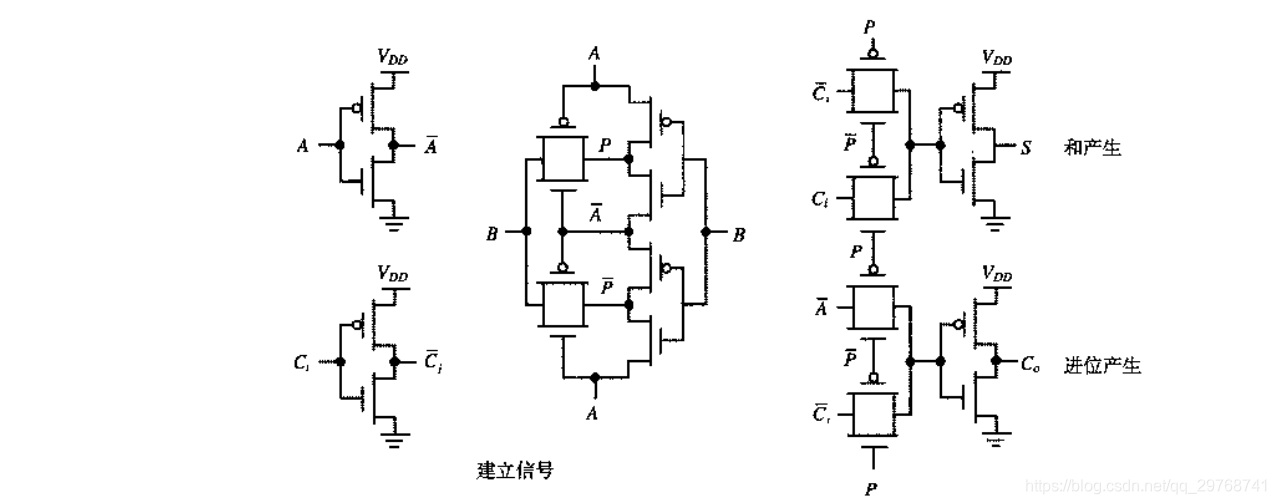

3. 传输门型加法器 —— S和Co有相同时间

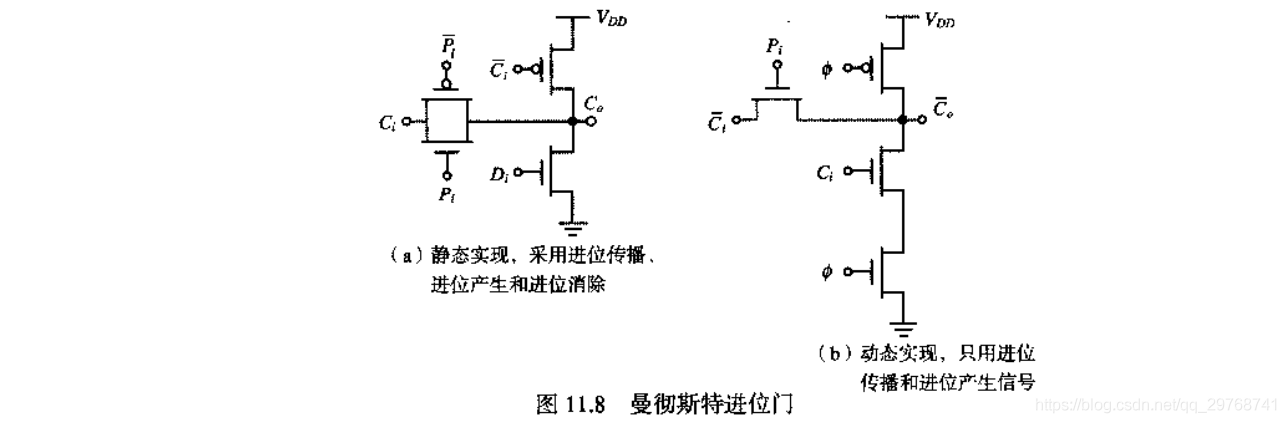

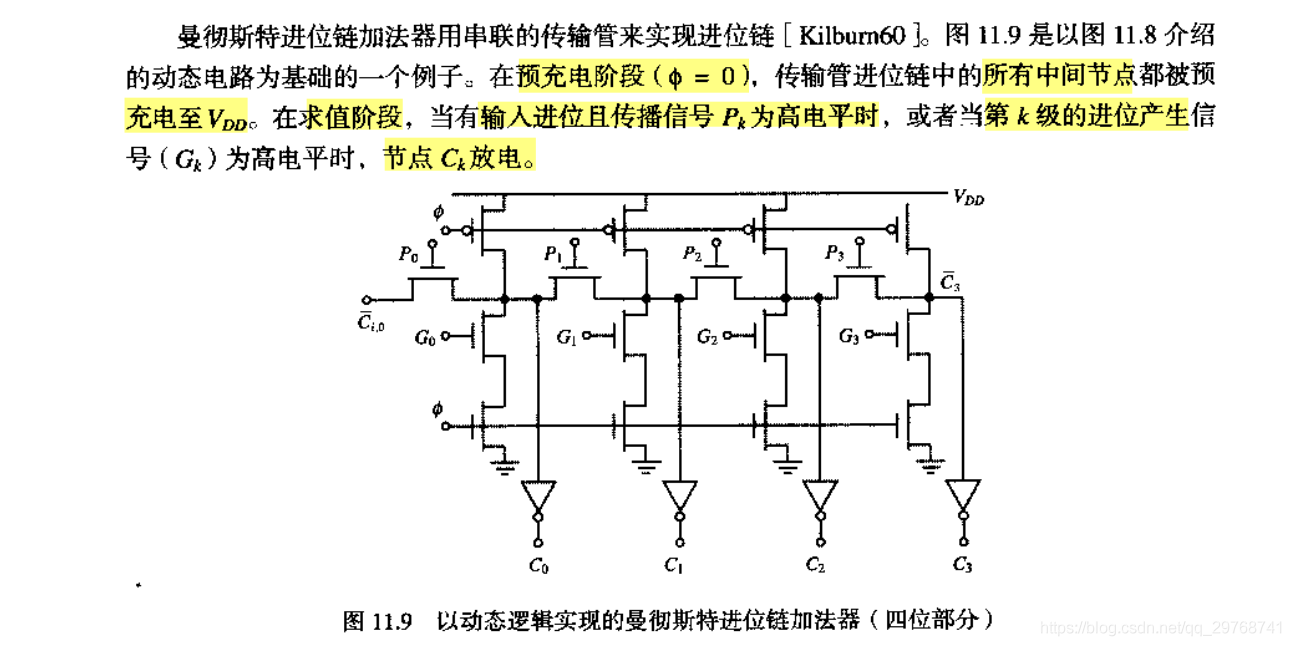

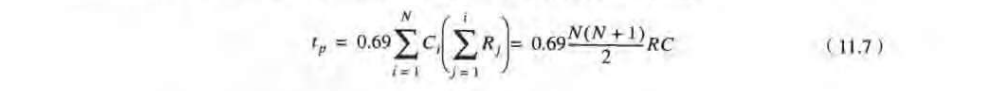

4. Manchester曼切斯特进位链加法器

如果P(传播)=1,Ci直接传播到Co。

动态实现更加简单,减少了Di信号。

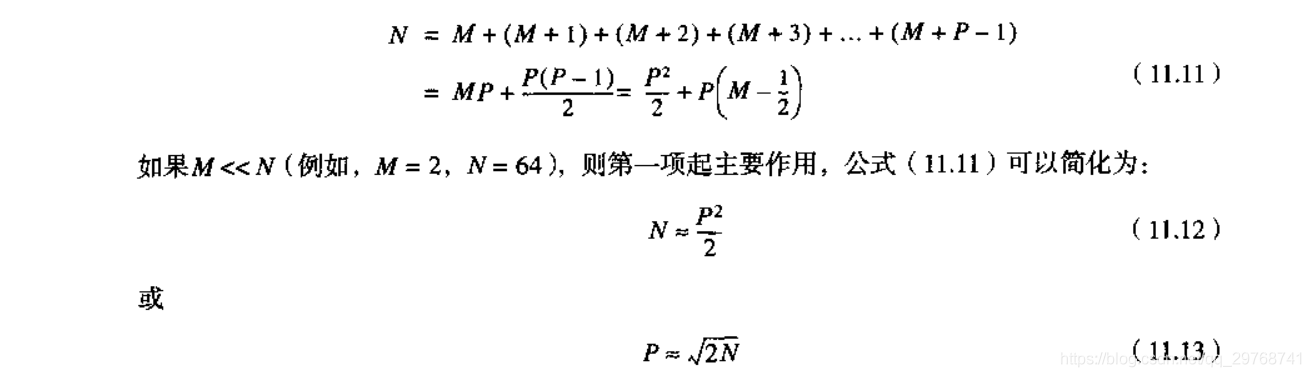

4. 逐位进位加法器只适合较少字长的加法——逻辑优化

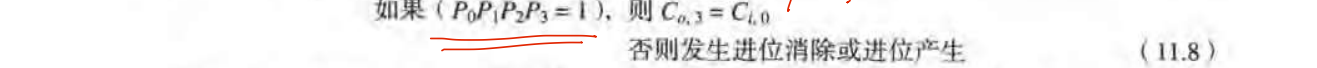

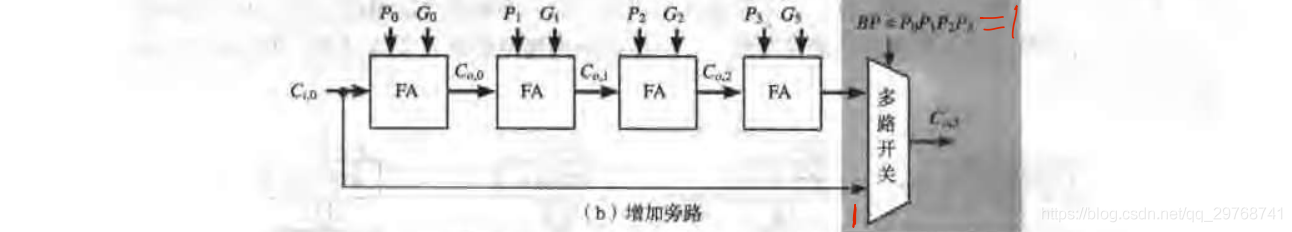

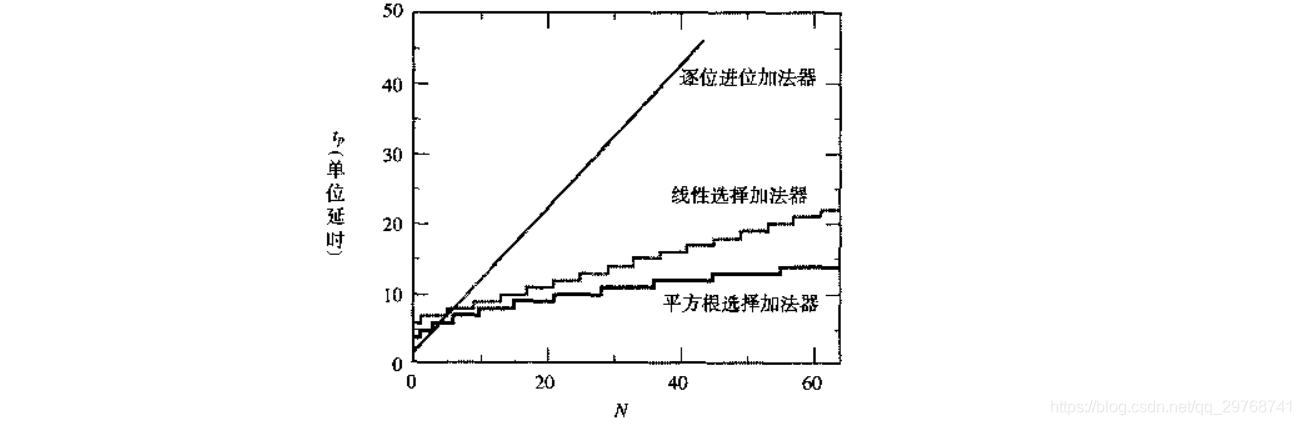

1. 进位旁路加法器(Carry-Bypass Adder)

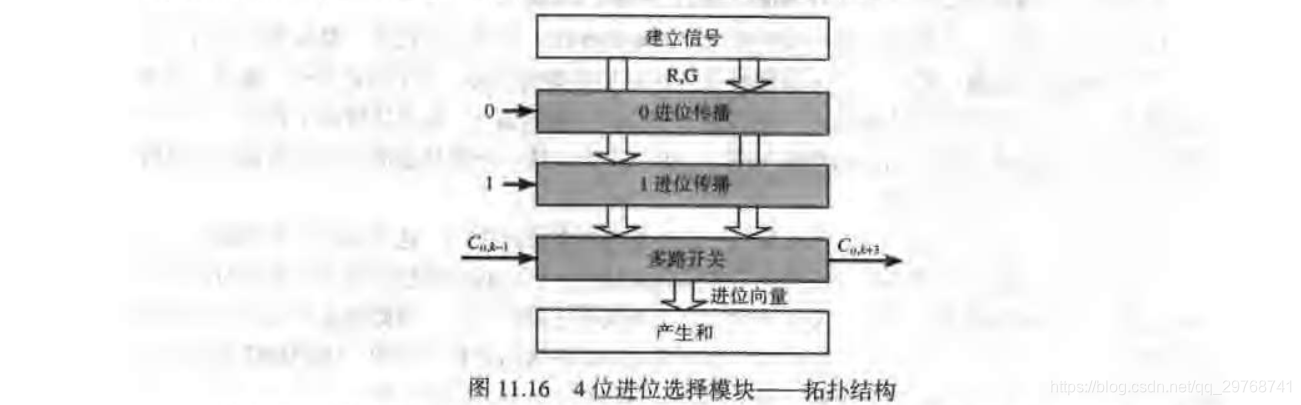

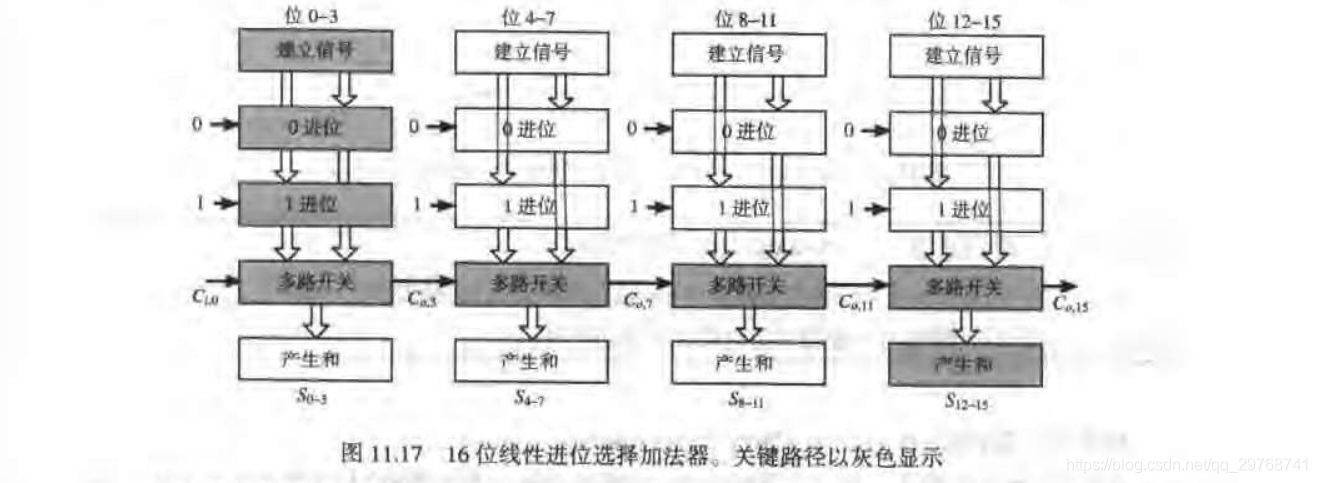

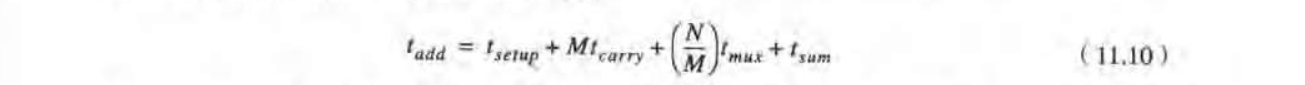

2. 线性进位选择加法器(Linear Carry-Select Adder)

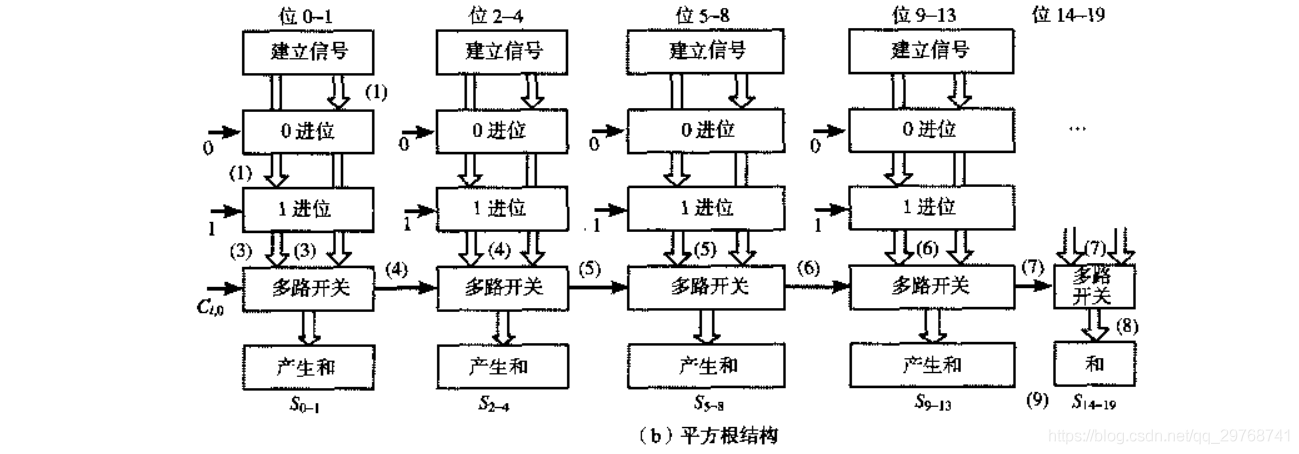

3. 平方根进位选择加法器(Square-Root Carry-Select Adder)

逐级增加计算位次

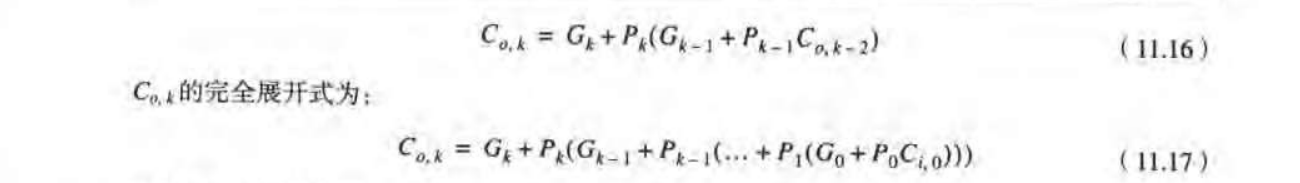

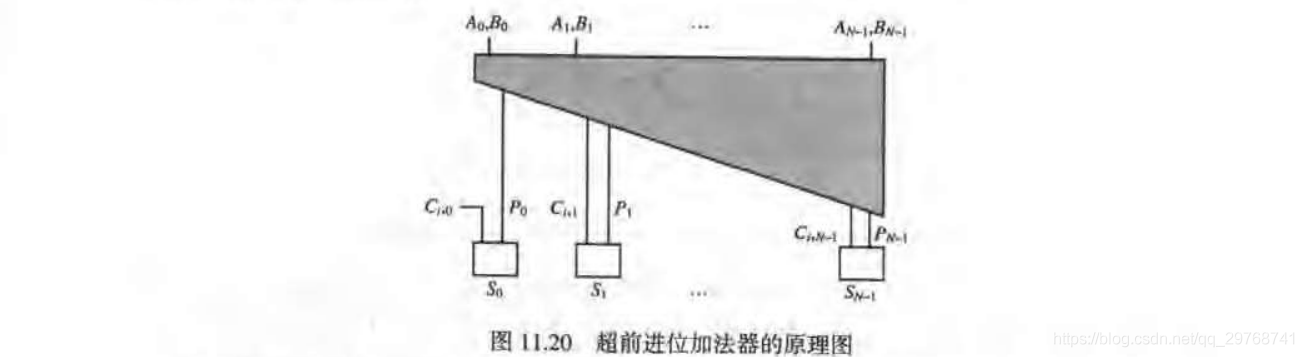

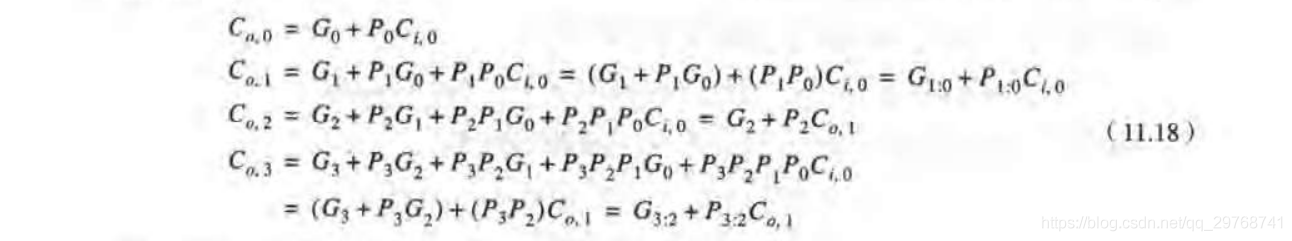

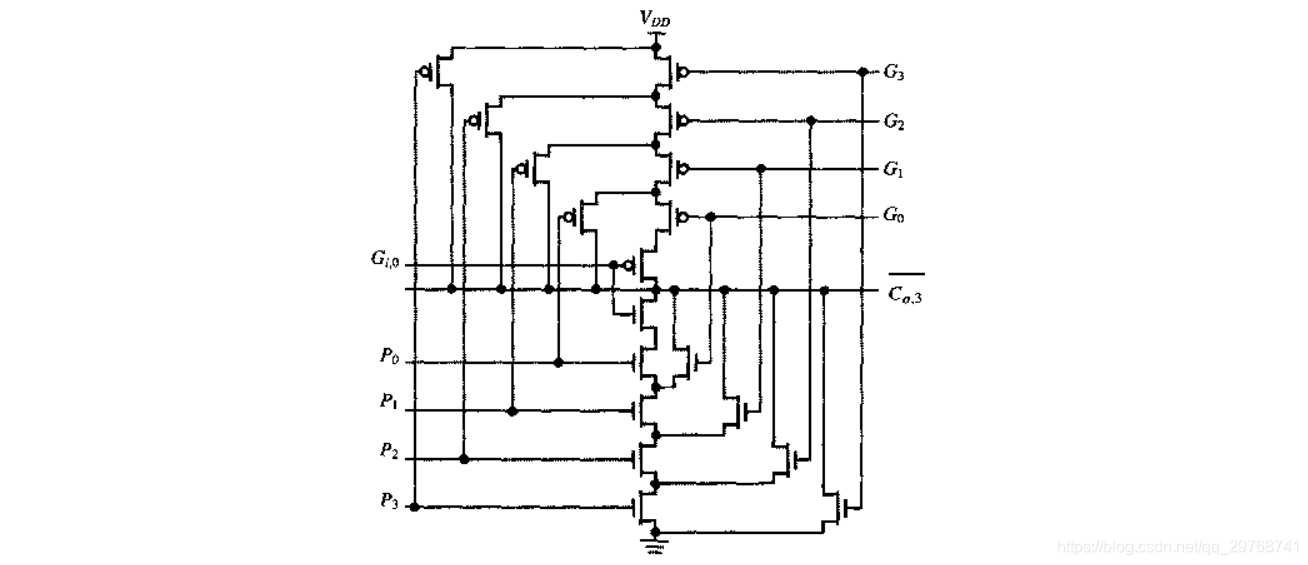

4. 超前进位加法器(Carry-Lookahead Adder)

4.1 单一超前进位加法器——一般用于N<=4

4.2 对数超前进位加法器

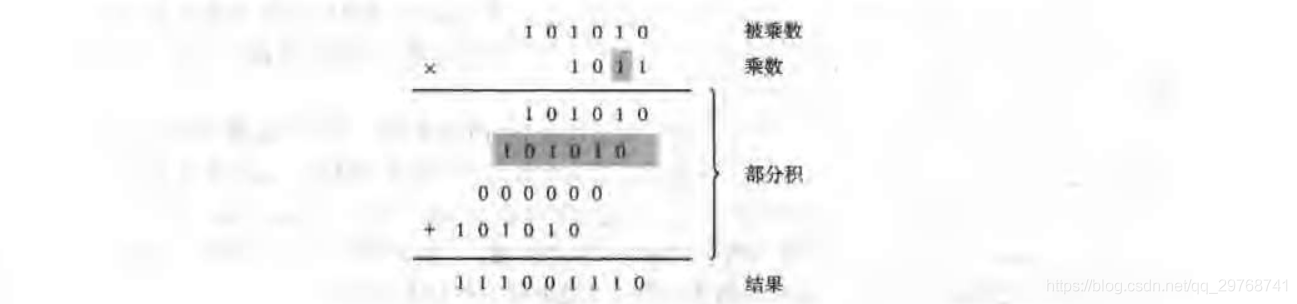

5. 乘法器

会有很多个部分积为0的情况,为了减少计算次数

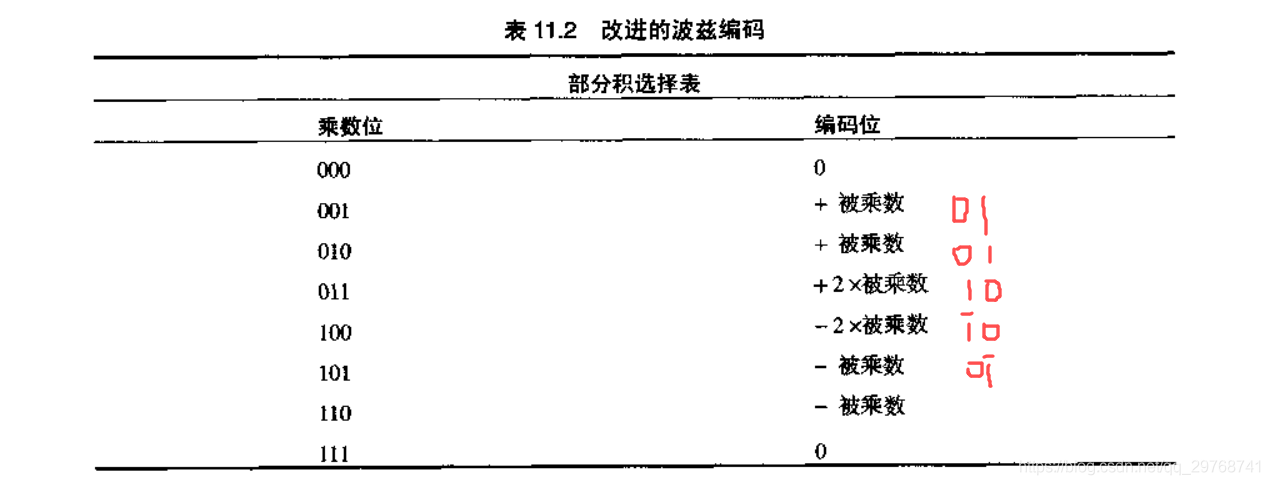

booth编码:

例子:10010(无符号)

左边+2个0 右边+1个0:00 10010 0

分组为:001 100 010:01 1‘0 01

3352

3352

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?