HKMG工艺技术简介

随着器件尺寸不断缩小到45nm及以下工艺技术,栅极介质层SiON的厚度降低到2nm以下,为了改善栅极泄漏电流,半导体业界利用高K介质材料HfO2和HfSiON取代SiON作为栅氧化层。

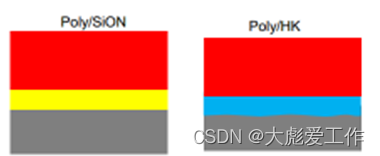

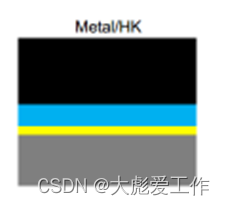

利用高K介质材料代替常规栅氧SiON和金属栅代替多晶硅栅的工艺称为HKMG工艺技术, HK是HighK的缩写, MG是Metal Gate的缩写,也就是金属栅极。

利用高K介质材料HfO2和HfSiON介质材料代替SiON也会引起很多问题:

1.高K介质材料与衬底之间会形成粗糙的界面,会造成载流子散射,导致载流子迁移率降低。

2.高K介质材料中的Hf原子会与多晶硅的硅原子发生化学反应形成Hf-Si键,从而形成缺陷中心,导致无法通过离子掺杂来改变多晶硅的功函数,造成费米能级的钉扎现象。

3.高K介质材料的高K值得益于内部偶极子结构,但是在栅介质层下表面附近的偶极子会发生振动并传递到沟道的硅原子,造成晶格振动,形成载流子声子散射,降低器件的速度。

解决不兼容的方法:

a) 半导体业界利用金属代替多晶硅作为器件栅极材料,利用金属栅代替多晶硅栅极可以改善费米能级的钉扎现象,同时金属栅极具有极高的电子密度,可以有效的解决多晶栅极耗尽问题。

b) 在高K介质材料与衬底之间的界面插入一层极薄的SiON薄膜,利用SiON薄膜作为过渡层可以得到理想的SiON与Si的界面,这样可以有效的改善高K介质材料与衬底之间的界面,也可以改善偶极子的振动对载流子迁移率的影响。

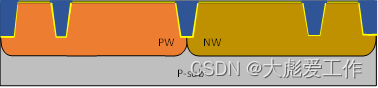

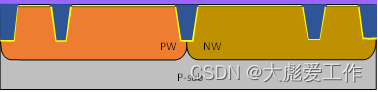

半导体业界提出了l两种实现HKMG工艺技术的集成方案:

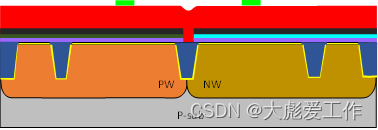

1.先栅(Gate-First)工艺技术,也称金属嵌入多晶硅(Metal Inserted Poly Silicon - MIPS)工艺技术,它的栅介质材料是HfSiON,同时在高K介质材料和多晶硅栅之间插入一层金属材料;

金属嵌入栅极工艺技术是指在高K介质材料与多晶硅栅之间嵌入高熔点金属TiN层和不同功函数层,功函数层称为“覆盖层(Cap layer)”。嵌入TiN的目的是为了解决金属嵌入栅极工艺中多晶硅栅耗尽,嵌入功函数覆盖层可以解决费米能级的钉扎现象。

调整栅极功函数的常用手段:在NMOS栅极工艺中,覆盖层的材料是一层La2O3薄层,La2O3材料含有更多负电性原子。在PMOS栅极工艺中,覆盖层的材料是一层Al2O3薄层,Al2O3材料含有更多正电性原子。

高K介质材料HfO2的介电常数是25,但是HfO2在温度超过500℃时会发生晶化,产生晶界缺陷,同时晶化还会造成表面粗糙度增加,这会引起漏电流增加,从而影响器件性能。所以HfO2不符合金属嵌入栅极工艺技术,可以通过对HfO2进行掺杂来改善它的高温性能,对HfO2进行掺Si和氮化形成HfSiON,HfSiON具有极好的高温稳定性,但是它的介质常数只有15。

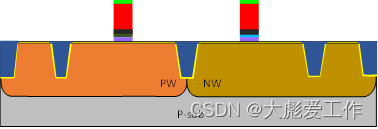

2.后栅(Gate-Last) 工艺技术,也称金属替代栅(Replacement Metal Gate - RMG)工艺技术,它的栅极是金属材料,它的栅介质材料是HfO2。

金属替代栅极工艺是通过原子层淀积技术淀积高K介质材料HfO2,它的介电常数是25。因为金属嵌入栅极工艺的高K介质材料是HfSiON,它的介质常数只有15。相对而言,金属替代栅极工艺的高K介质材料HfO2更具有优势,而当金属嵌入栅极工艺进入28nm工艺制程时,高K介质材料HfSiON已经不能满足提高器件性能的要求,金属嵌入栅极工艺被金属替代栅极工艺取代。

在金属替代栅极工艺中PMOS的金属栅极材料是TaN,NMOS的金属栅极材料是TaAlN。因为金属替代栅极工艺中金属栅极是淀积在多晶硅沟槽里的,它要求淀积工艺要具有很好的台阶覆盖率,所以选择原子层淀积技术淀积金属栅极。

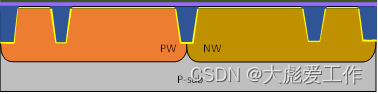

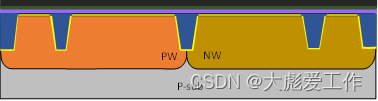

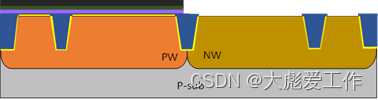

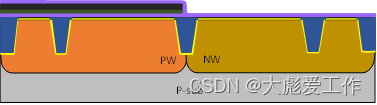

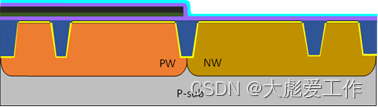

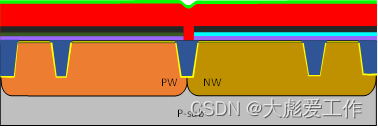

金属嵌入多晶硅栅工艺流程

1.通过ISSG(In Situ Steam Generation原位水汽生成)工艺技术淀积一层的SiON薄膜,目的是改善高k介质材料与衬底硅的界面态。

2.通过MOCVD(Metal Organic Chemical Vapor Deposition)淀积一层高k介质层HfSiO,然后再经过高温氮化形成HfSiON。

3. 通过原子层淀积技术淀积厚度1nm的La2O3薄膜,形成NMOS上覆盖层,目的是通过改变NMOS栅极的功函数来调节NMOS的阈值电压Vt。

4. 通过RFPVD淀积厚度5nm~10nm的TiN金属覆盖层,形成金属栅,改善栅极多晶硅耗尽。

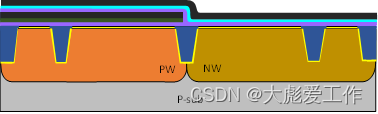

5. 通过光刻和刻蚀去除PMOS区域的栅介质层和金属薄膜。

6.同步骤1。

7.通过MOCVD淀积一层高k介质层HfSiO,然后再经过高温氮化形成HfSiON。

8. 通过原子层淀积技术淀积厚度1nm的的Al2O3薄膜,形成PMOS上覆盖层,目的是通过改变PMOS栅极的功函数来调节PMOS的阈值电压Vt。

9. 通过RFPVD淀积厚度5nm~10nm的TiN金属覆盖层,形成金属栅,改善栅极多晶硅耗尽。

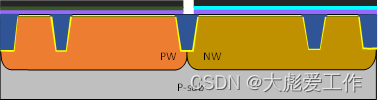

10.通过光刻和刻蚀去除NMOS区域第二次淀积的覆盖层。

11. 通过LPCVD淀积多晶硅栅。

12. 通过LPCVD淀积SiO2和SiON硬掩膜版层。

13. 通过光刻和刻蚀形成硬掩膜版层。

14. 通过干法刻蚀形成栅极。

金属替代栅级工艺流程及HKMG工艺技术限制详见下期博客。

本文详细介绍了HKMG工艺,包括高K介质材料HfO2/HfSiON的应用及其带来的问题,如载流子散射和费米能级钉扎。讲解了金属栅极替代和金属嵌入多晶硅栅的过程,并对比了Gate-First和Gate-Last工艺。着重讨论了解决方案和工艺流程,以及HfO2的高温性能改善。

本文详细介绍了HKMG工艺,包括高K介质材料HfO2/HfSiON的应用及其带来的问题,如载流子散射和费米能级钉扎。讲解了金属栅极替代和金属嵌入多晶硅栅的过程,并对比了Gate-First和Gate-Last工艺。着重讨论了解决方案和工艺流程,以及HfO2的高温性能改善。

9399

9399

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?