HKMG工艺技术基础知识及金属嵌入多晶硅栅工艺流程详见《【半导体先进工艺制程技术系列】HKMG工艺技术(上)》。

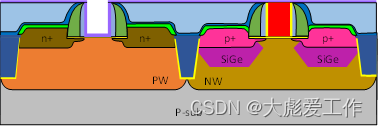

金属替代栅级工艺流程

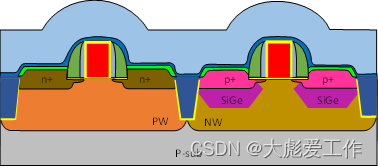

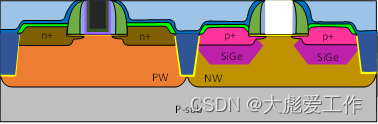

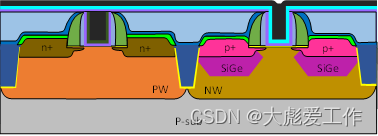

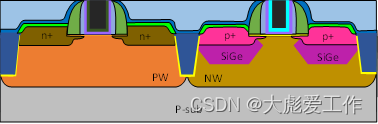

PMOS的有源区是SiGe应变材料,利用应变材料SiGe可以提高载流子空穴的迁移率,从而提高PMOS的速度。

1. 通过CVD淀积ILD层。

2. 通过CMP进行ILD平坦化。

3. 通过光刻和干法刻蚀去掉NMOS的多晶硅栅极。

4. 通过湿法刻蚀去掉氧化硅。

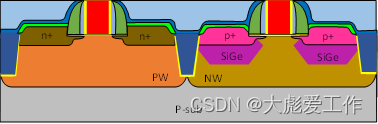

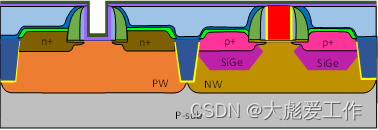

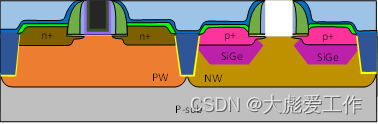

5. 通过ISSG工艺技术淀积一层的SiON薄膜,目的是改善高k介质材料与衬底硅的界面态。再通过原子层淀积技术淀积高K介质材料HfO2。

6. 通过原子层淀积技术淀积n型金属栅TaAlN。

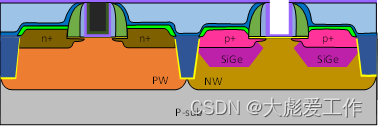

7. 通过原子层淀积技术淀积低阻金属填充栅沟槽

8. 通过CMP进行平坦化,清除多余的金属。

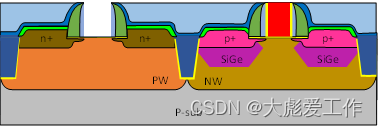

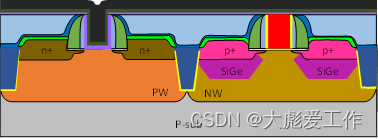

9. 通过光刻和干法刻蚀去掉PMOS的多晶硅栅极。

10. 通过湿法刻蚀去掉氧化硅。

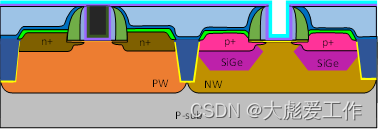

11. 通过ISSG工艺技术淀积一层的SiON薄膜,目的是改善高k介质材料与衬底硅的界面态。再通过原子层淀积技术淀积高K介质材料HfO2。

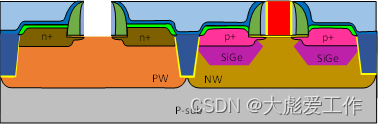

12. 通过原子层淀积技术淀积p型金属栅TaN。

13. 通过原子层淀积技术淀积低阻金属填充栅沟槽。

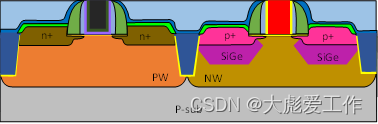

14. 通过CMP进行平坦化,清除多余的金属。

HKMG工艺技术限制

虽然HKMG利用金属栅极和高K栅介质层解决了多晶硅耗尽问题和栅极漏电问题,但是它也在硅衬底和高K栅介质层引入了SiON界面层,SiON的介电常数比较低在4~7之间,SiON的物理厚度在0.6nm左右,所以SiON界面层的削弱了高K栅介质层对先进工艺的中栅极电容的贡献。因为在技术上没有办法实现移除SiON界面层,SiON界面层的问题将一直存在,未来工艺的方向是仅仅只能通过提高工艺技术把SiON界面层的物理厚度从0.6nm降低到0.3nm左右。另外,衬底沟道量子化的问题也会一直存在,在技术上也没办法改善它。

相关内容

本文详细介绍了HKMG(高K金属栅极)工艺技术,包括其在提升PMOS速度方面的应用,以及金属替代栅级的具体步骤。工艺流程涉及CVD淀积、CMP平坦化、干法和湿法刻蚀、原子层沉积等技术。尽管HKMG解决了多晶硅耗尽和栅极漏电问题,但SiON界面层的存在仍限制了其性能,未来工艺将致力于减小该界面层的物理厚度。

本文详细介绍了HKMG(高K金属栅极)工艺技术,包括其在提升PMOS速度方面的应用,以及金属替代栅级的具体步骤。工艺流程涉及CVD淀积、CMP平坦化、干法和湿法刻蚀、原子层沉积等技术。尽管HKMG解决了多晶硅耗尽和栅极漏电问题,但SiON界面层的存在仍限制了其性能,未来工艺将致力于减小该界面层的物理厚度。

4161

4161

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?