VCS全程是 Verilog Compiled Simulator,其中包含PLI接口,可以调用C和C++一些程序。支持行为级描述、RTL(寄存器传输级)和Gate-level(门级:是RTL经过综合后得到的,与具体工艺库相关)。

一、VCS工作过程

VCS作为编译型仿真工具,工作过程主要分为两个大步骤,分别是编译和仿真

编译:VCS把我们编写的Verilog、SystemVerilog和c++语言等代码经过翻译变成可执行的二进制文件simv。

仿真:经过编译之后,就是仿真。

二、VCS命令格式

2.1 compile_time_options(编译开关)

执行vcs的编译格式:vcs source_files [compile_time_options]

source_files:我们编写的Verilog、SystemVerilog等。

compile_time_options:编译开关,控制VCS如何编译这些source_files。

-Mupdate:增量编译。当一个大型soc系统中,只有一处代码需要改动,那么使用此命令只需对改动的代码编译,以此节省编译时间。

-R:编译产生后的文件simv,要执行这个文件需要这条命令**./simv**,当添加了-R,就自动执行文件simv。

-l filename :将编译产生的文件放到filename中。

-sverilog:支持SystemVerilog。

+v2k:支持verilog2001的标准。

-v lib_file:如果在我们rtl代码中使用到一些厂商的工艺库,使用-v lib_file 寻找该工艺库。

-y lib_dir: 告诉VCS工艺库的路径。

+libext+lib_ext:使用文件的扩展名lib_ext在路径lib_dir搜索。比如:-y $SYNOPSYS/dw/sim_ver +libext+.v 在 $SYNOPSYS/dw/sim_ver 寻找有.v后缀的文件

+incdir+inc_dir:在路径inc_dir搜索rtl中使用`include文件。

-f file:将source_files 文件整合到一个文件中。

-o foo:编译产生后的文件simv,可以使用-o foo,将simv变成foo。

+define+<macro_name>=:如果在代码中使用到了宏,可以在编译的时候定义宏。

2.2 run_time_options(仿真开关)

执行vcs的仿真格式:simv [run_time_options]

-s: 结束仿真在time0时。

-l logfile:在仿真的时候输出的文件全部写到logfile中,包括display语句。

-gui:打开DVE仿真界面在仿真的时候。

&:后台执行

三、举例说明

3.1 准备文件

fsm_moore.v 放于rtl目录下

module fsm_moore(

//input signals

input clk,

input rst_n,

//output signals

output reg [3:0] dout,

output reg [2:0] q

);

parameter idle =2'b00,

s1 =2'b01,

s2 =2'b10,

s3 =2'b11;

reg [1:0] state,next;

always@(posedge clk or negedge rst_n)

begin

if(rst_n==1'b0)

state<= idle;

else

state<= next;

end

always@(*)

begin

next=idle;

dout=4'd0;

case(state)

idle:begin

dout=4'd0;

next=s1;

end

s1: begin

dout=4'd1;

next=s2;

end

s2: begin

dout=4'd2;

next=s3;

end

s3: begin

dout=4'd9;

next=idle;

end

endcase

end

always@(posedge clk or negedge rst_n)

begin

if(rst_n==1'b0)

q<=3'd0;

`ifdef INC_COUNTER

else

q<=q+1'b1;

`else

else

q<=q-1'b1;

`endif

end

endmodule

fsm_top.v 放于tb目录下

`timescale 1ns/1ns

module fsm_top;

reg clk;

reg rst_n;

wire [3:0] dout;

wire [2:0] q;

integer run_num=20;

initial begin

clk=0;

forever #5 clk=~clk;

end

initial begin

rst_n=1'b1;

repeat(2)@(posedge clk);

rst_n=1'b0;

repeat(2)@(posedge clk);

rst_n=1'b1;

repeat(run_num)@(posedge clk);

$display("finish simulation @ [%0t]",$time);

$finish;

end

fsm_moore fsm_moore_inst(

//input signals

.clk(clk),

.rst_n(rst_n),

//output signals

.dout(dout),

.q(q)

);

endmodule

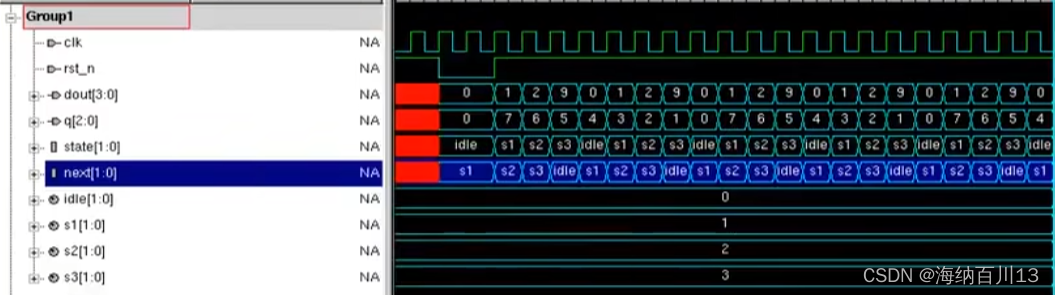

3.2 执行编译仿真

1.在sim目录下

输入:vcs ../rtl/fsm_moore.v ../tb/fsm_top.v +v2k -debug_all -l compile.log

2.在sim目录下产生simv文件时

输入:./simv -gui &

结果如下图所示:

3187

3187

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?