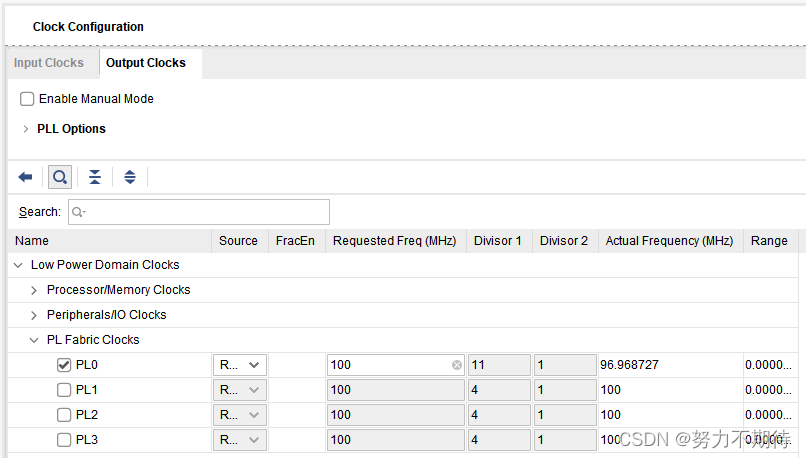

ZYNQ PS端最多可以分配4个时钟供给PL端使用,见下图。

本文的目的:在XCZU21DR环境下,PS给PL提供一个100MHz的时钟,PL端根据此时钟产生1S信号,点亮LED。

添加&配置Zynq UltraScale+ MPSoc IP

双击该IP,在Clock Configuration -> Output Clocks -> Low Power Domain Clocks -> PL Fabric Clocks中设置见上图。

这个PL Fabric Clocks就是PS提供给PL的100MHz时钟。

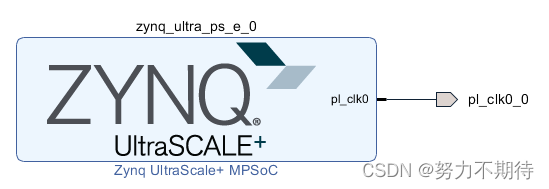

最终将pl_clk0引出,得到下图。

执行Generate Output Products和Create HDL Wrapper,最后修改顶层文件如下:

module design_1_wrapper(

output led

);

wire pl_clk0_0;

design_1 design_1_i(

.pl_clk0_0(pl_clk0_0));

clk_div_N #(

//.FREQ_WORD(32'd43) //1S闪烁1次

// .FREQ_WORD(32'd20) //2S闪烁1次

.FREQ_WORD(32'd86) //0.5S闪烁1次

) clk_div_N_inst(

.clk_in(pl_clk0_0),

.rst_n(1'b1),

.clk_out(led)

);

endmoduleclk_div_N内容如下:

//clk_in = 50MHz, 可任选

//clk_out = clk_inK/(2^32),32表示计数器位数

//频率控制字FREQ_WORD = clk_out(2^32)/clk_in, 32表示计数器位数

module clk_div_N #(

parameter FREQ_WORD = 32'd1431655765 //3分频

) (

input clk_in,

input rst_n,

output reg clk_out);

//--------------------------------------

reg [31:0] max_value;

always@(posedge clk_in or negedge rst_n)

begin

if(!rst_n)

max_value <= 1'b0;

else

max_value <= max_value + FREQ_WORD;

end

//--------------------------------------

always@(posedge clk_in or negedge rst_n)

begin

if(!rst_n)

clk_out <= 1'b0;

else

begin

if(max_value < 32'h7FFF_FFFF)

clk_out <= 1'b0;

else

clk_out <= 1'b1;

end

end

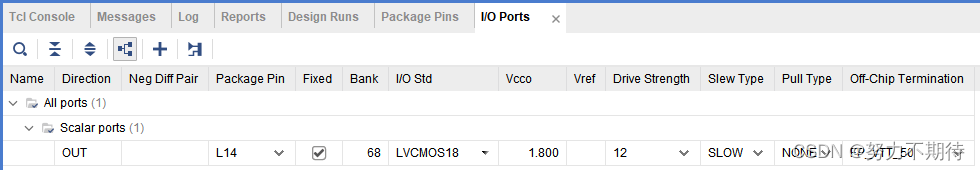

endmodule执行综合、实现后,完成led的引脚约束即可,见下图。

代码经过上板测试通过。

代码经过上板测试通过。

本文介绍了在XCZU21DR环境下,如何配置ZynqUltraScale+MPSocIP,由PS端提供100MHz时钟给PL端,PL端通过计数器模块clk_div_N产生1S信号,用于控制LED闪烁。经过综合和实现后,上板测试成功。

本文介绍了在XCZU21DR环境下,如何配置ZynqUltraScale+MPSocIP,由PS端提供100MHz时钟给PL端,PL端通过计数器模块clk_div_N产生1S信号,用于控制LED闪烁。经过综合和实现后,上板测试成功。

3322

3322

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?