电阻

互连电阻的最佳近似

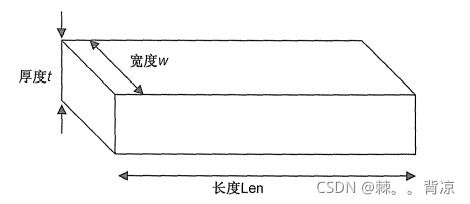

电路中的导线可以看作一个理想的电阻。导线模型如下:

对于导线横截面横定的情况,电阻值可以由下表示:

R

=

ρ

L

e

n

A

R=\rho \frac{Len}{A}

R=ρALen

其中

ρ

\rho

ρ表示导线的体电阻率(单位为

Ω

⋅

c

m

Ω \cdot cm

Ω⋅cm), Len表示导线长度(cm),A表示横截面积(

c

m

2

cm^2

cm2)

ρ

\rho

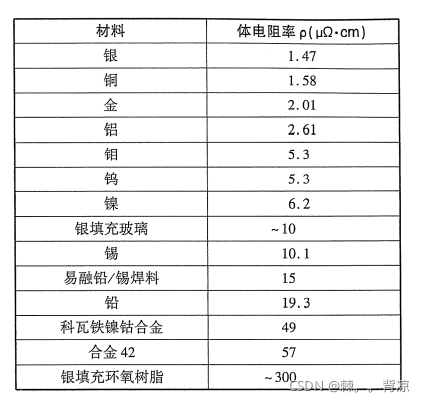

ρ体电阻率是材料的固有特性为电导率的倒数,常用的材料体电阻率为:

单位长度电阻

对于横截面均匀的导线,如PCB中的导线,其单位长度电阻为:

R

L

=

R

L

e

n

=

ρ

A

R_L=\frac{R}{Len}=\frac{\rho }{A}

RL=LenR=Aρ

这里有个经验公式:键合线(半导体封装用的核心材料,是连接引脚和硅片、传达电信号的零件)的单位长度电阻为1Ω/in,即0.1in长的键合线其阻值约为0.1Ω。

方块电阻

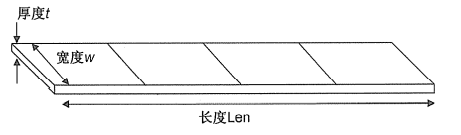

在PCB上走向,其厚度一般都是相同的,对于这种相同的线条,其电阻有:

R

=

ρ

L

e

n

t

×

w

=

ρ

t

L

e

n

w

R=\rho \frac{Len}{t\times w}=\frac{\rho }{t}\frac{Len }{w}

R=ρt×wLen=tρwLen

其中

L

e

n

w

\frac{Len }{w}

wLen是长度和宽度的比值,如果将

L

e

n

×

w

Len\times w

Len×w的导线分成

n

×

w

×

w

n\times w\times w

n×w×w个方块,那么

ρ

t

\frac{\rho }{t}

tρ代表方块电阻

R

s

q

R_{sq}

Rsq

所以导线的电阻

R

=

n

R

s

q

R=nR_{sq}

R=nRsq

方块电阻的阻值不会随着正方形边长改变,如果其长加倍,电阻值加倍,但是其宽度也加倍,那么电阻值减半,最后导致方块电阻的阻值不变。

这里有个经验法则:0.5盎司铜的方块电阻是1mΩ/sq;1盎司铜的方块电阻是0.5mΩ/sq,一根长为5in,宽为5mil的铜导线,可以划分为1000个串联的方块,所以其电阻值为1Ω。

同时可以由方块电阻得到单位长度电阻:

R

L

=

R

s

q

×

1

w

R_L=R_{sq}\times \frac{1}{w}

RL=Rsq×w1

其中w=线宽。

电容

平行板近似

电容平行板近似:

C

=

ϵ

0

A

h

C=\epsilon_0 \frac{A}{h}

C=ϵ0hA

其中A表示平板面积,h表示平板距离,

ϵ

0

\epsilon_0

ϵ0表示自由空间介电常数(0.089pF/cm)。

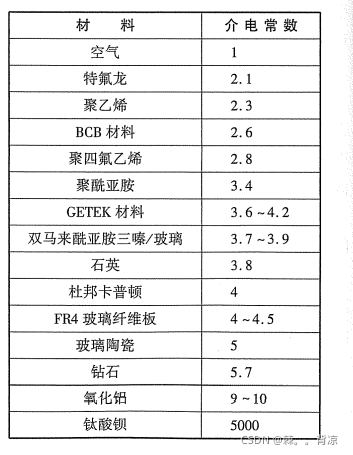

常见材料的相对介电常数

ϵ

r

\epsilon_r

ϵr, 其值为导体被绝缘材料包围时的电容比上被空气包围时的电容:

去耦电容

为了减小电源分配系统中的电压轨道塌陷,就要在电源和地之间有足够的去耦电容。在一定时间

δ

t

\delta t

δt 内,电容可以阻止电源电压的下沉。

在电源轨道上,如果芯片的功率损耗为P,则电流为I=P/V。由于去耦电容的作用,电压下沉幅度到电源电压的5%时的时间近似为:

δ

t

=

0.05

C

V

2

P

\delta t=0.05C\frac{V^2}{P}

δt=0.05CPV2

V=电源电压;

δ

t

\delta t

δt =电压下降幅度达到电源电压的5%的时间;

P表示芯片的功率;

C表示去耦电容;

通常需要足够大的去耦电容,以提供至少5us的时间,直到电压稳压器提供足够的电流。

单位长度电容

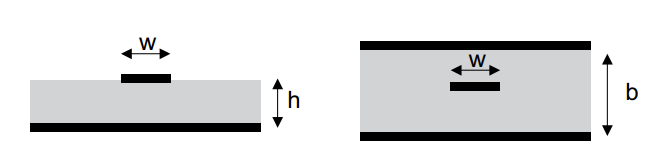

微带线(图左)的单位长度电容近似为:

C

L

=

0.67

(

1.41

+

ϵ

r

)

l

n

5.98

h

0.8

w

+

t

≈

0.67

(

1.41

+

ϵ

r

)

l

n

7.5

h

w

C_L=\frac{0.67(1.41+\epsilon_r)}{ln { \frac{5.98h}{0.8w+t}}}\approx \frac{0.67(1.41+\epsilon_r)}{ln 7.5{ \frac{h}{w}}}

CL=ln0.8w+t5.98h0.67(1.41+ϵr)≈ln7.5wh0.67(1.41+ϵr)

微带线(图左)的单位长度电容近似为:

C

L

=

1.4

ϵ

r

l

n

1.9

b

0.8

w

+

t

≈

1.4

ϵ

r

l

n

2.4

b

w

C_L=\frac{1.4\epsilon_r}{ln { \frac{1.9b}{0.8w+t}}}\approx \frac{1.4\epsilon_r}{ln 2.4{ \frac{b}{w}}}

CL=ln0.8w+t1.9b1.4ϵr≈ln2.4wb1.4ϵr

这里有一个经验法则:FR4板上50Ω传输线的单位长度电容约为3.5pF/in。

电感

电感是对表面磁场强度的数值积分。

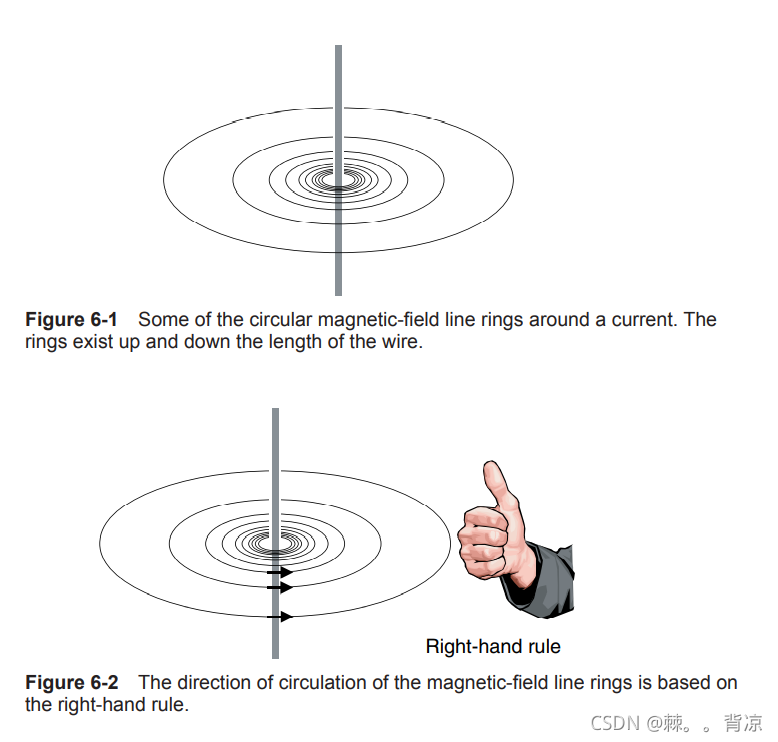

在电流的周围会形成闭合磁力线圈,其方向遵守右手定则。

电感是导体电流1A时周围磁力线的匝数,电感与流过单位安培电流时导体周围的磁力线匝数有关,即:

L

=

N

/

I

L=N/I

L=N/I

L=电感(H),

N=导体周围的磁力线匝数(Wb)

I=导体中的电流。

电感可以看作是用于测量导体产生磁力线圈的效率。

为了区分磁力线圈源头,通常将电感分为自感和互感。为了知道磁力线圈所围绕电流回路的大小,引入了回路电感和局部电感。

自感是指导线中流过单位安培电流时,所产生的环绕在导线自身周围的磁力线匝数。通常我们所说的电感实际上是导线的自感。

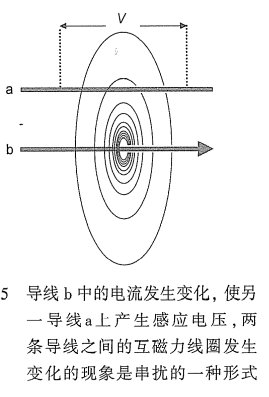

互感是指一条导线中流过单位安培电流时,所产生的环绕在另一条导线周围的磁力线匝数。

感应电动势

导线周围的磁力线总匝数发生变化,就会在导线两端产生感应电压,即:

V

=

Δ

N

/

Δ

t

V=\Delta N/\Delta t

V=ΔN/Δt

V=导线两端电压;

Δ

N

\Delta N

ΔN=磁力线匝数的变化量;

Δ

t

\Delta t

Δt=磁力线匝数的变化时间。

将电感带入公式则有

V

=

Δ

L

I

/

Δ

t

=

L

d

I

d

t

V=\Delta LI/\Delta t=L \frac{dI}{dt}

V=ΔLI/Δt=LdtdI

感应电压正是电感在信号完整性中意义重大的根本原因,如果电流变化时没有产生感应电压,信号就不会受到电感的影响。 这个由电流变化产生的感应电压引起了传输线效应、突变、串扰、开关噪声、轨道塌陷、地弹和大多数电磁干扰源。

在图中的情况下,产生的电压噪声为

V

n

o

i

s

e

=

M

d

M

d

t

V_{noise}=M\frac{dM}{dt}

Vnoise=MdtdM

V

n

o

i

s

e

V_{noise}

Vnoise=表示导线a中的感应电压噪声;

M=两条线之间的互感;

I=流过导线b中的电流。

上诉噪声也叫开关噪声或者

Δ

I

\Delta I

ΔI噪声。

有效电感、总电感或净电感及地弹

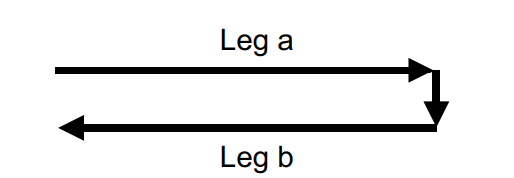

如图,导线组成一个完整的回路,回路产生的电压噪声由该支路周围磁力线匝数变化的速度确定。

一条支路周围的磁力线由该支路中电流产生的磁力线(自感)和其他支路产生的磁力线(互感)两部分组成。当电流为1A时,某支路周围的磁力线匝总数叫做有效电感、总电感或净电感

我们通过两个支路的局部电感计算出每条支路的有效电感。如图,a,b支路都有自身的局部电感,分别为

L

a

L_a

La和

L

b

L_b

Lb,它们之间还存在互感,记为

L

a

b

L_{ab}

Lab;回路中的电流为I,其在支路a和b中,大小等方向反。

对于支路b,其自身电流的磁力线匝数为

N

b

=

I

L

b

N_b=IL_b

Nb=ILb,来源于支路a产生的互感的磁力线线圈匝数为

N

a

b

=

I

L

a

b

N_{ab}=IL_{ab}

Nab=ILab。

所以围绕在支路b周围的磁力线总匝数(支路a因为其电流与支路b的电路相反,所以产生的磁力线相反)为:

N

t

a

t

a

l

=

N

b

−

N

a

b

=

(

L

b

−

L

a

b

)

I

N_{tatal}=N_b-N_{ab}=(L_b-L{ab})I

Ntatal=Nb−Nab=(Lb−Lab)I

N

t

a

t

a

l

N_{tatal}

Ntatal为称为支路b的有效电感、总电感或净电感

当相邻电流的方向相反时,如回路的两条文路中的一条是另一条的返回电流路径时有效电感决定了四路电流变化时支路两端感应电压的大小。如果这第二条支路是返回路径,则称在该返回路径上产生的电压为地弹。

返回路径上的地弹电压为:

V

g

b

=

L

t

o

t

a

l

d

I

d

t

=

(

L

b

−

L

a

b

)

I

V_{gb}=L_{total}\frac{dI}{dt}=(L_b-L{ab})I

Vgb=LtotaldtdI=(Lb−Lab)I

最小化返回路径上的电压降(地弹电压)有两种方法。

1、减小回路中的电流的变化速度。这意味着降低边沿的变化率,并限制共同用一个返回路径的信号路径数目,以及使用差分信令。我们很少有机会这样做。

2、减小

L

t

o

t

a

l

L_{total}

Ltotal。主要由两方面入手:减小支路的局部自感,增大两支路的局部互感。减小支路的局部自感意味着返回路径要尽可能的短,尽可能宽(也就是使用平面);增大支路的局部互感,就是支路与返回路径尽可能的靠近。(通过使用短而宽的互连以减小返回路径的局部自感,将电流及其返回路径尽量靠近以增大两支路之间的互感)

如果两条导线里流过的都是电源电流,即它们的电流方向相同,为了减小一条导线的净电感,要增大它们的间距。

在电源分配系统种中,减小任意一条支路净电感的常用设计规则是:尽可能让同向平行电流之间的问距大于它们的长度。即如果两条长度为100mil的相邻键合线,如果它们都是电源线,则线间距至少应为100mil。如果靠得近一点就会增加它们之间的互感,是的每条支路的净电感增大,从而导致导线的开关噪声增大。

对于过孔,由上可知,如果过孔之间的电流相同,则应保证过孔间距大于过孔长度,这样产生的互感会非常小;而如果过孔间的电流相反,则应该小于过孔长度。同时在同一个焊盘中,有多个过孔时,由于与电源、地平面的接触面积加大,进入电源、地平面的扩散电感将会减小。有时,这一点比减小过孔电感的效果更重要。

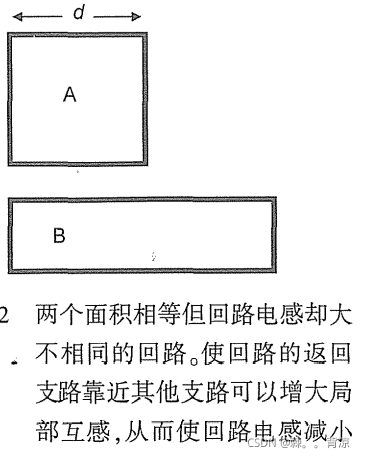

回路电感和回路互感

回路电感:完整电路回路产生的总电感。

回路自感:整个回路的自感。对于上诉回路,其回路自感为

L

l

o

o

p

=

L

a

−

L

a

b

+

L

b

−

L

a

b

=

L

a

+

L

b

−

2

L

a

b

L_{loop}=L_a-L_{ab}+L_{b}-L_{ab}=L_a+L_b-2L_{ab}

Lloop=La−Lab+Lb−Lab=La+Lb−2Lab

电源分配网络和回路电感

电源分配网络(PDN)的用途是在每个芯片的电源焊盘和地焊盘之间提供恒定的电压。在大多数的分配中,噪声的波动一般不超过5%,进入芯片的电流如果发生突变(如程序的执行等),则变化的电流流过电源分配网络的互连阻抗时就会引起电压降,被称为轨道下沉或轨道塌陷。

要使电流变化时引起的电压降最小,电源分配网络的串联阻抗就要小于一定的值,要使电源分配网络的阻抗比较小,有两条设计原则:低频时,添加具有低回路电感的去耦电容器;高频时,使去耦电容器和芯片焊盘之间的回路电感最小,以保持它们之间的阻抗低于一定的值。

大致估算一下去耦电容容量。

在电压下降的这段时间,电容器上有

Δ

Q

\Delta Q

ΔQ的电荷经芯片释放掉,其两端电压

Δ

V

\Delta V

ΔV下降为:

Δ

V

=

Δ

Q

C

\Delta V=\frac{\Delta Q}{C}

ΔV=CΔQ

假设芯片的平均功耗为P,则流过芯片的平均电流

I

=

P

/

V

I=P/V

I=P/V

芯片的去耦就是要维持一定的去耦时间

Δ

t

\Delta t

Δt, 其关系为:

P

/

V

=

Δ

Q

Δ

t

=

C

Δ

V

Δ

t

P/V=\frac{\Delta Q}{\Delta t}=\frac{C\Delta V}{\Delta t}

P/V=ΔtΔQ=ΔtCΔV

因为时以电压下降为5%来算,所以

Δ

V

=

0.05

V

\Delta V=0.05V

ΔV=0.05V

所以去耦时间为:

Δ

t

=

0.05

C

V

2

P

\Delta t=0.05C\frac{V^2}{P}

Δt=0.05CPV2,或者有

C

=

P

0.05

V

2

Δ

t

C=\frac{P}{0.05V^2}\Delta t

C=0.05V2PΔt

如果芯片的工作电压为3.3V,功率为1W,则需要的去耦电容总量为

C

=

2

Δ

t

C=2 \Delta t

C=2Δt,如果稳压器在10us内对电压变化来不及做出反应,就至少需要提供2*10=20uF的去耦。

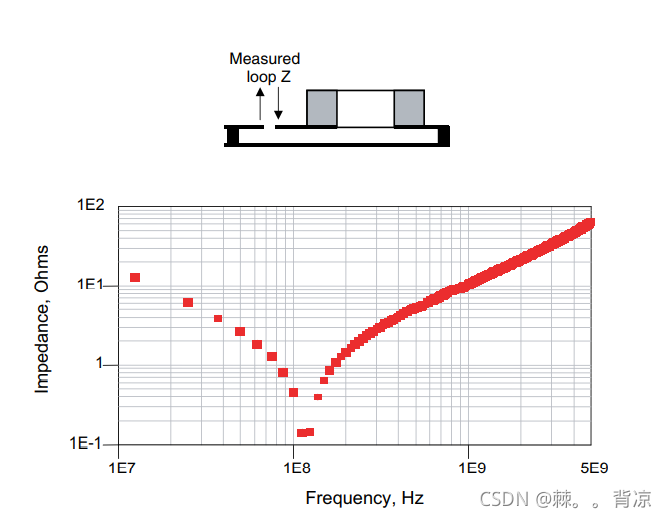

很多情况下,使用多个去耦电容,而不是使用一个大的去耦电容,原因是理想电容器的阻抗随着频率的升高而减小,但实际电容器的两端和芯片焊盘相连的那段线条会有相应的回路电感。该回路电感与理想电容元件相串联,导致实际电容器的阻抗随频率的升高而增大。

下图是0603封装的去耦电容阻抗和频率的关系。

从某一点起,串联的回路电感开始在阻抗中起主要作用,该点的频率称为自谐频率。所以到高频时,减小阻抗就需要减小回路电感,减小去耦电容器的回路电感的方法有下面几种:

1、使电源平面和地平面靠近电路板的表层,缩短过孔

2、使用尺寸小的电容器

3、电容器焊盘到过孔之间的连线要尽量短

4、多个电容器并联使用

如果某一去耦电容器的回路电感为2nH ,而容许的最大回路电感为 0.1 nH ,那么至少要并联20个电容器,所得的等效回路电感才能满足要求。

多个电感器的等效电感

对于两个局部电感的串联,其等效局部自感电感为

L

s

e

r

i

e

s

=

L

1

+

L

2

+

2

L

12

L_{series}=L1+L2+2L12

Lseries=L1+L2+2L12

当两个电感并联时,其等效局部自感为:

L

p

a

r

a

l

l

e

l

=

L

1

L

2

+

L

12

(

L

1

+

L

2

)

+

L

1

2

2

L

1

+

L

2

+

2

L

12

L_{parallel}=\frac{L1L2+L12(L1+L2)+L12^2}{L1+L2+2L12}

Lparallel=L1+L2+2L12L1L2+L12(L1+L2)+L122

当局部互感为零且局部自感相同时,串联的等效电感时其中一个局部自感的2倍,并联的等效电感是其中一个局部自感的1/2.

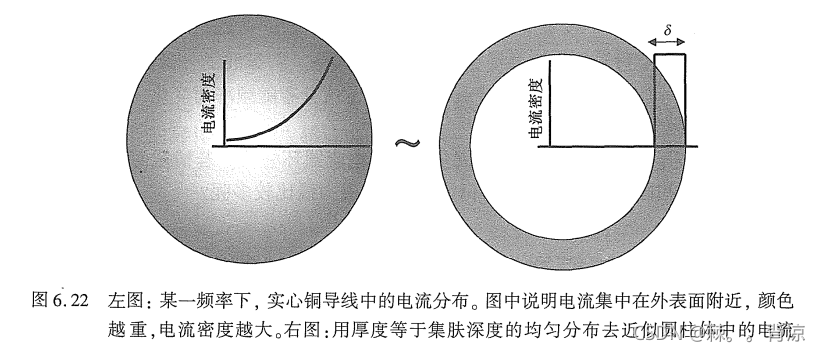

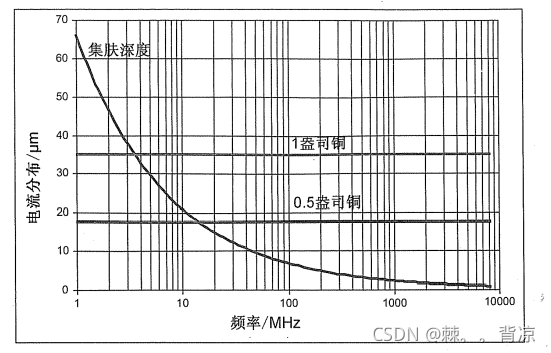

电流分布及集肤深度

在实际中,直流电流在导线中是均匀分布的,而交流电流不是均匀分布的。在交流中,电流看作是正弦波,其任何评率的分量都是沿最低的阻抗路径传播的,电感最大的电流路径,其阻抗也最大;而随着频率的升高,高电感的路径的阻抗会变得更大,所以此时电流倾向于选择电感较低的路径,即趋向于外表面的路径。

在高频时,所有电流会趋向于导线表面那一薄层。

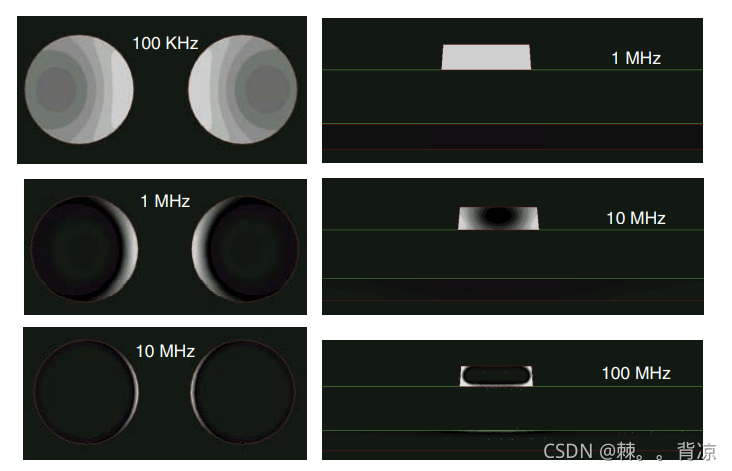

下图时圆柱体中电流分布的近似:

在这种几何结构中,可以把电流层近似成固定厚度

δ

\delta

δ的均匀分布,并称该厚度为集肤深度,表示为:

δ

=

1

σ

π

μ

0

μ

r

f

\delta =\sqrt{\frac{1}{\sigma\pi\mu_0\mu_rf}}

δ=σπμ0μrf1

δ

\delta

δ=集肤深度(cm);

σ

\sigma

σ=金属的电导率(S/m);

μ

0

\mu_0

μ0=自由空间的磁导率;

μ

r

\mu_r

μr=相对磁导率;

f

f

f=频率;

铜的集肤近似为:

δ

=

66

1

f

\delta =66\sqrt{\frac{1}{f}}

δ=66f1

单位为um,

f

f

f为正弦波频率为MHz。

这里有一个经验法则::当电路板上的铜线为1盎司或者几何厚度为 34μm时,若频率大于等于 10 MHz ,则导线中的电流不再占用线条的整个横截面,趋肤效应在电流分布中起主导作用。

当频率较低时,集肤深度大于导线截面的几何厚度,此时可以任务电流时均匀分布的。当集肤深度小于横截面的几何厚度时,随着频率的升高,电流流过的横截面积随频率的平方根成比例减小,从而使导线的单位长度电阻随频率的平方根成比例增大。

上图是3种不同频率时直径为 20 mil 的导线和1盎司销微带线中的电流分布,其中颜色越淡,电流密度越高。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?