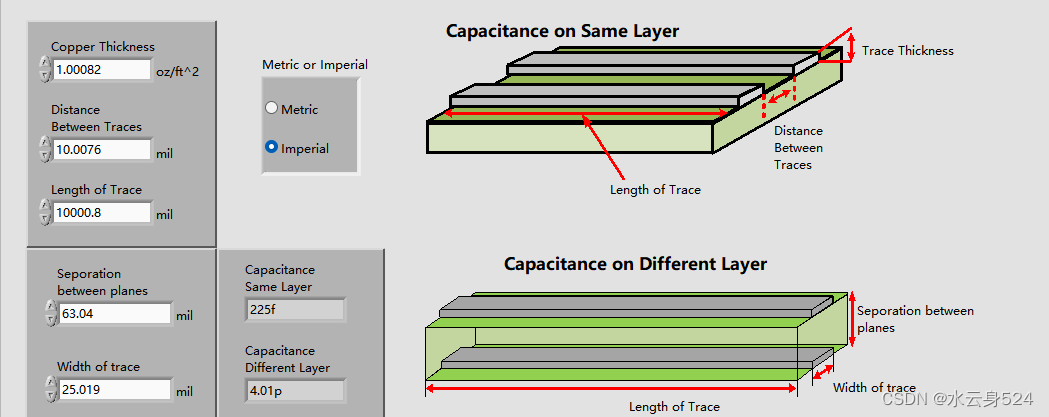

1.导线与导线之间的寄生电容

导线之间的寄生电容由两导线之间的平行面积与距离决定,分为同一层和不同层之间的寄生电容

同层导线寄生电容取决于平行线长度和间距和铜箔厚度

不同层导线寄生电容取决于平行线重合的线宽和两层间距

假设走线铜厚为1盎司,两层铜箔间距为1.6mm(63mil),同一层两导线平行长度为1000mil,线距为10mil

线宽也是10mil的情况下

由上图可知,同层导线寄生电容为22.5f法,相邻层导线寄生电容为161f法

2.导线与铺铜的寄生电容

该寄生电容的计算方式与导线和导线之间一致,在设计因为经常大面积铺铜,所以导线与铜之间的寄生电容产生的更加普遍。假设一根导线长度10000mil,其相邻层全铺铜,该寄生电容为信号线与地之间的电容

则寄生电容达到了4pf

3.导线的寄生电感

影响寄生电感的产数有:铜厚,线宽,线长。对寄生电感影响最大的是线长L,将L的长度缩短是减小信号线寄生电感的最有效方法。

导线电感可大概计算为 大约1000mil有5.076nH寄生电感

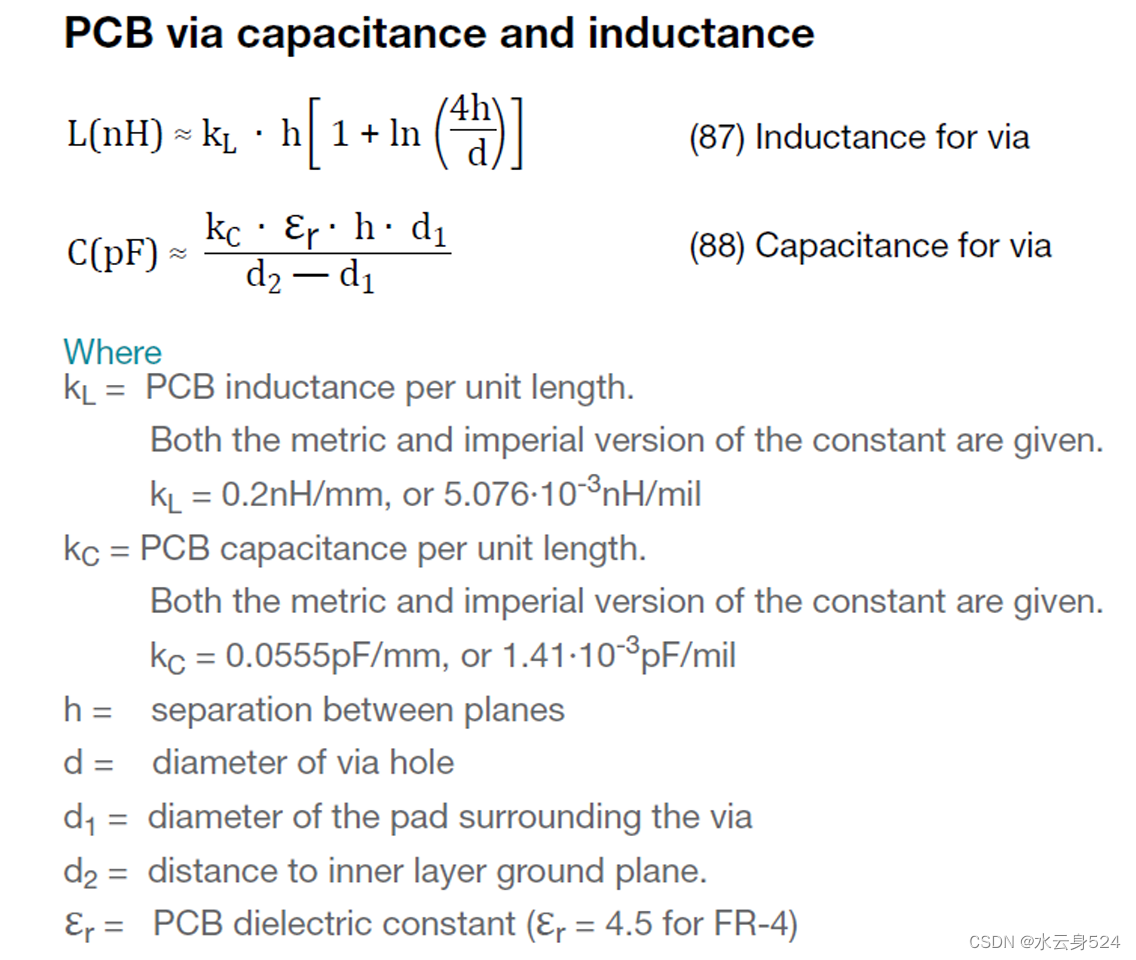

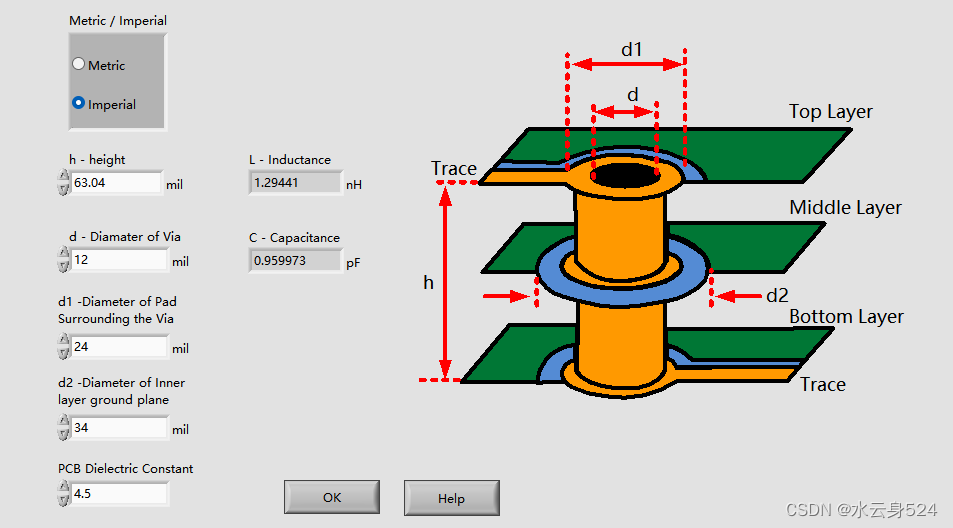

4.过孔的寄生电容与寄生电感

过孔的寄生电容主要取决于过孔外直径,层高和铺的地铜围孔的直径,过孔外直径越大,层高越高,铺的地铜围孔的直径越小,寄生电容越大

过孔的寄生电感主要取决于孔内径,层高,层高越高,孔内径越小,寄生电感越小

假设层高1.6mm(63mil),孔内径为12mil,孔外径为24mil,铺的地铜围孔的直径为34mil,下图为计算的寄生电容和寄生电感

本文详细分析了导线间的寄生电容,包括同层和不同层的情况,以及导线与铺铜的电容。还讨论了导线的寄生电感,强调了线长对其的影响,以及过孔的寄生电容和电感,以电子电路设计中这些关键参数为例进行计算。

本文详细分析了导线间的寄生电容,包括同层和不同层的情况,以及导线与铺铜的电容。还讨论了导线的寄生电感,强调了线长对其的影响,以及过孔的寄生电容和电感,以电子电路设计中这些关键参数为例进行计算。

1100

1100

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?