【FPGA开发】–Moore 型和 Mealy型状态机

摘要:关于Moore 型和 Mealy型状态机的详细说明,读者可以自行查阅书籍或者上网查找,本文不做详细描述。本文主要通过一个序列检测器的状态机来说明Moore 型和 Mealy型状态机基本设计方法,并对两种状态机进行简单对比说明。

NO.1状态机的基本知识点

1、状态机的分类

①根据状态机的状态数是否为有限个:

有限状态机(FSM)、无限状态机(ISM)

②根据输出与现态以及输入的关系:

Moore型状态机、Mealy型状态机

Moore型状态机输出仅取决于状态;

Mealy型状态机输出取决于输入和状态。

2、状态机的状态编码

编码原则:

Binary-code和Gray-code适用于触发器资源较少,组合电路资源丰富的情况(CPLD);对于FPGA等触发器资源丰富的器件,使用one-hot-code较合适,这样不但充分利用FPGA丰富的触发器资源,还因为只需比较1bit,速度快,组合电路简单。

3、状态机的描述方法

★单进程(一段式)FSM描述方法

将整个状态机的三个模块合并起来,写到一个进程里面,在该进程中同时描述状态的寄存和次态逻辑和输出逻辑;

★两进程(二段式)FSM描述方法

用2个进程来描述状态机,其中当前状态寄存逻辑用一个同步时序进程描述,输出逻辑和次态逻辑合并起来用一个组合逻辑进程来描述;

★三进程(三段式)FSM描述方法

将状态机的3个模块用3个进程来描述,一个同步时序进程描述当前状态寄存逻辑,一个组合逻辑进程描述次态逻辑,一个进程来描述输出逻辑;

注意:

①三段式状态机并非指只有三个always块,当电路复杂时可以有多个always块;

②三段式状态机的输出逻辑可以用组合逻辑,也可以用时序逻辑。当使用组合逻辑时,判断条件是current_state,此时输出可能有毛刺,为了滤除毛刺,要用触发器进行同步,所以会使得输出有一个时钟的延时;当用时序逻辑时,为了不延时一个时钟周期,判断条件是next_state,此时输出是同步电路,没有毛刺;

③三段式状态机中描述次态逻辑的部分是组合逻辑,判断条件是current_state。

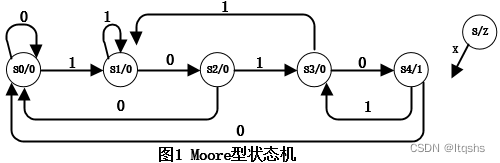

NO.2Moore型状态机设计之“1010”序列检测器

1、状态转换图

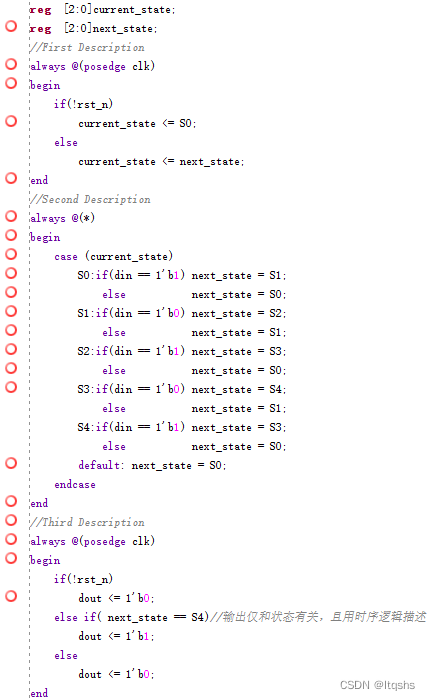

2、关键代码

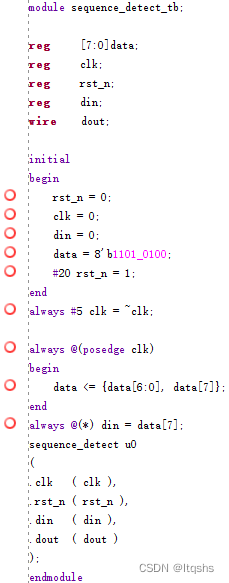

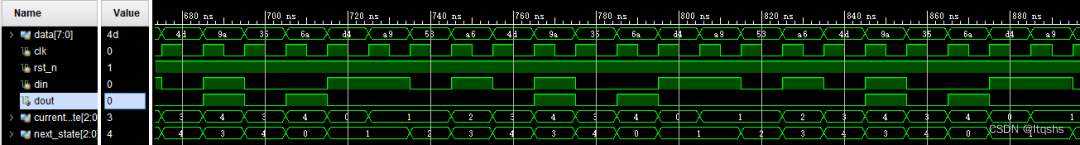

3、仿真验证

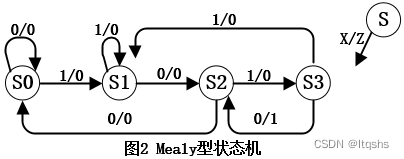

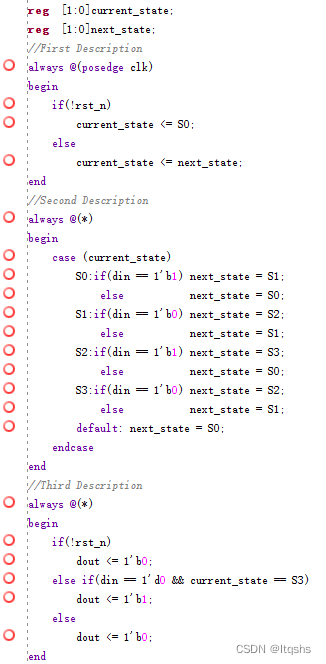

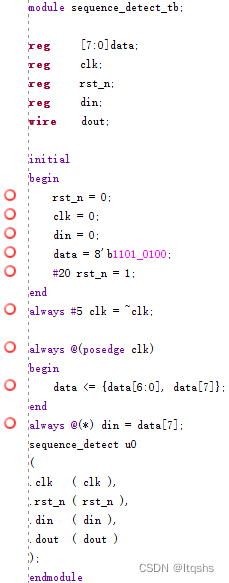

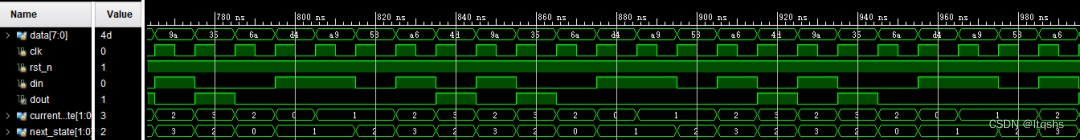

NO.3Mealy型状态机设计之“1010”序列检测器

1、状态转换图

2、关键代码

3、仿真验证

NO.4对比分析

1、Moore型的输出与时钟是同步的,因为它仅是状态的函数,从而只有当状态改变时输出才可能改变。这就保了Moore型输出波形更加“洁净”。

2、Mealy型输出会随着输入的变化而变化,这既是它的缺点也是它的优点,设计者可通过输入信号对状态机的输出信号实施控制。

3、Mealy型状态机比Moore状态机所需要的状态个数少,这就意味着所需要的触发器个数少,电路更简单,成本更低廉。

4、就本文所的“1010”序列检测器而言,Moore的输出比Mealy的输出会有一个时钟的时延。

4537

4537

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?