编译BD出错描述

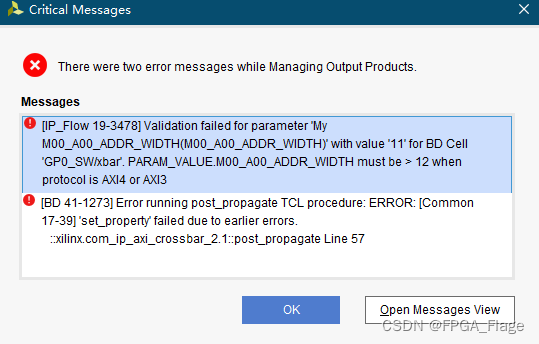

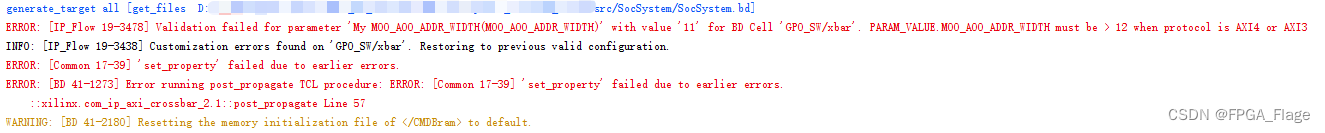

在开发ZYNQ的PL部分时,编译所设计的Block Design时出现[IP_Flow 19-3478]错误,详细错误为:

- [IP_Flow 19-3478] Validation failed for parameter ‘My M00_A00_ADDR_WIDTH(M00_A00_ADDR_WIDTH)’ with value ‘11’ for BD Cell ‘GP0_SW/xbar’. PARAM_VALUE.M00_A00_ADDR_WIDTH must be > 12 when protocol is AXI4 or AXI3;

- [BD 41-1273] Error running post_propagate TCL procedure: ERROR: [Common 17-39] ‘set_property’ failed due to earlier errors.::xilinx.com_ip_axi_crossbar_2.1::post_propagate Line 57。

具体报错如图所示:

编译环境

- 软件:Vivado 2019.2

- 运行环境:Windows10

- 工程芯片:xc7z035ffg900-2

原因分析

在报错图片中有说到参数无效, [IP_Flow 19-3478] Validation failed for parameter ‘My M00_A00_ADDR_WIDTH(M00_A00_ADDR_WIDTH)’ with value ‘11’ for BD Cell ‘GP0_SW/xbar’. PARAM_VALUE.M00_A00_ADDR_WIDTH must be > 12 when protocol is AXI4 or AXI3。

而参数无效的原因是:M00_A00_ADDR_WIDTH 必须为12,但是设计中的位宽为11,因此找到错误的AXI总线,将其地址深度改到不低于12位位宽的深度。

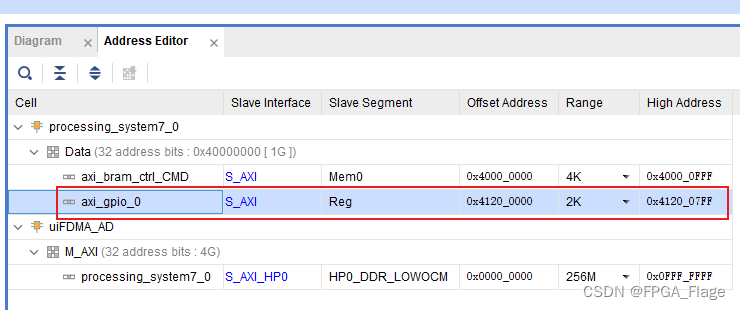

打开BD设计界面中的Address Editor选项卡,如图所示

从上图表红色框所知,axi_gpio_0 的深度为 2K(注意:这里的单位为Byte);因此axi_gpio_0总线位宽为11位就能表示该范围(2K = 211 = 2048);由此可以得出只要将范围设置为4K即可消除该错误。

解决方法

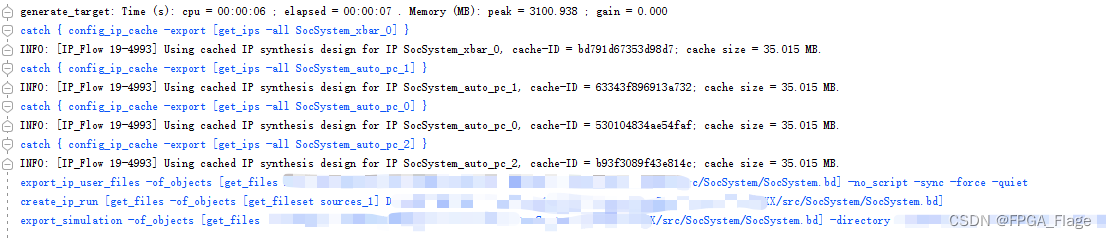

由上面原因分析可知:只要将上面的AXI 总线范围修改为4K即可消除此错误,如图所示:

保存

→

\rightarrow

→ 编译BD设计文件;编译结果

总结

由此可以总结:AXI总线地址是以4K对齐。

8934

8934

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?