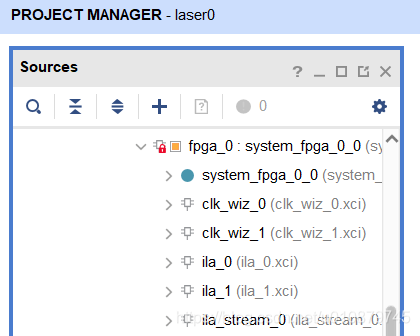

subsystem IP核是只读文件,无法修改,下面是本人苦战数日,研究出的方法,分享给大家。

前面是不成功的尝试,最后部分是成功的经验,没时间,可跳过前面的内容。

尝试方法如下,均告失败。

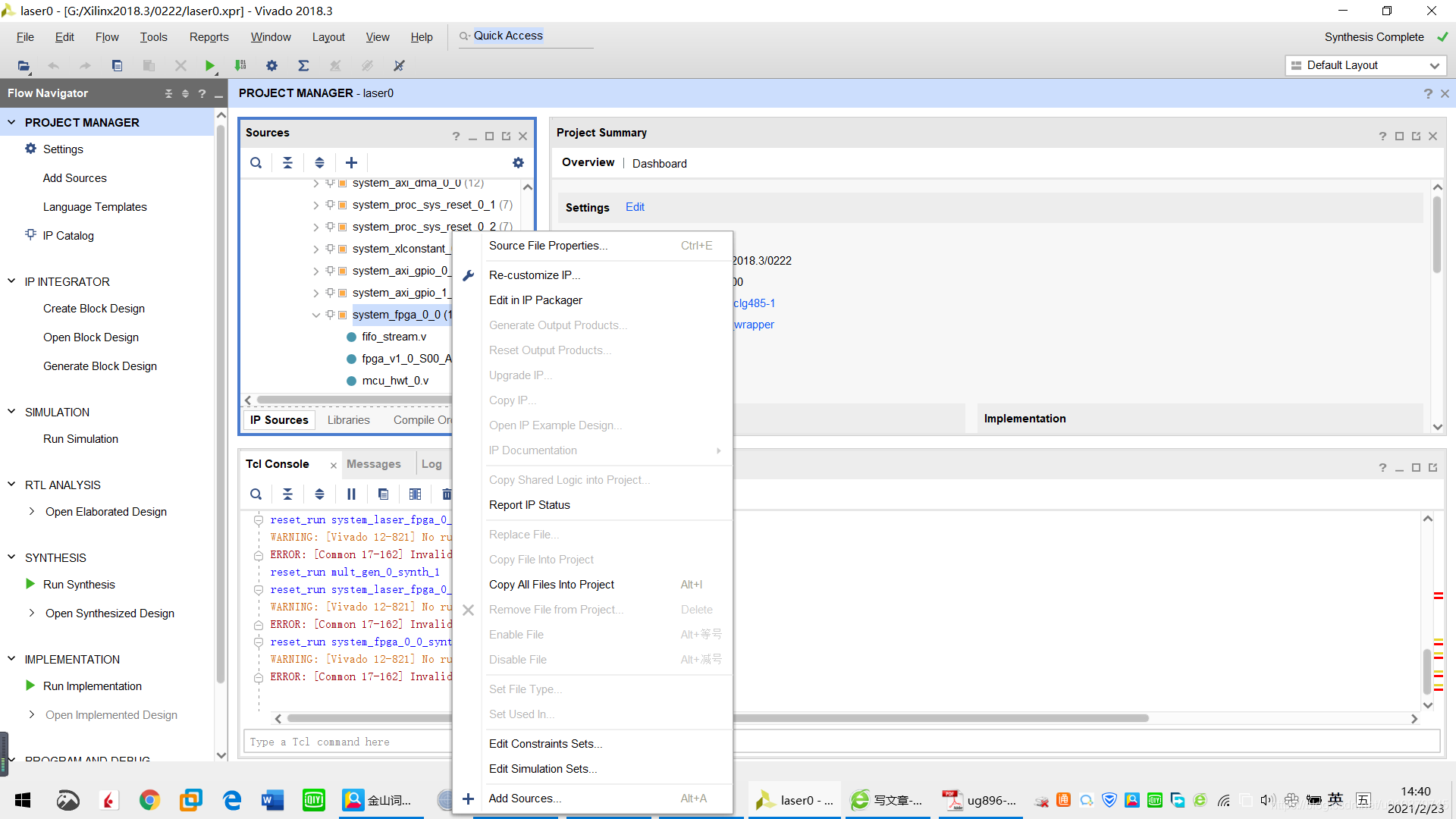

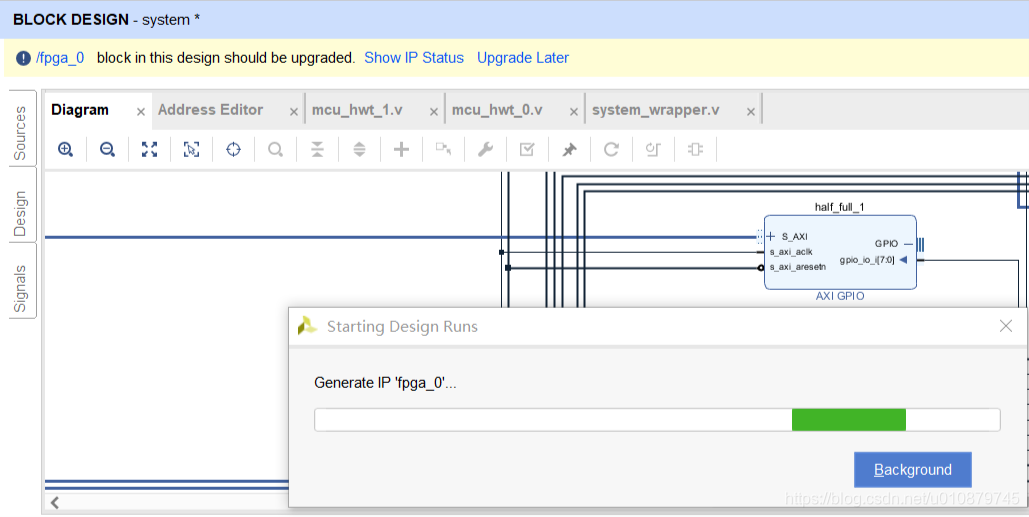

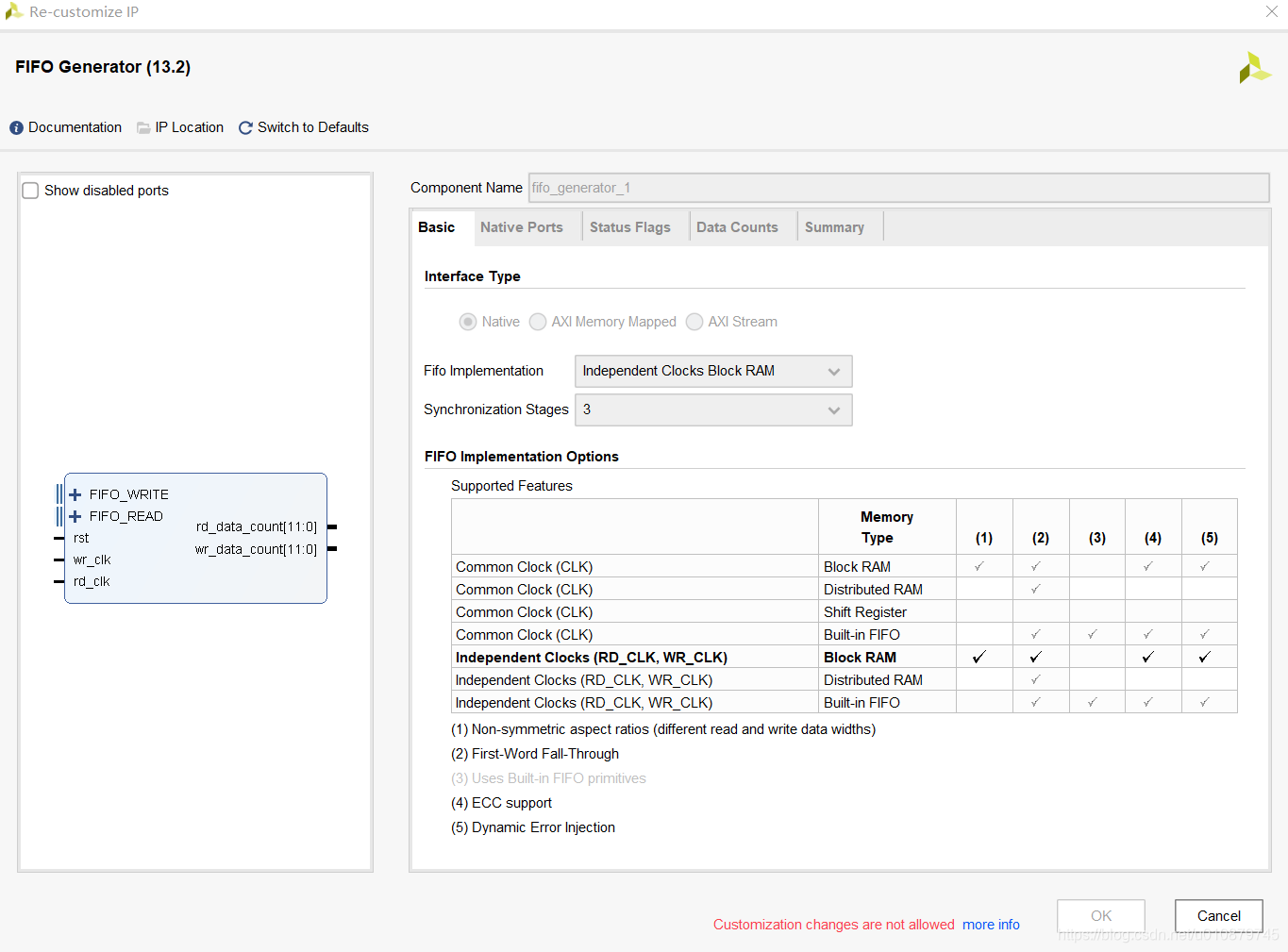

1、Re-Customizing Existing IP, 再定制,不允许 。

2、只读文件,外面强行改,编译不认。

3、大量博客改set_property IS_MANAGED,因是定制IP,又属于BD,也不让改。

4、清cache, 同样没用,config_ip_cache -clear_output_repo。

5、查到所谓的AR# 57546: Vivado IP Flows - How to modify/edit IP core source files in Vivado? https://www.xilinx.com/support/answers/57546.html,一堆复杂神操作,先搁置未用。

6、今天尝试Edit IP, 似乎成功,但一堆错,查查查 。

尝试一,直接重定制,失败

这上一层就没有BD可以修改,该提示没有任何意义。

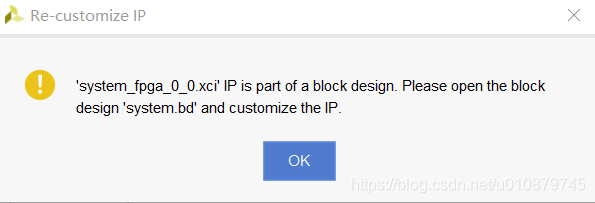

尝试二、用Vivado Design Suite User Guide Designing with IP UG896 (v2018.2) 109页 Editing Subsystem IP,仍失败

用另一编辑器

尝试运行复位和运行命令:

reset_run <ip_name>_synth_1

launch_run <ip_name>_synth_1

查ip_name

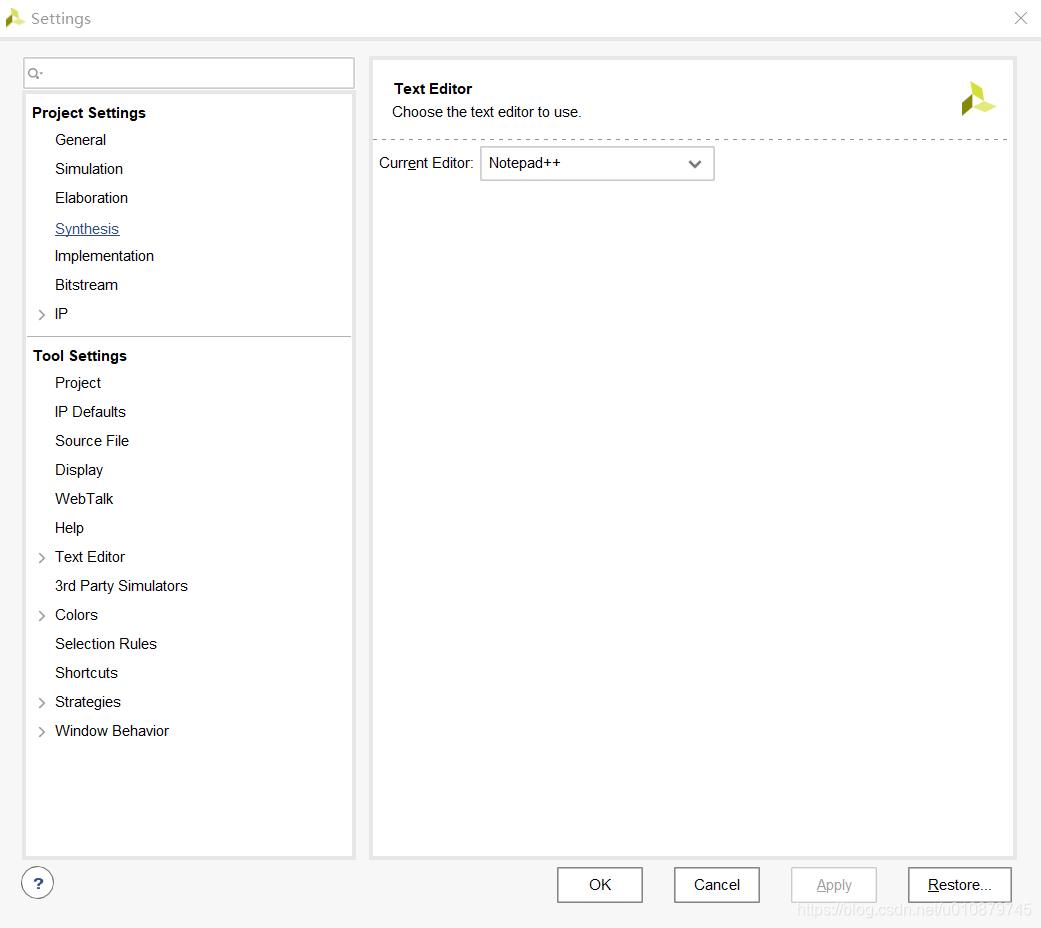

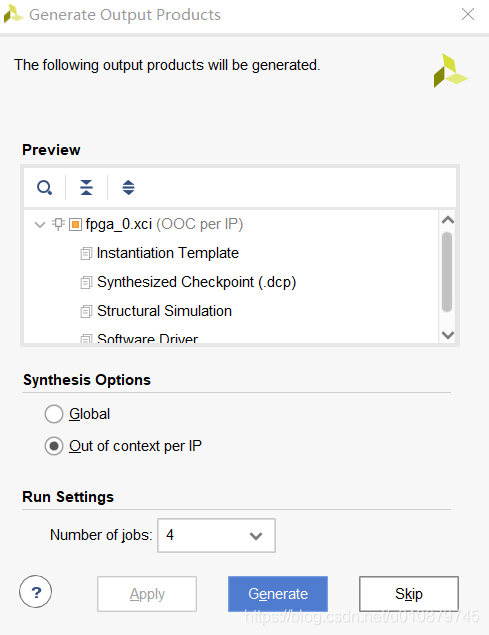

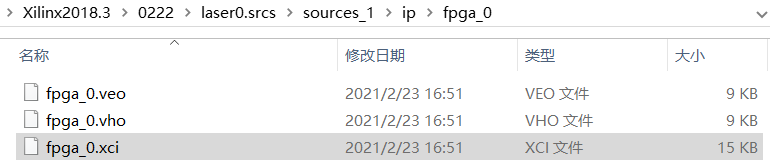

By default, the output products for an IP are written to the local project directory, at <project_name>.srcs/sources_1/ip/<ip_name>

有些成功,有些失败。

尝试三、用Vivado Design Suite User Guide Designing with IP UG896 (v2018.2) 109页 Editing IP Sources, 仍失败

set_property IS_MANAGED false [get_files <IP_NAME>.xci]

set_property IS_MANAGED false [get_files fpga_0.xci]

//可能同样有用 Tcl Command to Disable OOC Options on IP

//set_property GENERATE_SYNTH_CHECKPOINT FALSE [get_ips <ip_name>]

reset_run <ip_name>_synth_1

reset_run fpga_0_synth_1

launch_run <ip_name>_synth_1

launch_run fpga_0_synth_1

虽然你可以找到DCP文件,但删掉后综合会报警

INFO: [Project 1-454] Reading design checkpoint ‘g:/Xilinx2018.3/0222/laser0.srcs/sources_1/bd/system/ip/system_fpga_0_0/system_fpga_0_0.dcp’ for cell ‘system_i/fpga_0’

尝试四、清cache, config_ip_cache -clear_output_repo, 仍失败

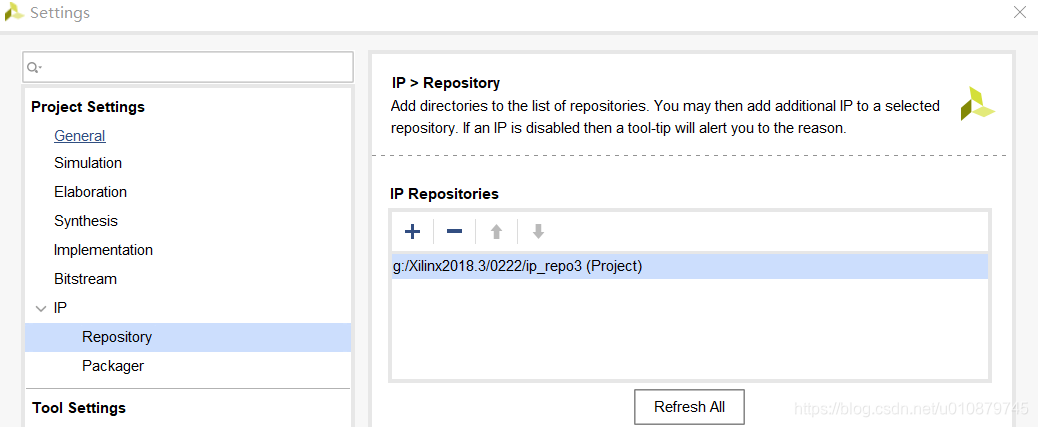

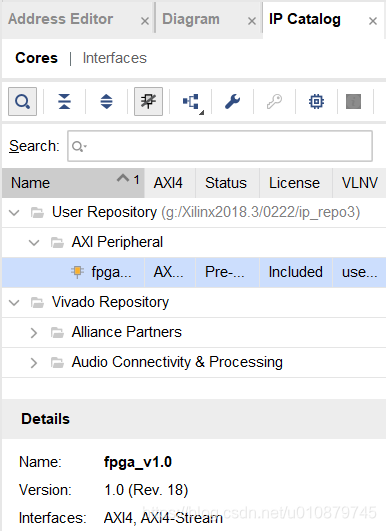

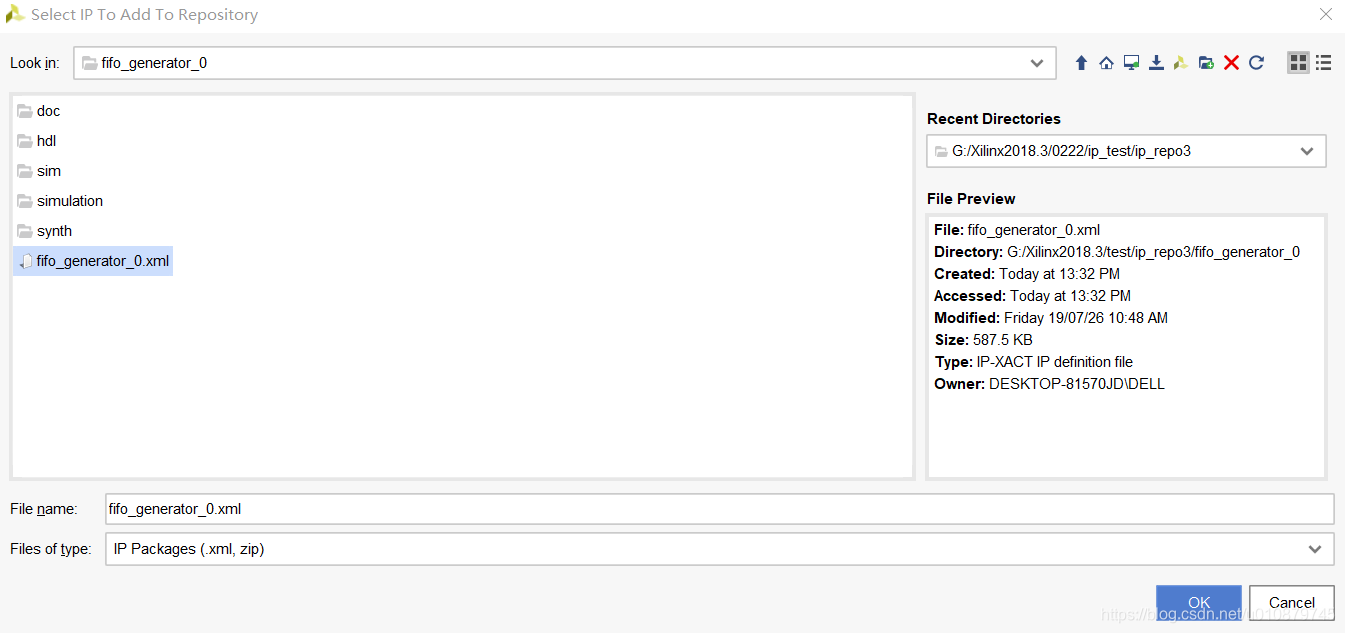

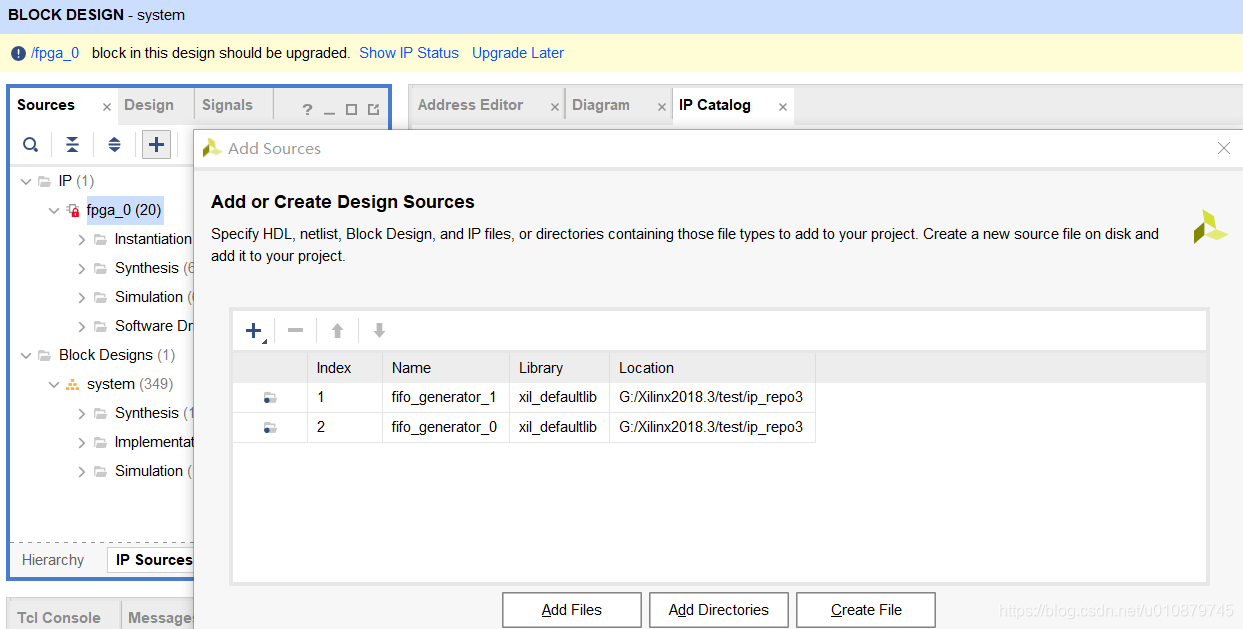

尝试五、用IP Repositories引入修改的IP,失败

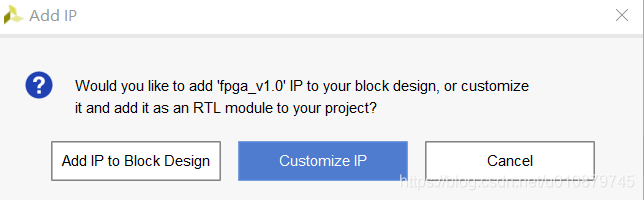

双击fpga_v1.0, 选择图形式加入,让系统自己去例化

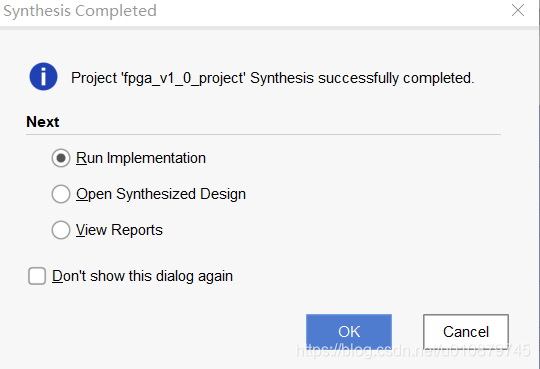

double click OK

G:\Xilinx2018.3\0222\laser0.srcs\sources_1\ip文件夹里面的内容是自动产生的,不要修改

仍无法实现用户管理

set_property IS_MANAGED false [get_files system_fpga_0_0.xci]

ERROR: [filemgmt 56-10] Setting is_managed is not permitted for the source file ‘G:/Xilinx2018.3/0222/laser0.srcs/sources_1/bd/system/ip/system_fpga_0_0/system_fpga_0_0.xci’ because its parent is managed. Unmanage the parent source file first.

set_property IS_MANAGED false [get_files fpga_0.xci]

ERROR: [IP_Flow 19-3666] The is_managed property cannot be directly modified for hierarchical IP.

ERROR: [Common 17-39] ‘set_property’ failed due to earlier errors.

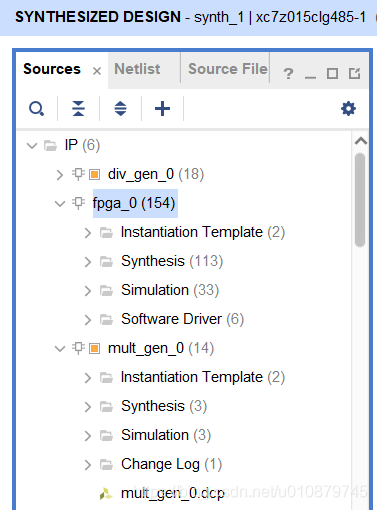

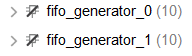

系统自带则可修改

set_property IS_MANAGED true [get_files fifo_generator_0.xci]

不是新的源文件,仍是原来结果

尝试六、做一个可以忽略的改动后重置综合,结果依旧是未修改的原结果

upgrade_ip [get_ips cfifo] -log c:/prj/IP/cfifo_upgrade.log

report_property [get_ips char_fifo]

CONFIG.core_clk.FREQ_HZ: Applicable when using a common clock (this

example)

° CONFIG.read_clk.FREQ_HZ: Applicable when using independent clocks

° CONFIG.write_clk.FREQ_HZ: Applicable when using independent clocks

set_property CONFIG.core_clk.FREQ_HZ 250000000 [get_ips char_fifo]

set_max_delay –from [get_cells data_reg] –to [get_cells synchro_stage0_reg]\ –

datapath_only [get_property PERIOD [get_clocks –of_objects [get_ports ref_clk]]]

The Vivado Design Suite User Guide: Using Constraints (UG903) [Ref 24]

Execute the following in the Tcl Console to reset the run:

reset_run <ip_name>_synth_1

d. Re-launch the run using the following command in the Tcl Console:

launch_run <ip_name>_synth_1

The Tcl command required to reset the and regenerate the output products are as follows:

• reset_target:

reset_target all

[get_files /project_1/project_1.srcs/sources_1/ip/<core_name>.xci]

• generate_target:

generate_target all

[get_files project_1/project_1.srcs/sources_1/ip/<core_name>.xci]

as described at this link in the Vivado Design Suite User

Guide: System-Level Design Entry (UG895).

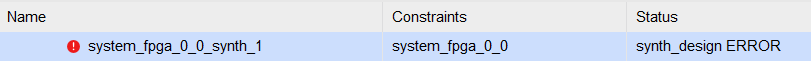

reset_run system_fpga_0_0_synth_1

launch_run system_fpga_0_0_synth_1

无法用户管理

set_property IS_MANAGED false [get_files system_fpga_0_0.xci]

ERROR: [filemgmt 56-10] Setting is_managed is not permitted for the source file ‘G:/Xilinx2018.3/test/laser0.srcs/sources_1/bd/system/ip/system_fpga_0_0/system_fpga_0_0.xci’ because its parent is managed. Unmanage the parent source file first.

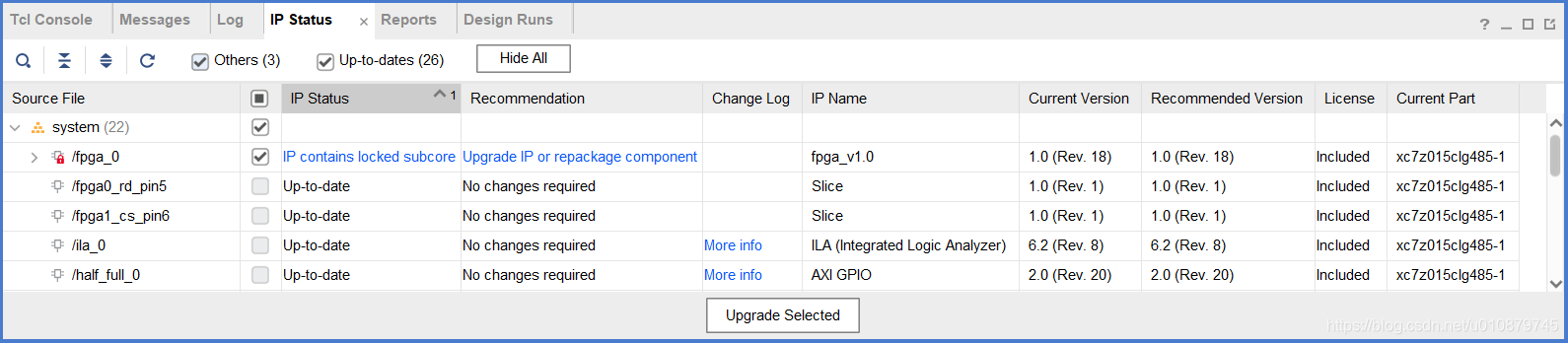

但可以锁定文件

get_property IS_LOCKED [get_files system_fpga_0_0.xci]

0

set_property IS_LOCKED true [get_files system_fpga_0_0.xci]

get_property IS_LOCKED [get_files system_fpga_0_0.xci]

1

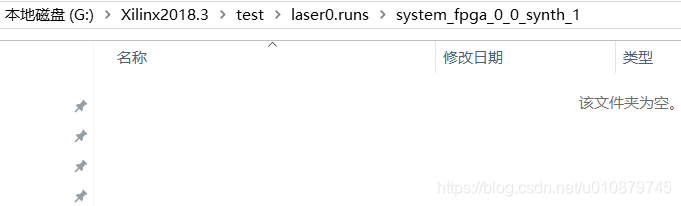

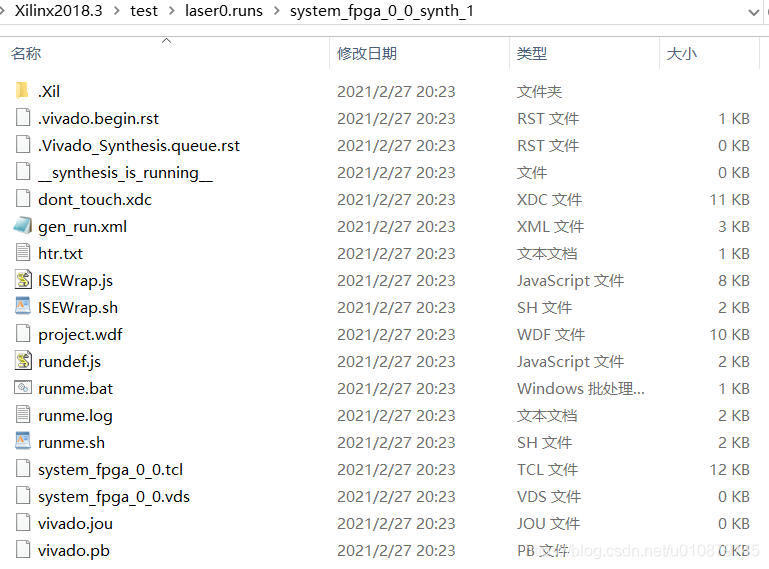

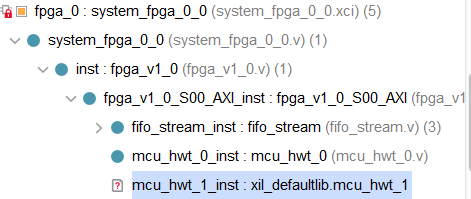

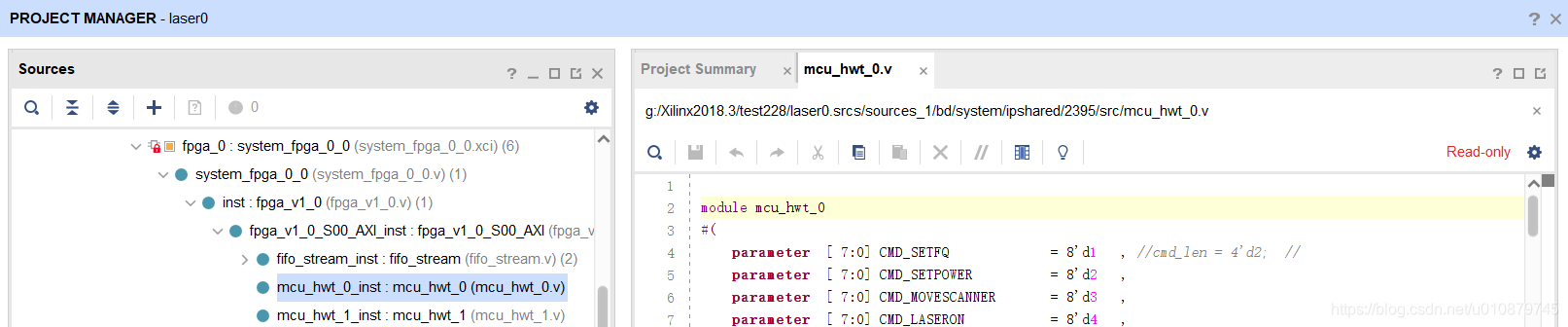

即使删掉文件,如下图,仍能正常编译

从源文件Tab看到该文件呈?

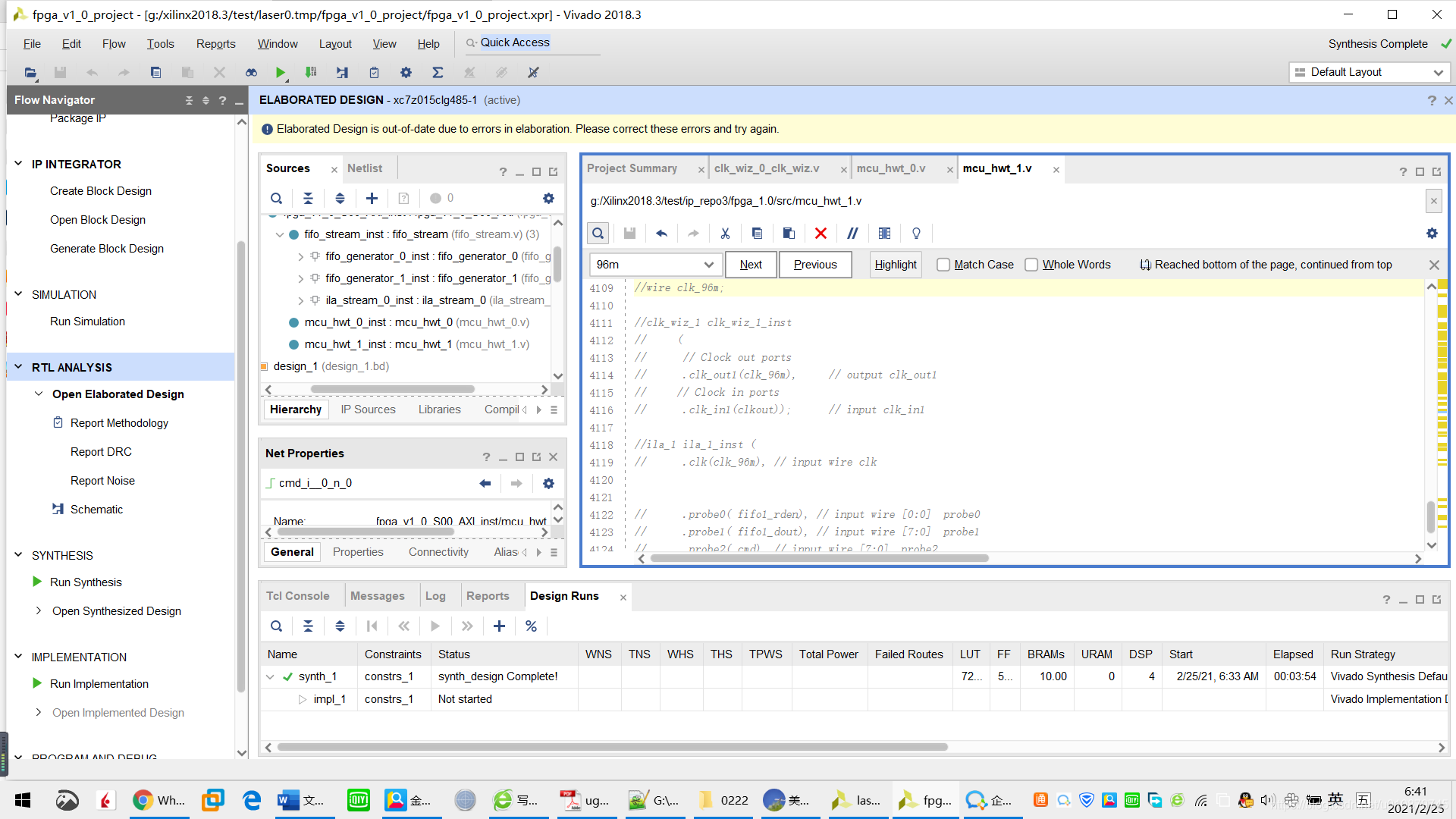

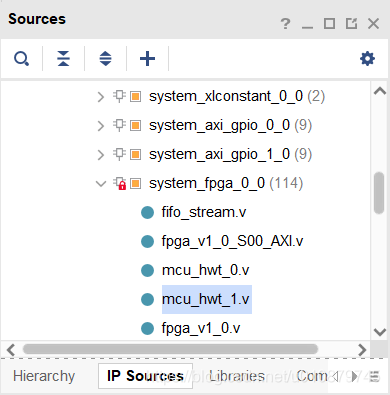

如果把system_fpga_0_0锁定,程序先找 mcu_hwt_1.v,再找这个 system_fpga_0_0.v

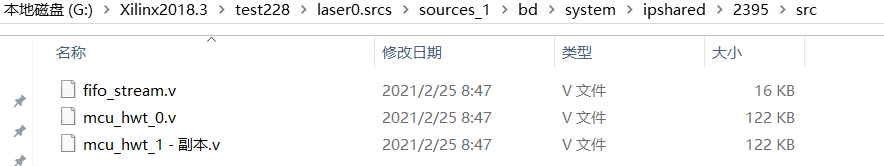

[Runs 36-287] File does not exist or is not accessible:‘g:/Xilinx2018.3/test228/laser0.srcs/sources_1/bd/system/ipshared/2395/src/mcu_hwt_1.v’

[Runs 36-287] File does not exist or is not accessible:‘g:/Xilinx2018.3/test228/laser0.srcs/sources_1/bd/system/ip/system_fpga_0_0/synth/system_fpga_0_0.v’

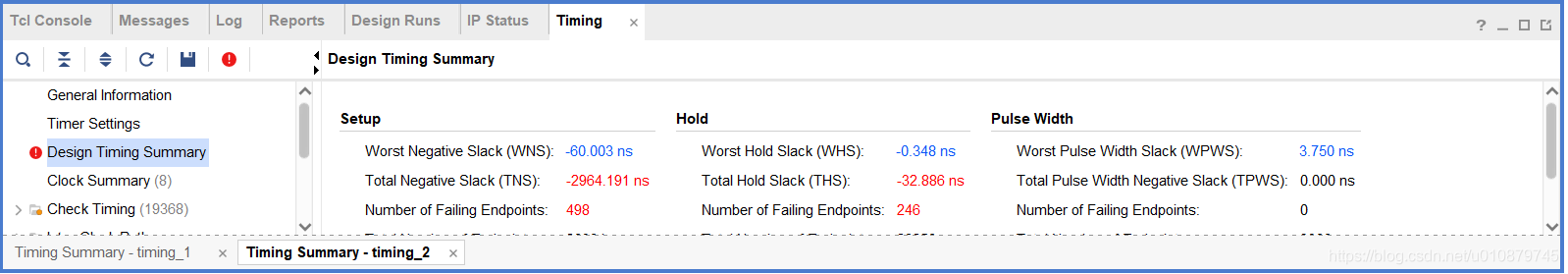

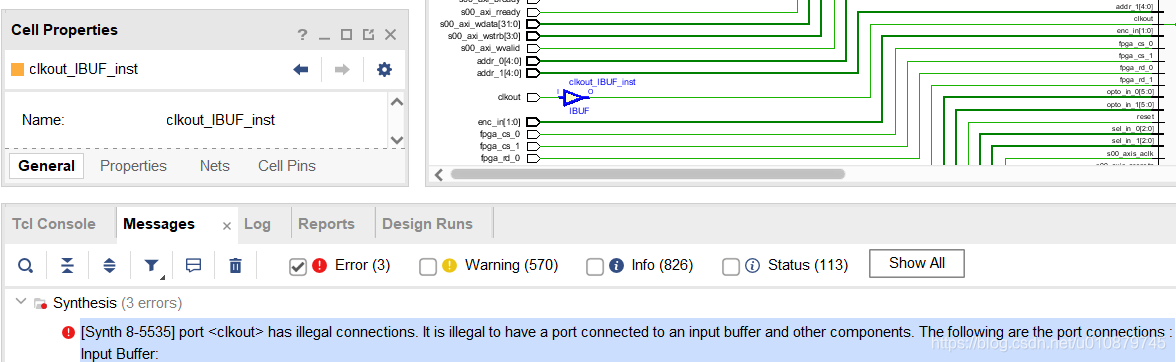

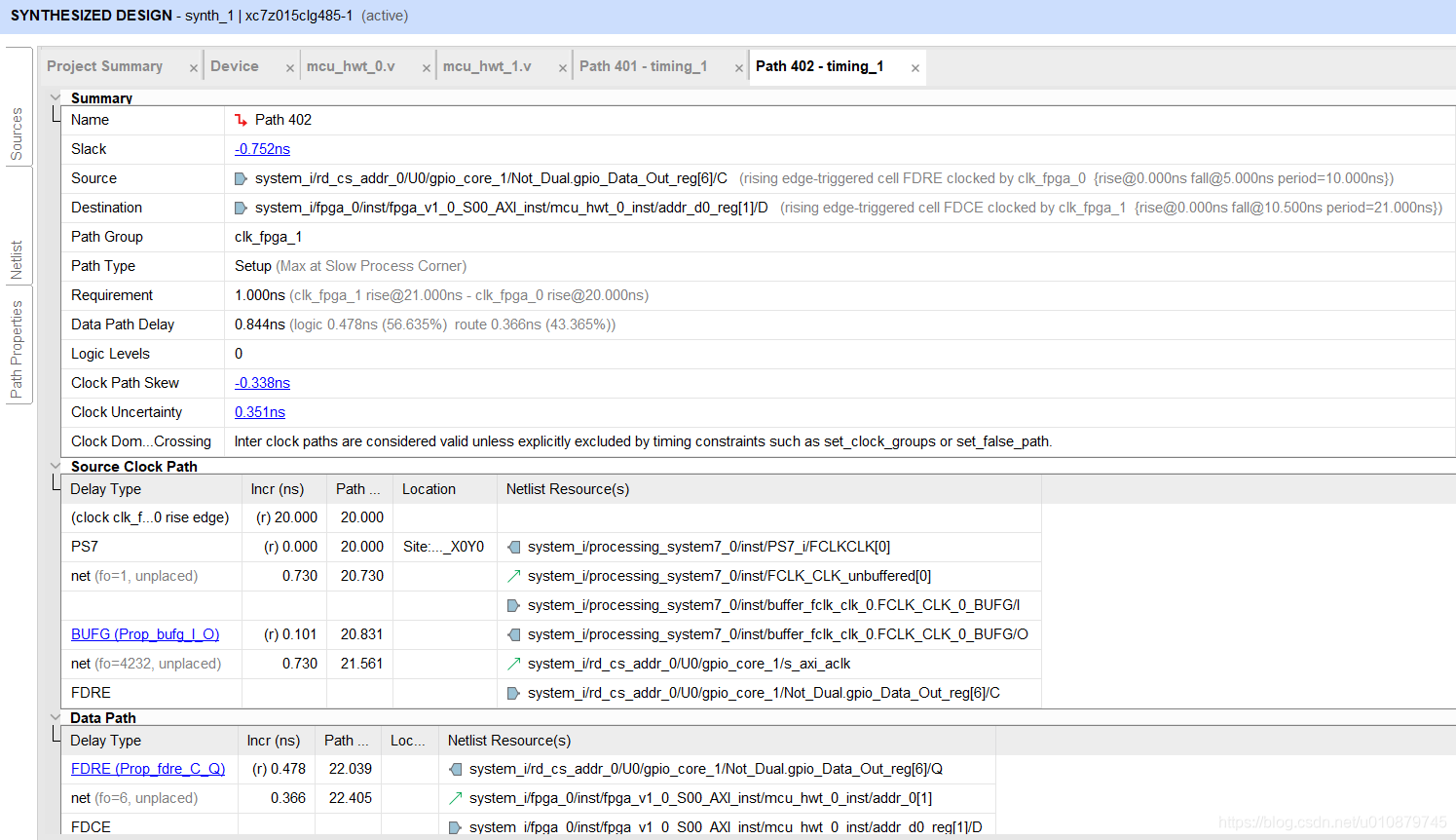

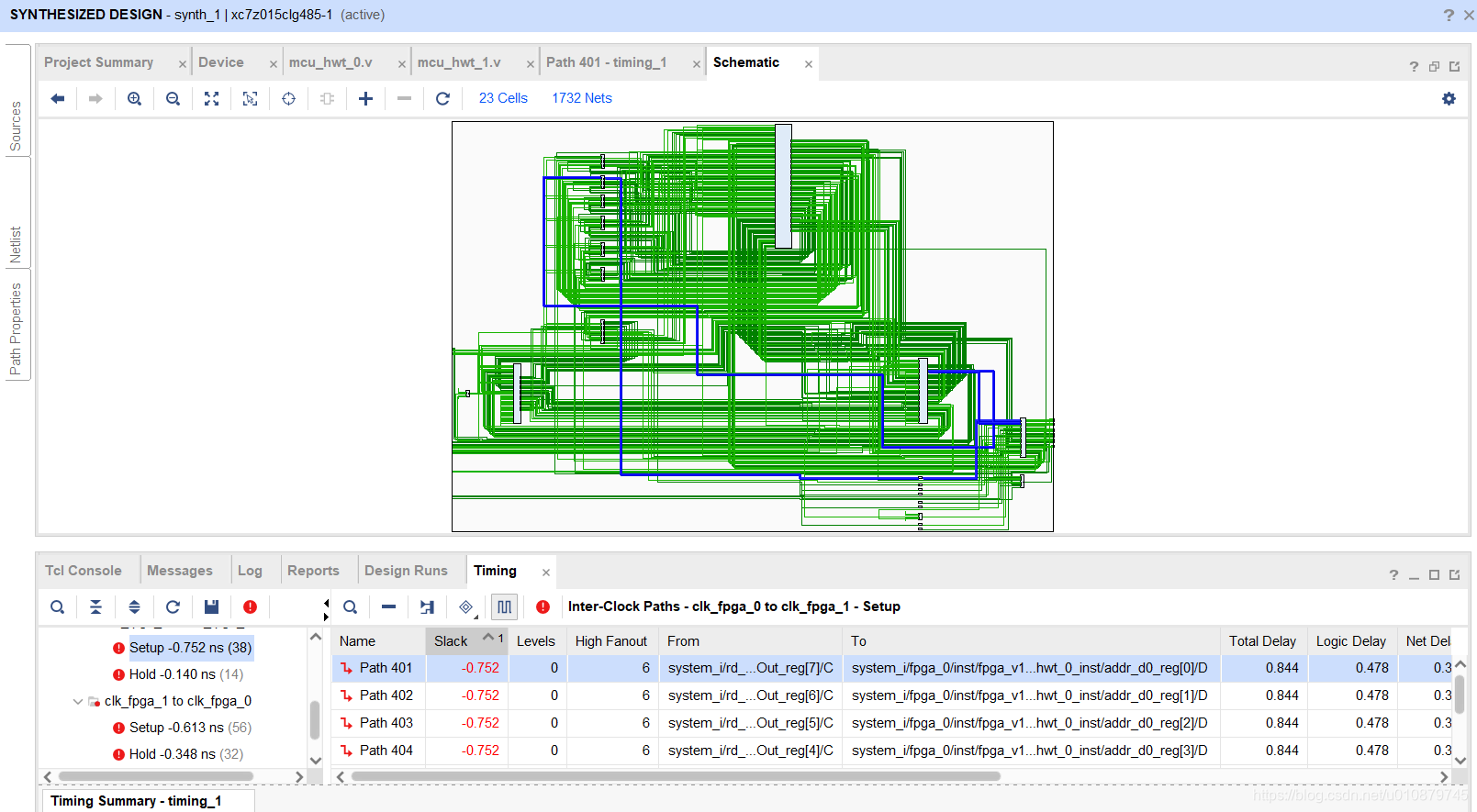

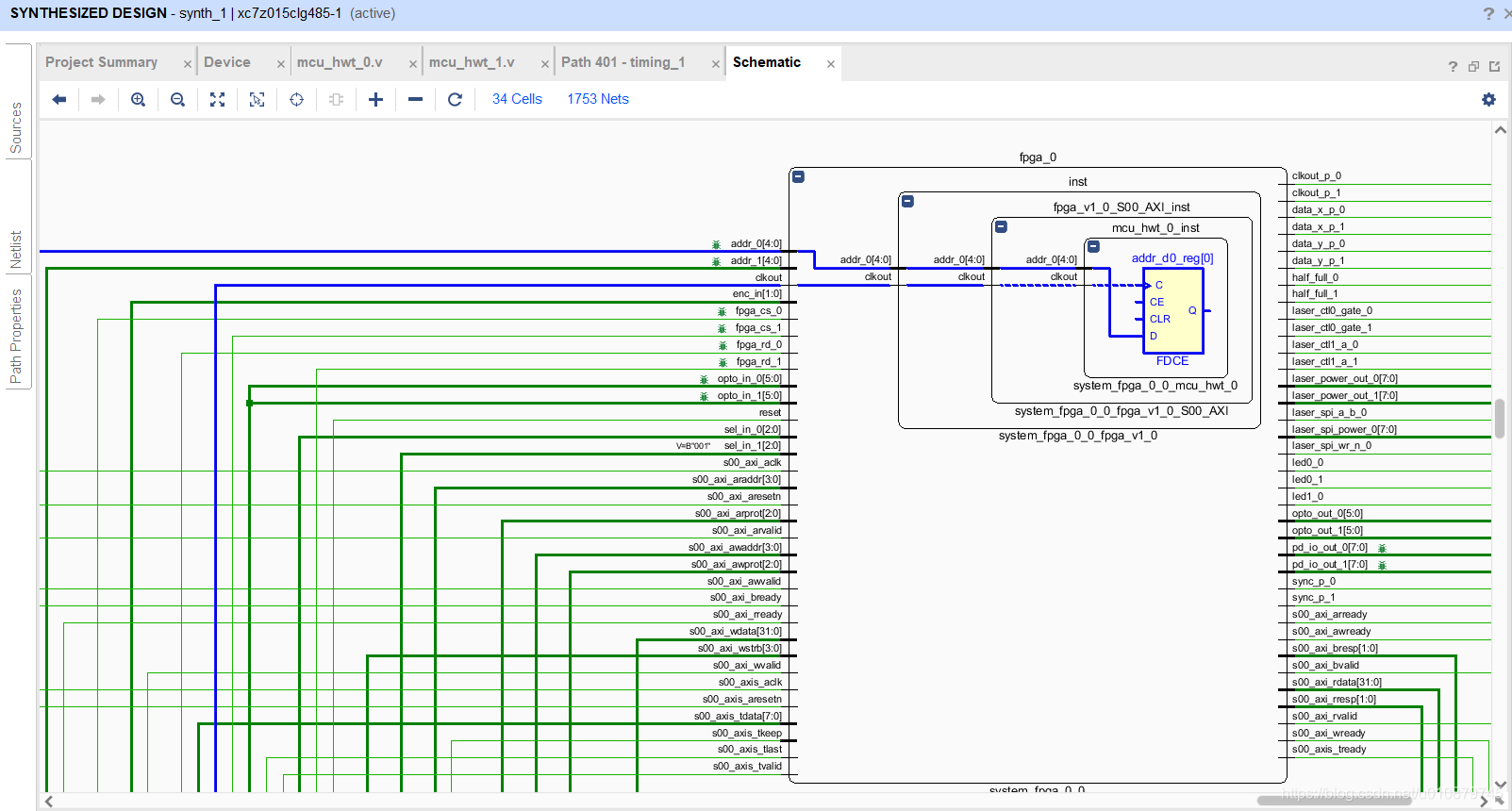

从下图看出,时序违例现发生在FPGA的地址选码上,地址信号是A9发来的,而接收时钟则是48M,是异步时间,不应该分析。

Vivado Design Suite: Creating and Packaging Custom IP (UG1118) [Ref 37] for more information about using the packaging feature.

Vivado Design Suite Tutorial: Creating and Packaging Custom IP (UG1119) [Ref 38]

The Vivado Design Suite Tutorial: Designing with IP (UG939) [Ref 32]

provides instruction on how to use Xilinx IP in Vivado.Vivado Design Suite User Guide:

Designing IP Subsystems Using IP Integrator (UG994) [Ref 35].

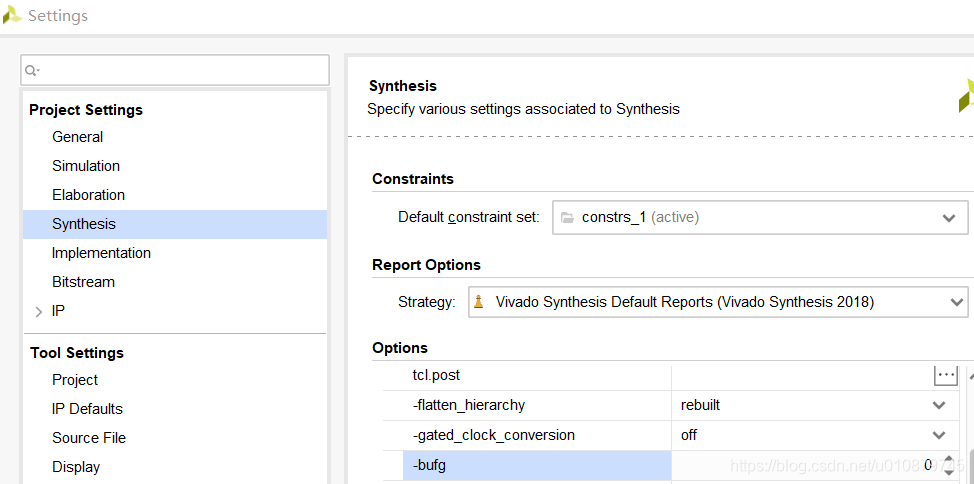

赛灵思的下面的文档已接近完善,但缺少最重要的一环,先必须清cache

AR# 57546: Vivado IP Flows - How to modify/edit IP core source files in Vivado? https://www.xilinx.com/support/answers/57546.html

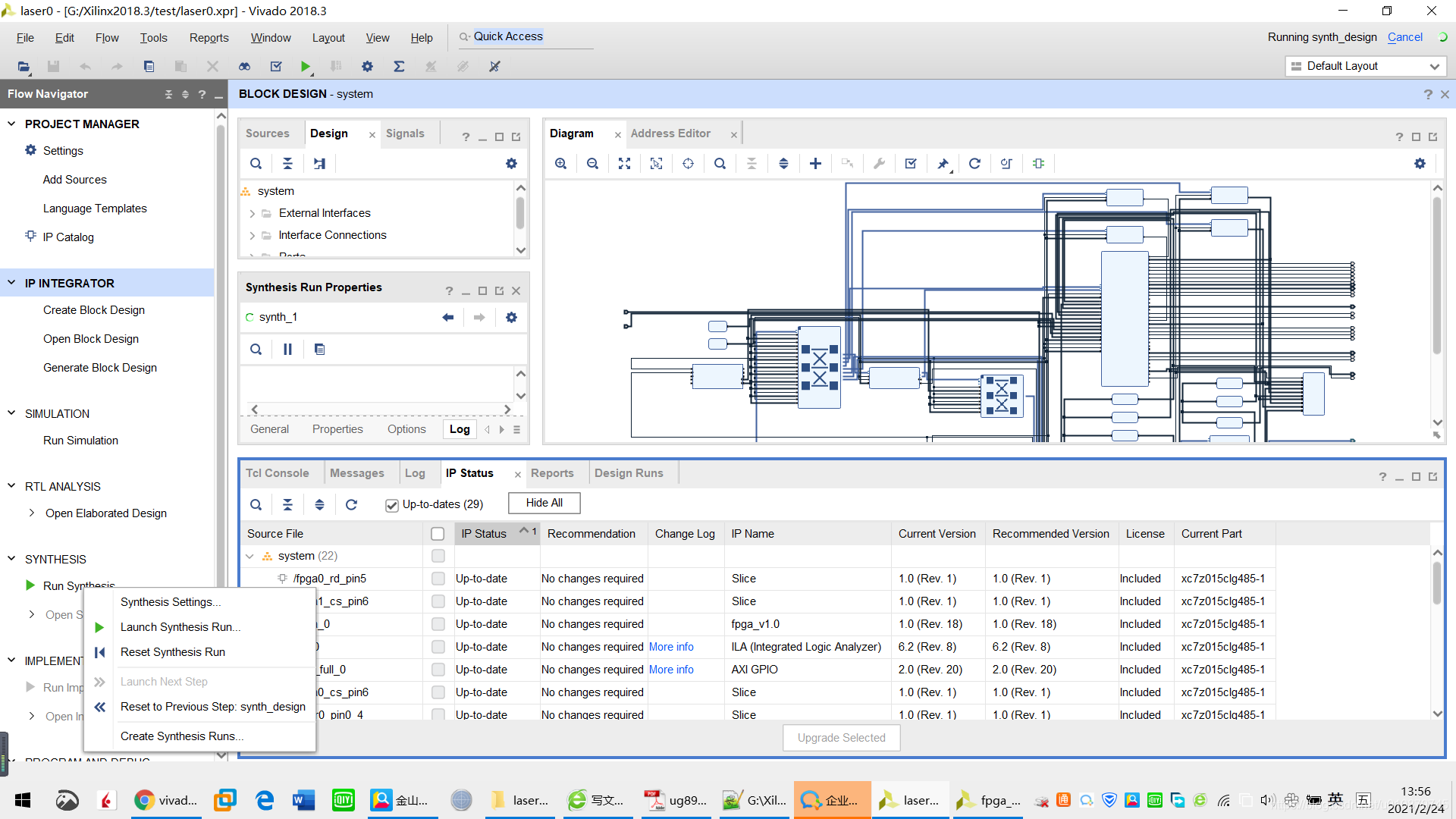

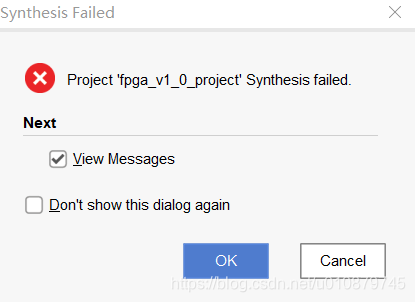

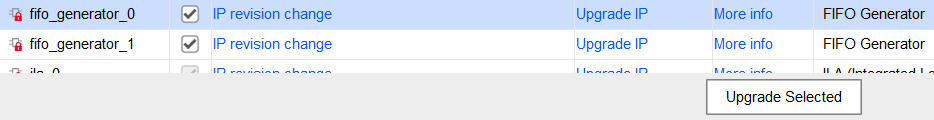

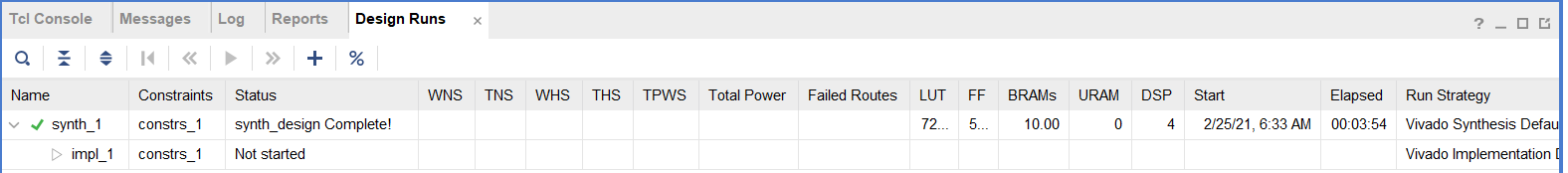

成功经验

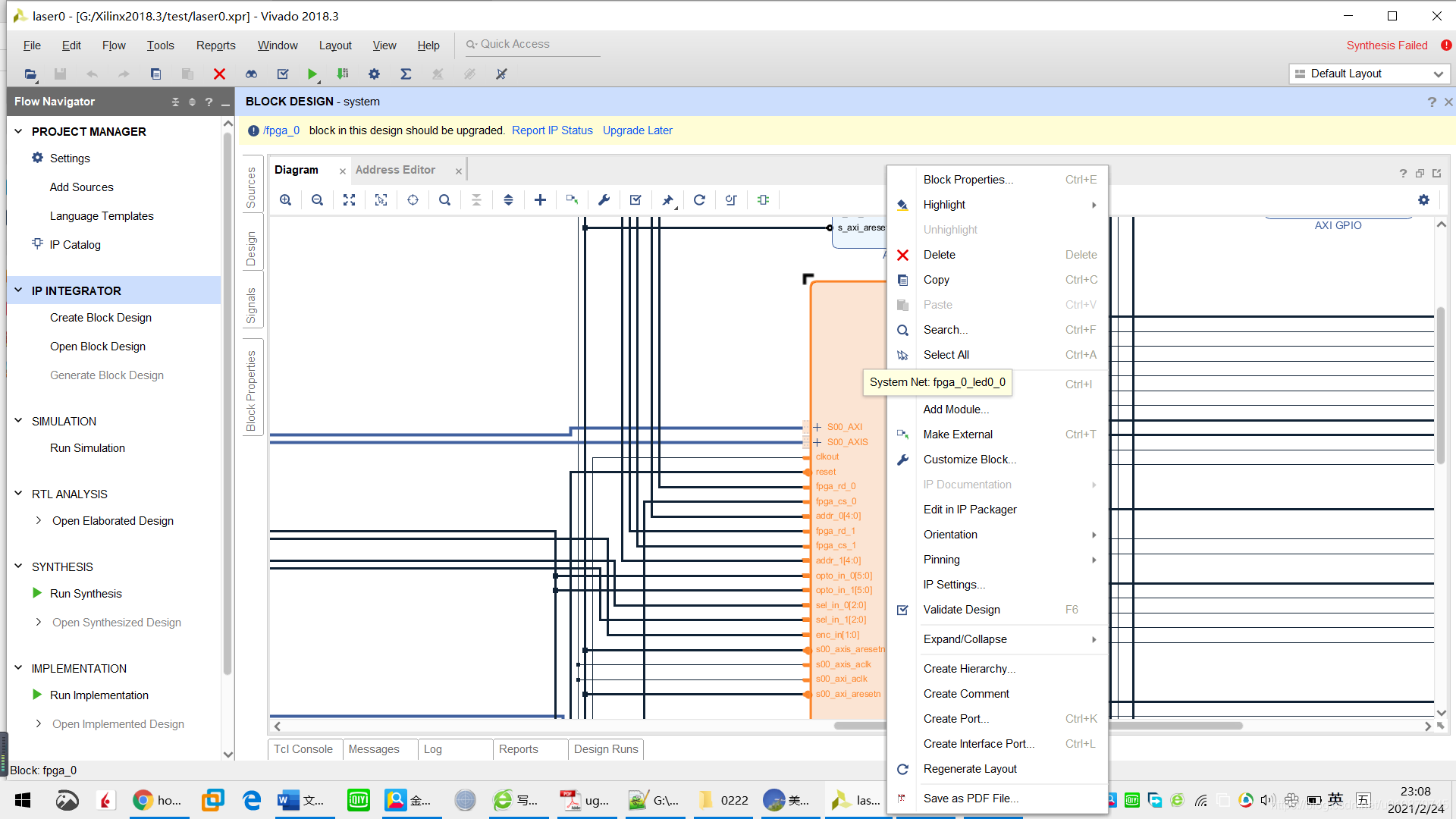

第一步,锁死要修改的文件,左上角的红锁。

set_property IS_LOCKED true [get_files system_fpga_0_0.xci]

get_property IS_LOCKED [get_files system_fpga_0_0.xci]

1

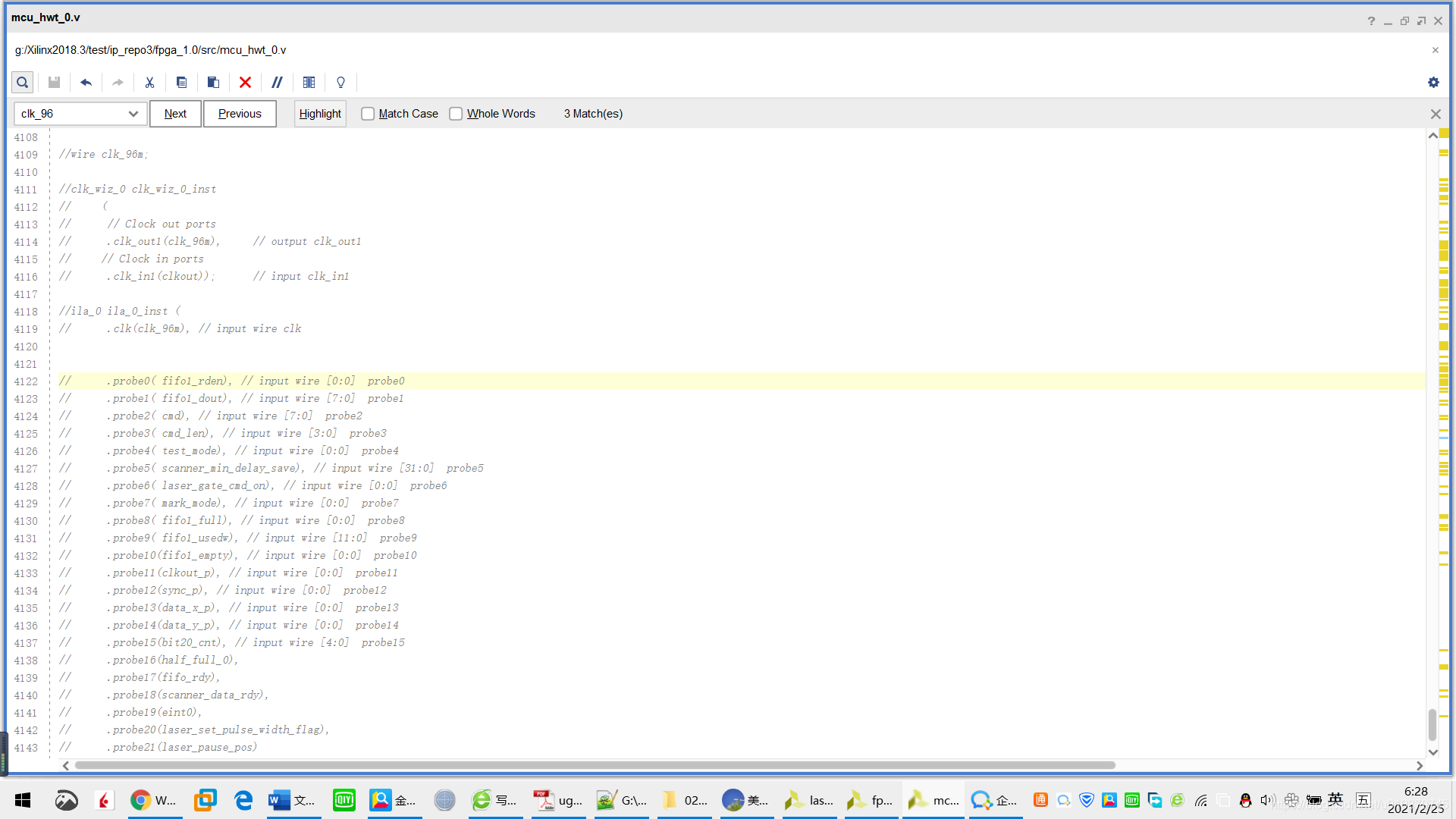

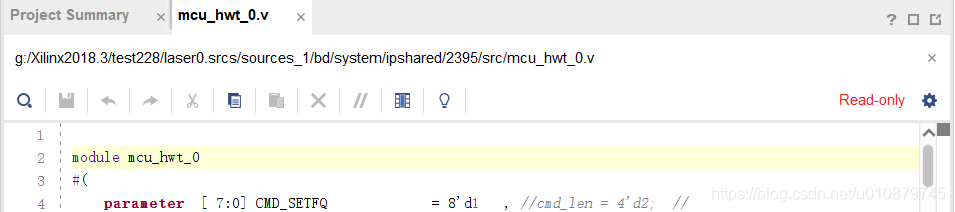

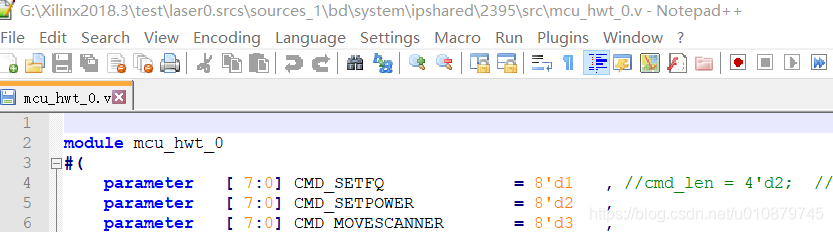

第二步,由于是只读文件,用第三方的编辑器, 编辑后保存。

用第三方编辑器,如Notepad++

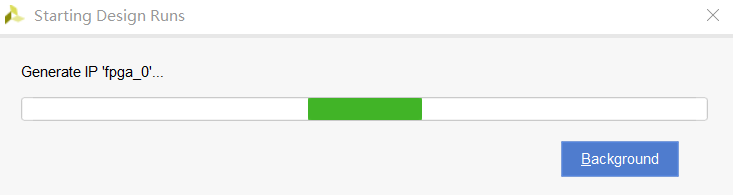

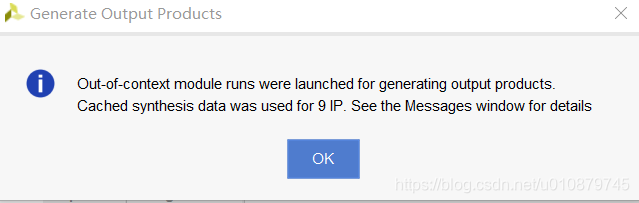

第三步,运行下面的Tcl例程, 否则改一个地方要进行无数神操作,累死…

重要核心代码

config_ip_cache -clear_output_repo

reset_run system_fpga_0_0_synth_1

launch_run system_fpga_0_0_synth_1

wait_on_run system_fpga_0_0_synth_1

reset_run synth_1

launch_runs synth_1 -jobs 4

wait_on_run synth_1

refresh_design

report_timing_summary -delay_type min_max -report_unconstrained -check_timing_verbose -max_paths 100 -input_pins -routable_nets -name timing_1

config_ip_cache -clear_output_repo

reset_run system_mcu_hwt_0_0_0_synth_1

launch_run system_mcu_hwt_0_0_0_synth_1

wait_on_run system_fpga_0_0_synth_1

reset_run synth_1

launch_runs synth_1 -jobs 4

wait_on_run synth_1

refresh_design

report_timing_summary -delay_type min_max -report_unconstrained -check_timing_verbose -max_paths 100 -input_pins -routable_nets -name timing_1

899

899

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?