7 Series ISERDESE2 and OSERDESE2

ISERDESE2:input serial-to-parallel converters;

OSERDESE2:output parallel-to-serial converters;

在xilinx 7系列FPGA中ISERDESE2和OSERDESE2支持非常高的I/O数据速率,对于ISERDESE2存在bitslip信号来重新对齐串行数据以获得正确的字节数据;

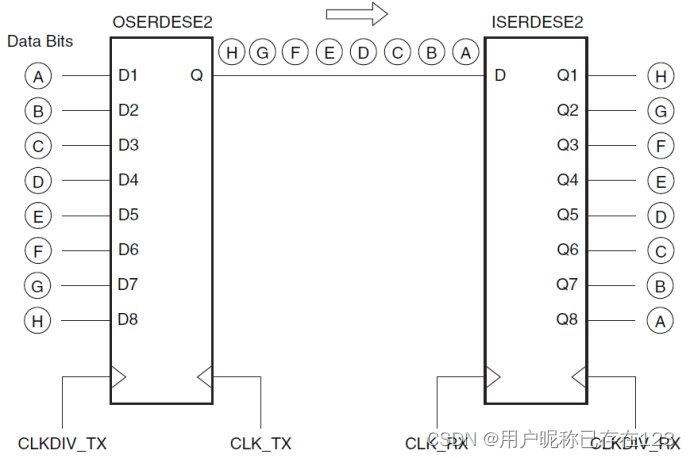

上图为OSERDESE2并转串输出到ISERDESE2串转并输入的字节序变化。

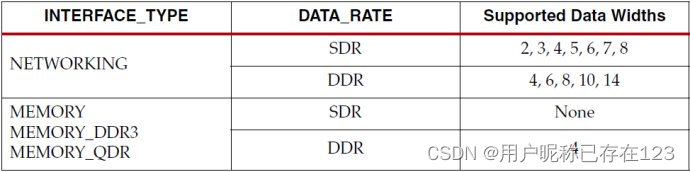

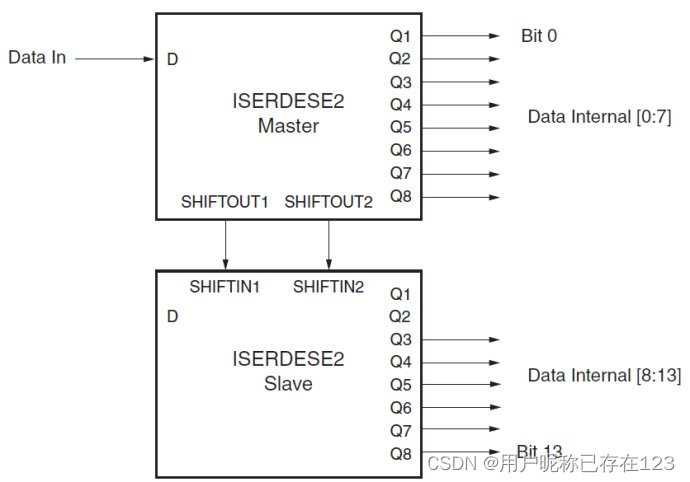

上表列出了ISERDESE2以及OSERDESE2可以实现的串并转换的并行数据的位宽,其中10与14位位宽需要两个ISERDESE2级联或两个OSERDESE2级联获得。

注意级联时,当需要获取10位位宽时,使用下面一个ISERDESE2的Q3与Q4来作为Data Internal[8:9];当需要获取14位位宽时,使用下面一个ISERDESE2的Q3~Q8来作为Data Internal[8:13]。

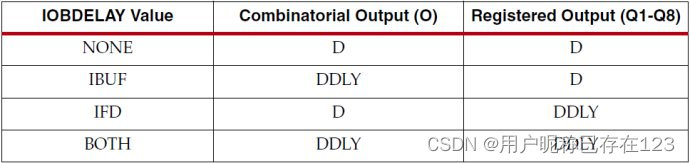

对于ISERDESE2而言,串行输入可以直接来自IOB也可以来自IDELAY2单元(串行信号经过IDELAY2后进行了延时),这就需要通过IOBDELAY Value来设置,具体参数设计以及ISERDESE2实际使用的输入如下表所示:

、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、、

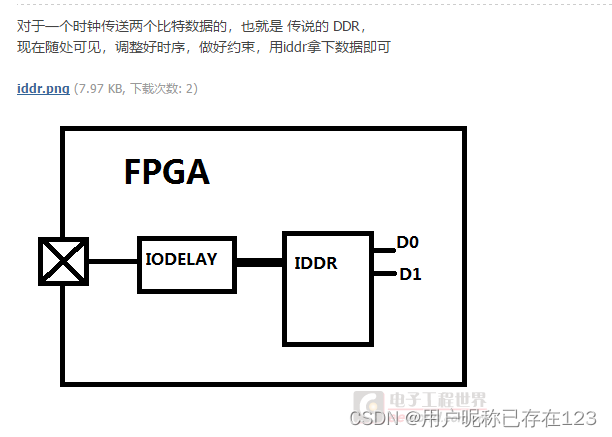

无论是HiSPi、LVDS还是MIPI,其核心思想就是要实现将高速串行信号恢复成并行数据。这将会用到XilinxFPGA IOB上的一个重要的资源——ISERDES。

实现串行信号的并行化,光有ISERDES还不行,还需要用到IOBANK上的延时模块IDELAYCTRL和IOB上的IODELAYE以及相关的相位训练算法。

在电压、温度等因素变化时,可能会影响到系统的时序,此时IDELAYCTRL模块就可以连续补偿时钟域内所有个体的delay taps (IDELAY/ODELAY)。如果使用了IOB上的IDELAY或ODELAY资源,那么就必须使用IDELAYCTRL资源。请注意,整个IO BANK里面只有一个IDELAYCTRL。

IDELAYCTRL很重要的一个输入项就是参考时钟REFCLK,补偿时钟域内所有模块的时序参考,这个时钟必须由BUFG或BUFH驱动。REFCLK必须保证在FIDELAYCTRL_REF+IDELAYCTRL_REF_PRECISION(MHz)ppm才能保证IDELAY/ODELAY的延时分辨率:

(TIDELAYRESOLUTION=1/(32x 2 x FREF))

(TIDELAYRESOLUTION=1/(32x 2 x FREF))

vivado,data_delay 可调tap范围0~31,clock_delay可调范围0~31;

即 data_delay 和clock_delay各占用ref_clock的半个周期。clock_delay即相当于data 前置,与data_delay是相反方向的相位设置。

ex,ref_clock = 200MHz, ref_clock_period = 1/ 200MHz = 0.5 ns = 5000ps

则data_delay 1个tap = 5000ps / 2 / 32 = 78ps

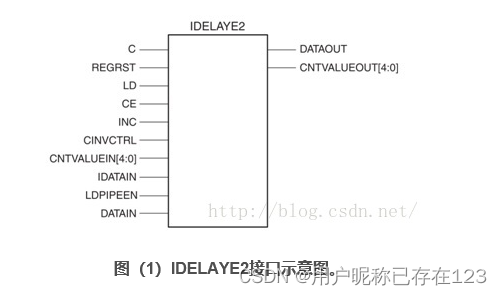

IDELAYE2逻辑是一个31抽头的循环延时补偿模块,对输入的信号进行指定分辨率的延时,FPGA可以直接访问。Tap延时分辨率由IDELAYCTRL的参考时钟提供持续补偿。图(1)是IDELAYE2接口示意图,表(1)是对这些接口的描述,表(2)是对逻辑参数的描述。

|

端口名 |

方向 |

位宽 |

描述 |

|

参数名 |

值域 |

默认值 |

描述 |

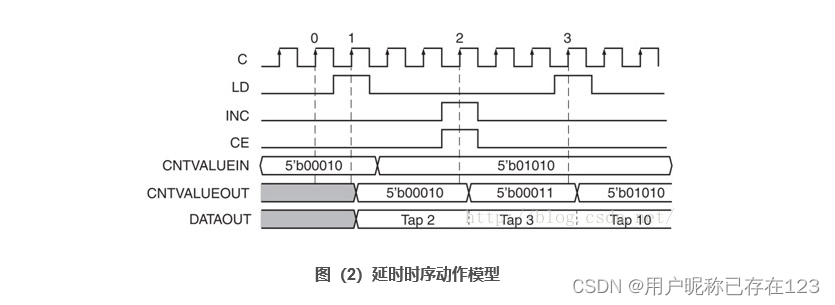

以下以VAR_LOAD模式为例说明延时的时序动作,如图(2)所示。

在C的上升沿采样到LD有效,此时DATAOUT延时CNTVALUEIN指定的延时Taps,改变tap Setting到Tap2,CNTVALUEOUT更新到新的Tap值;

INC和CE有效,此时指定了增量操作,Tap值加1,DATAOUT输出从Tap2更新到Tap3,CNTVALUEOUT更新到新的Tap值;

LD有效,DATAOUT输出延时更新到Tap10,CNTVALUEOUT更新到新的Tap值。

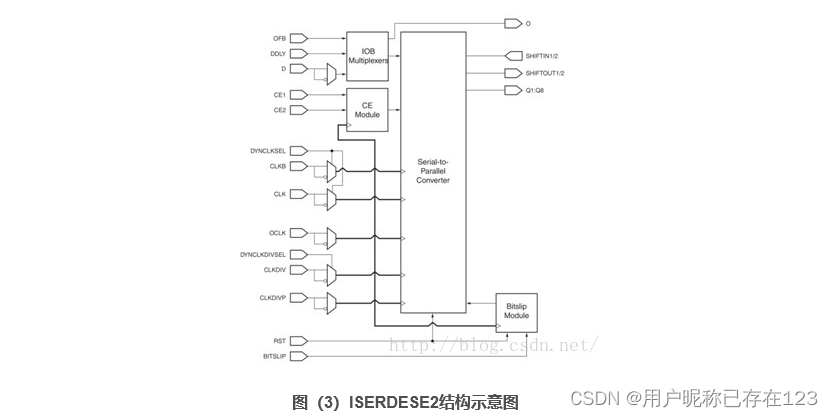

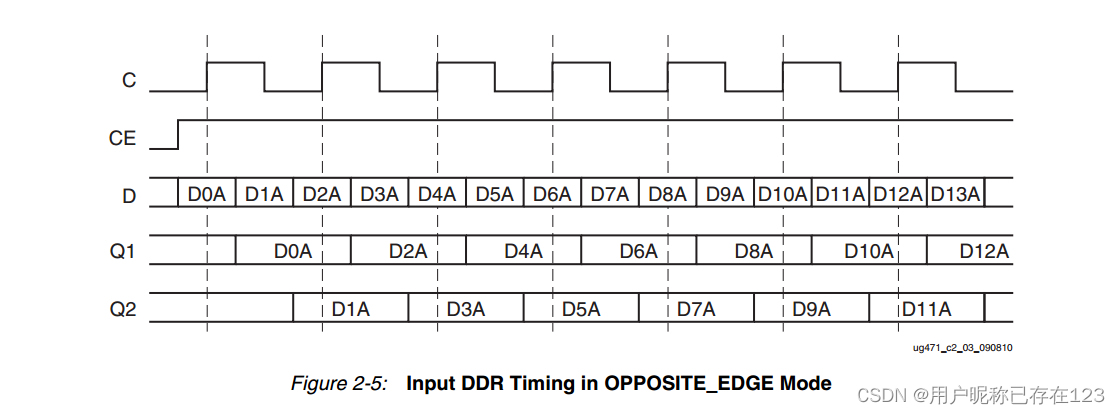

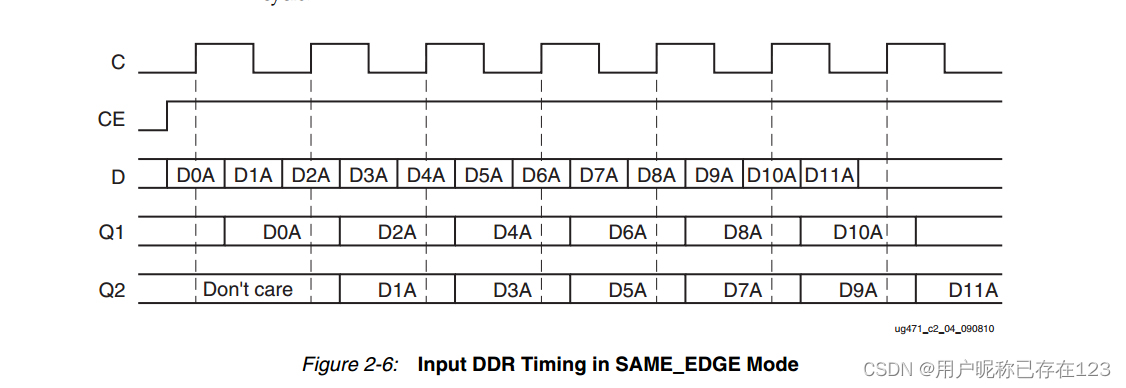

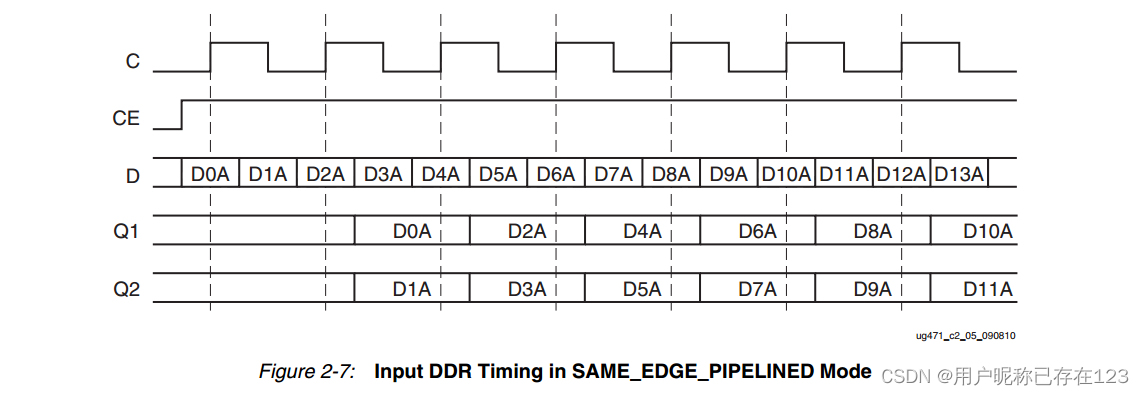

输入串转并逻辑可以看做是OSERDESE2的逆过程,在SDR模式下可支持2-、3-、4-、5-、6-和7-的串并转换,在DDR模式下可支持2-、4-、6-、8-的串并转换,级联DDR模式下还可扩展到10-和14-。每一个ISERDESE2包括:

图(3)是ISERDESE2的结构示意图。表(3)是ISERDESE2接口描述,表(4)示ISERDESE2的参数描述。

|

端口名 |

方向 |

位宽 |

描述 |

|

参数名 |

阈值 |

默认值 |

描述 |

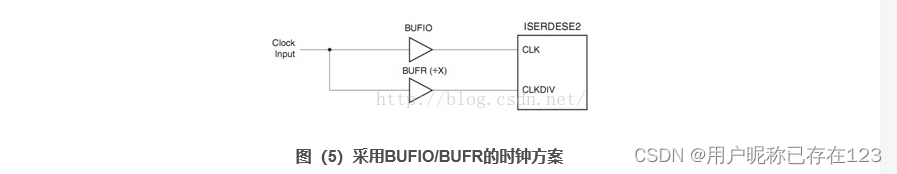

CLK和CLK_DIV必须是严格对齐的时钟,虽然允许使用BUFIO/BUFR,但任然有可能存在相位问题。图(5)时采用BUFIO/BUFR的方案。

n CLK→MMCM/PLL;CLKDIV→和CLK相同的MMCM/PLL的CLKOUT[0:6]的输出,使用MMCM时CLK和CLKDIV必须使用相同的驱动BUF;

n CLK→BUFIO, OCLK→BUFIO,或CLKDIV→BUFR;

n CLK→MMCM或PLL, OCLK→MMCM,或CLKDIV由同一个MMCM/PLL的CLKOUT[0:6]驱动;

OCLK和CLKDIV的输入相位必须是严格对齐的,CLK和OCLK之间不要求相位关系。From CLK to OCLK的时钟域必须进行补偿。

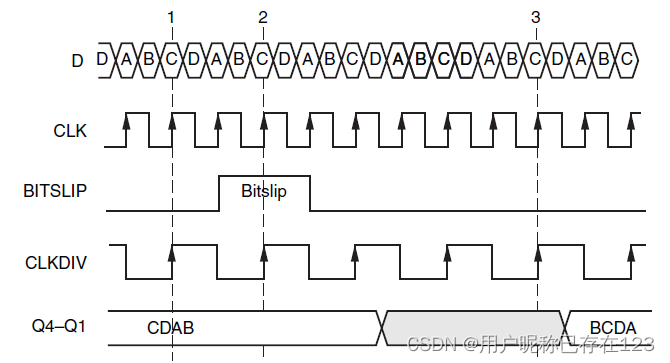

BitSlip用于调整并行寄存器输出串行数据的位置。在SDR模式下,每一个BitSlip脉冲让输出pattern的数据左移1bit;在DDR模式下,第一个BitSlip右移1bit,第二个BitSlip左移3bit,依次进行,移动规律如图(6)所示。BitSlip一定是和CLKDIV同步的一个脉冲

使用bitslip信号可以修改串转并的起始位置,如下图所示,为DDR模式下使用bitslip的时序图,开始时最先采集到的串行数据转换出来的并行数据为0xCDAB,插入一个bitslip信号后采集数据变为0xBCDA,你可以通过多次插入bitslip的方法来获取正确的并行数据序。

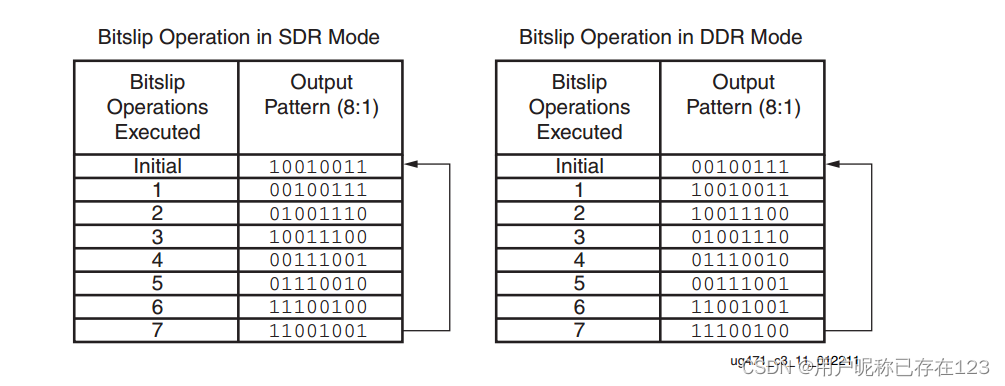

SDR以及DDR模式下bitslip插入次数对并行数据字节序的影响如下图所示,插入8次bitslip就可以将整个转换循序循环一遍。

不管是哪种方式,我们都是一次一次的拉高bitsilp,直到有正确的字节顺序。

在上面所介绍的资源中,IDELAYE2是动态相位对其训练的神器,ISERDESE2实现串并转换,其Bitslip功能是实现并行化数据对齐的关键。

Although the repeating pattern seems to show that bitslip is a barrel shifting operation, this is not the case. A bitslip operation adds one bit to the input data stream and loses the nth bit in the input data stream. This causes the operation on repetitive patterns to appear like a barrel shifter operation.

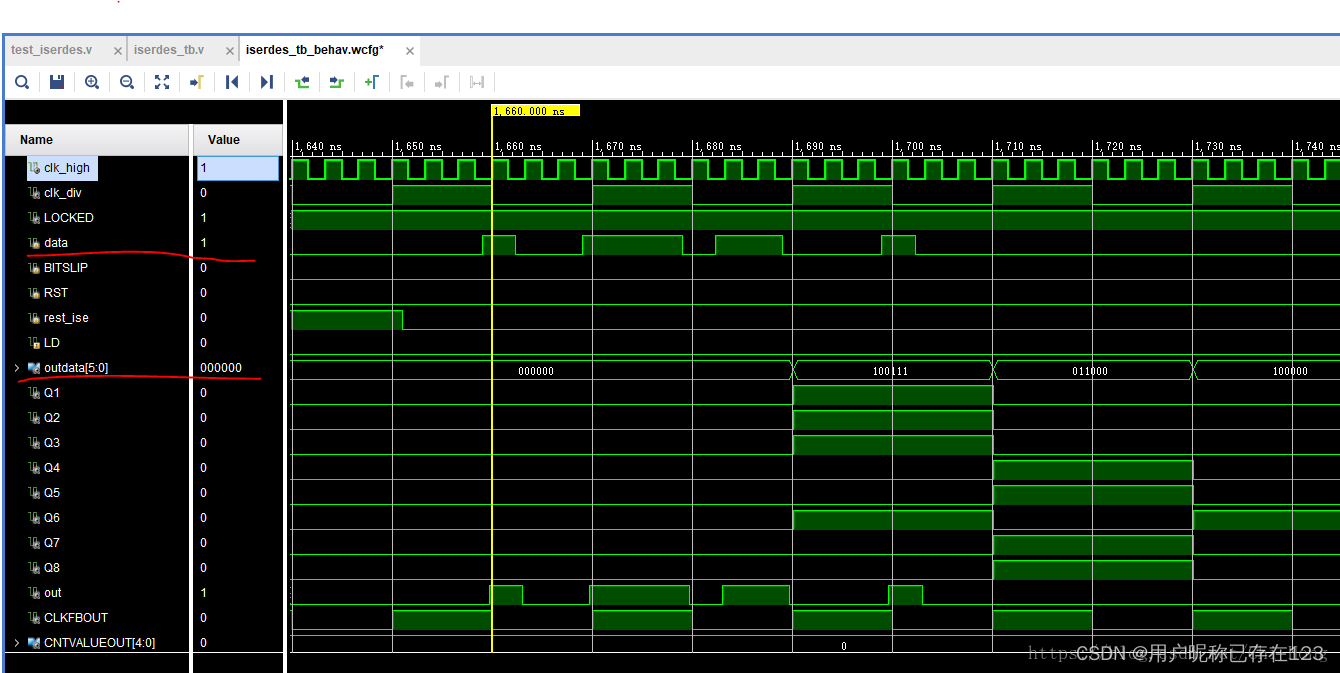

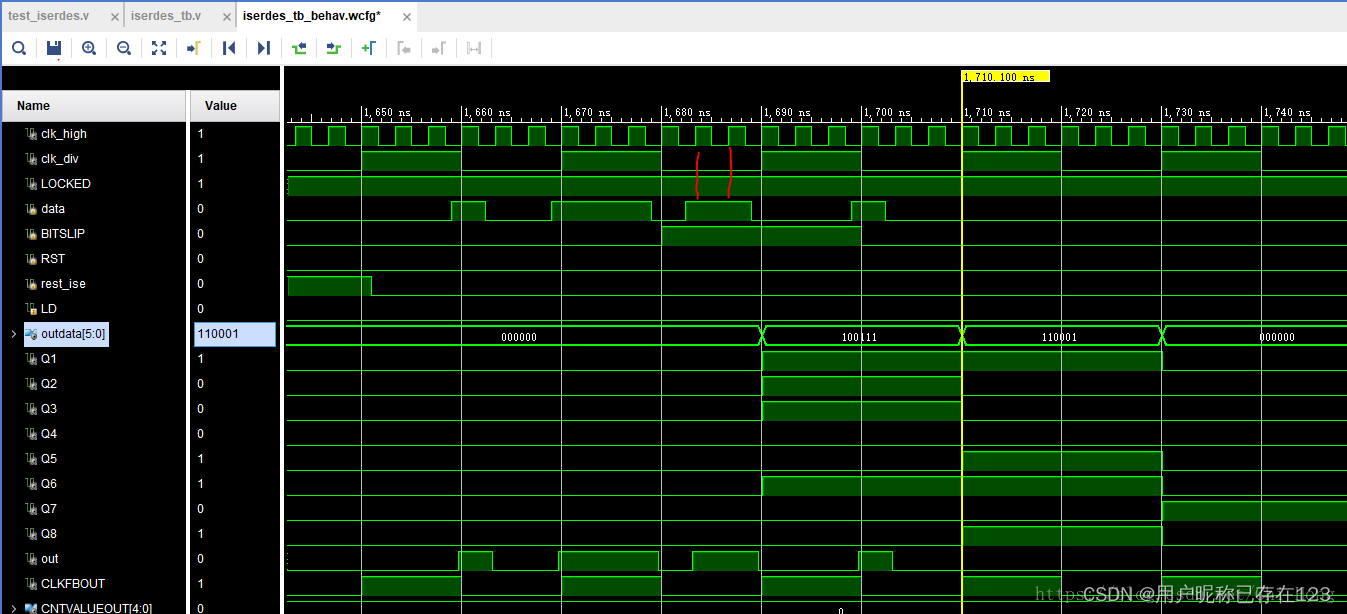

图1是没有使用bitsilp的情况,可以看到接受到的数据为:100111 011000 100000

再第二个时钟 使用bitsilp之后,数据变成: 100111 110001 000000

可以看到第二拍的数据 从原来的011000 变成110001 ,而末尾的1是下一个数据的1,开始的0被丢弃

文章详细介绍了Xilinx7系列FPGA中的ISERDESE2输入串行到并行转换器和OSERDESE2输出并行到串行转换器的使用,包括它们在高速I/O数据速率下的应用,以及如何通过bitslip进行数据对齐。此外,还讨论了IDELAYE2延迟模块在时序补偿中的作用和工作原理。

文章详细介绍了Xilinx7系列FPGA中的ISERDESE2输入串行到并行转换器和OSERDESE2输出并行到串行转换器的使用,包括它们在高速I/O数据速率下的应用,以及如何通过bitslip进行数据对齐。此外,还讨论了IDELAYE2延迟模块在时序补偿中的作用和工作原理。

1566

1566

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?