目录

1、二选一MUX的真值表

输入为din0、din1,控制为sel,输出为dout

| sel | dout |

| 0 | din0 |

| 1 | din1 |

2、逻辑框图与逻辑表达式

逻辑表达式:

3、组成结构

使用与门、或门、反相器来构造二选一MUX:

二、Glitch free 无毛刺的MUX

1、利用MUX实现时钟切换

将上图的din0、din1替换成两个不同频率的时钟CLK0、CLK1,这个时钟切换复用器有1个控制信号SELECT,当 SELECT = 0 时输出 CLK0,当 SELECT = 1 时输出 CLK1。

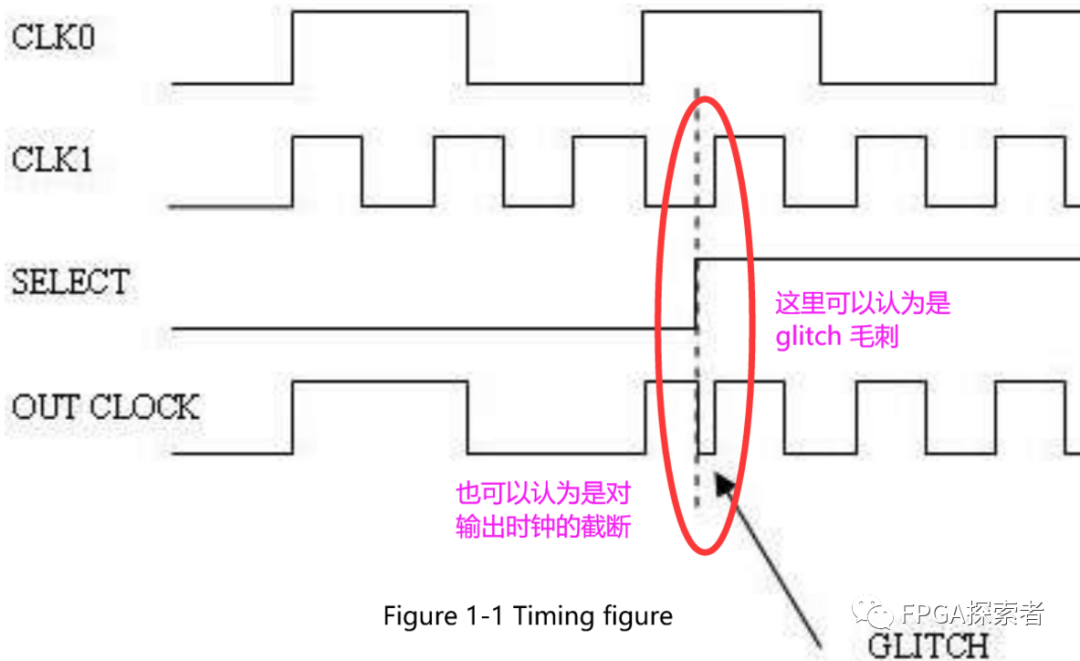

当 SELECT 的值发生变化,输出时钟从当前的时钟源切换到下一个时钟源,此时可能会产生毛刺。

如下图中的时序图所示,当 SELECT 控制信号变化时,在输出OUT CLOCK 上产生了毛刺。这类门控开关的问题在于,SELECT 开关控制信号会在时钟源的任意电平位置发生变化,从而导致输出时钟截断或者产生毛刺。

毛刺出现原因:

SELECT在CLK0的高电平期间进行了切换,这样CLK0的输出就被截断了,导致输出出现了毛刺。因此SELECT控制信号不能在当前时钟为高电平时切换时钟源。

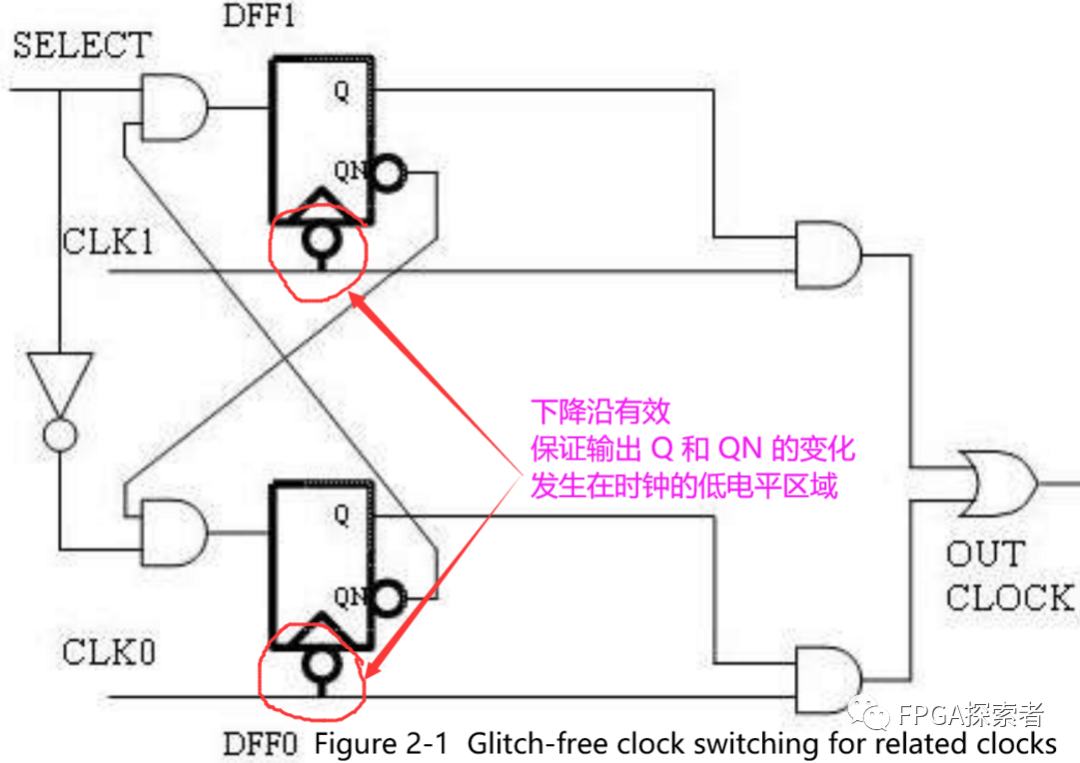

2、时钟无缝切换方法

原时钟切换电路如上所示,其缺陷为不能保证SELECT信号不在高电平时切换。为了让SELECT控制信号只在时钟低电平时切换时钟,引入下降沿触发的D触发器,即只在CLK由1变0时才能切换时钟,或者这样理解,得让当前时钟源有效电平结束了,才能切换时钟源

如上图所示,在每个时钟源的选择路径上,都插入一个下降沿有效的D触发器。

对某一个时钟的选择会通过QN端反馈到另一个时钟上,这种反馈机制使得门控开关在选择输出下一个时钟之前,必须先取消当前时钟的输出选择,避免了任何可能出现的毛刺Glitch。

比如,当前SELECT为0,CLK0被输出,设在CLK0为高电平时刻将SELECT置为1,此时DFF1的输出不会马上变为1,CLK1也就不能输出,而是在CLK1降为0时,才输出CLK1,而它此时是低电平,故不会出现毛刺

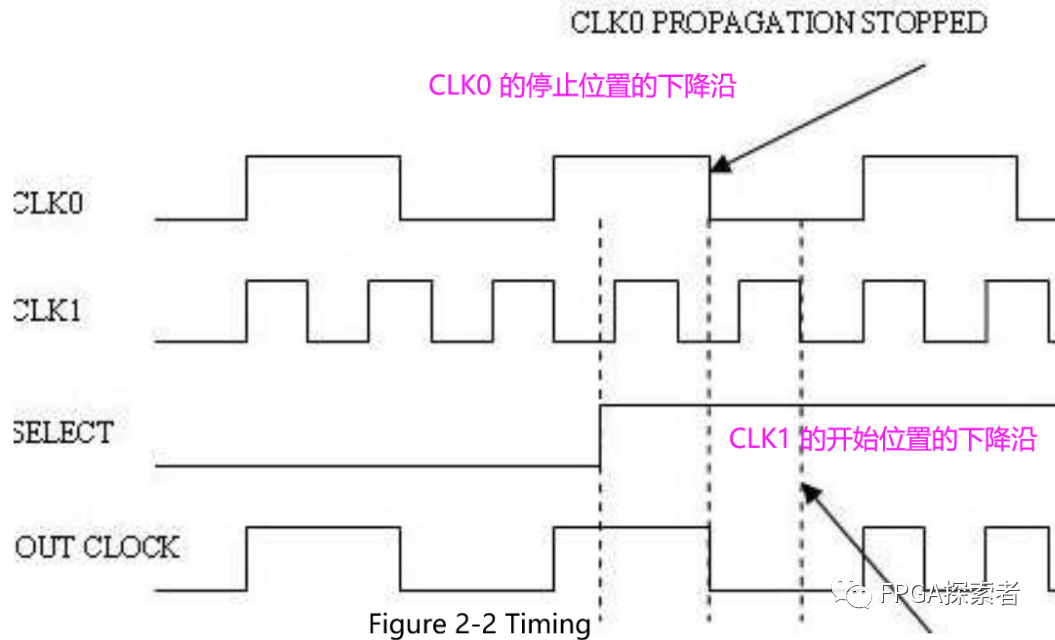

结合上面的时序图,对输入与输出的关系会更加清晰:

当输出时钟为CLK0时,在CLK0高电平时切换时钟源,即将SELECT置1,因为CLK0的下降沿还未出现,此时DFF0仍然保持SELECT为0的状态,因此反馈也没有更新,DFF1不变,继续输出CLK0;

直到CLK0的下降沿来临,DFF0收到SELECT置1的状态,将其传递到后面的与门,并反馈给DFF1的输入端与门上,此时下面的与门无效了,只用看电路的上半部分就行了;

不过DFF1的输入端刚刚才为1,要等到CLK1的下降沿来临,才能将SELECT为1的状态送入DFF1并向后传递。

也正如上图红字表示的一样:

- SELECT变化后,先保持CLK0继续输出;

- 在原时钟源CLK0的下降沿到来时,输出被停止,且一直为0(此时用下半部电路表示输出,因为SELECT为0了,导致输出的或门两个输入都是0,所以输出即不为CLK0,也不是CLK1,而是0);

- 在原时钟源CLK0变0后,开始找CLK1的下降沿,其出现后,输出用上半部分电路表示了,即输出为CLK1

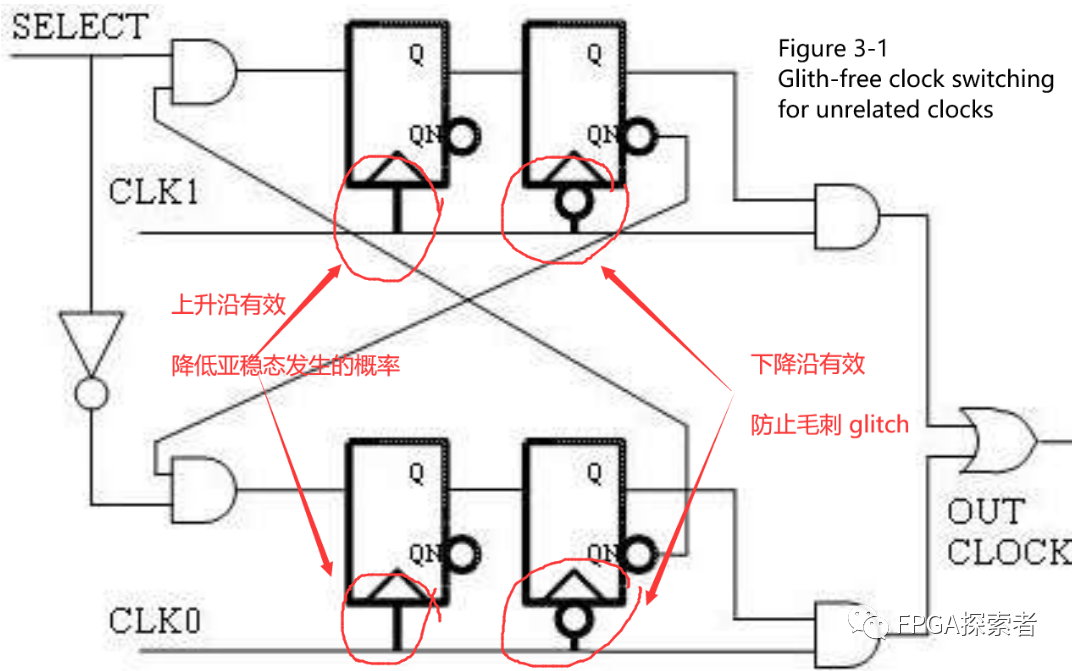

3、不相关时钟的无缝切换

在前一种避免输出毛刺的门控选择方式中,要求两个输入时钟源的频率有倍数关系,这样使用者可以(通过使用恰当的时序约束)避免信号与任何一个时钟域异步。这种实现方式没有处理异步信号的机制。

这样,提出第二种实现方式,使用同步电路来避免异步信号带来的潜在的亚稳态风险。当两个时钟源完全不相关时,异步行为可能来自 SELECT,也可能来自另一个时钟域的异步的反馈信号。

详细请前往:

163

163

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?