*以下是个人对相关基础知识的梳理和总结,对于高度专业性的知识个人理解可能会有出入,如果有误,希望各位大佬不吝指教;

1.硅晶体

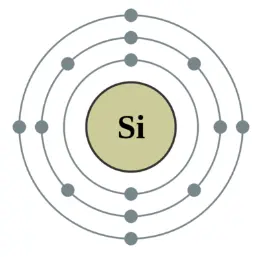

硅(Silicon),是一种化学元素,化学符号是Si。原子序数14,相对原子质量28.0855,有无定形硅和晶体硅两种同素异形体。硅也是极为常见的一种元素,然而它极少以单质的形式在自然界出现,而是以复杂的硅酸盐或二氧化硅的形式,广泛存在于岩石、砂砾、尘土之中。

单纯的硅晶体是不导电的,因为硅最外电子层有4个电子,可以与周围四个硅元素的电子层,两两结合组成共价键。共价键对电子的束缚很强,但一旦晶体内出现其他的杂质元素,很有可能引入额外的电子和空穴(统称为载流子),导致其导电性能得到提升。

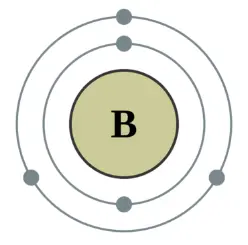

2.P型半导体

P型半导体,也称为空穴型半导体,其特点是在半导体材料中把硼(B)、镓(Ga)或铟(In)作为杂质(最外层具有3个电子的第三主族元素)掺杂到硅中,即可制成p型半导体。在适当掺杂后,硅单晶的电阻率将得到显著下降。元素的3个电子和硅的3个电子结合,其中一个电子将不足以使硅和硼键合,从而产生了缺少电子的空穴,这个空穴就是p型半导体的载流子,下面以硼(B)来举例:

在外加电压的作用下,正电荷(空穴)在P型半导体中移动,产生电流。

实际上,P型半导体的空穴本身不能移动,前面所说的“移动”实际上是通过电子的移动来间接实现的。当外加电场作用时,附近的电子会被空穴捕获,这样空穴就消失了。然而,在电子被捕获的同时,失去电子的位置又会形成一个新的空穴。这个过程就像空穴在移动一样,尽管实际上是电子在移动填补空穴。

“p” 表示正电的意思,取自英文positive的首字母。

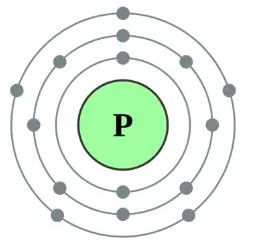

3.N型半导体

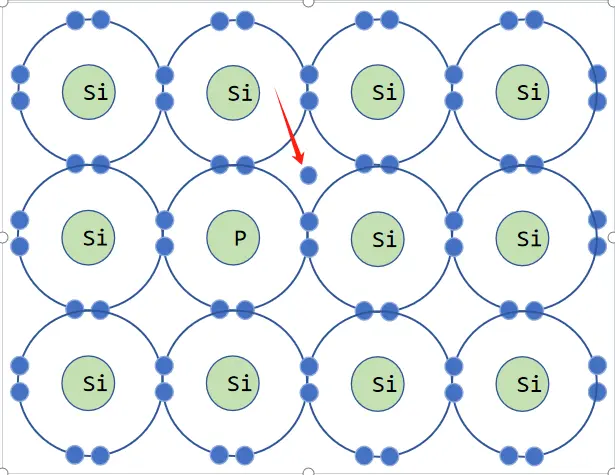

N型半导体,又称为电子型半导体,其制备过程是在半导体材料中把如磷(P)、砷(As)或锑(Sb)作为杂质(最外层具有5个电子的第五主族元素)掺杂到硅中,导致自由电子浓度远大于空穴浓度,即可制成N型半导体。在适当掺杂后,硅单晶的电阻率将得到显著下降。在N型半导体中,第五主族元素中的5个电子的其中4个和硅结合,剩余的一个即可自由移动成为自由电子,这个电子就是N型半导体的载流子。这些额外的自由电子是由杂质原子提供的,它们能够更容易地参与导电过程。下面以磷(P)来举例:

n” 代表负电,取自英文negative的首字母。

4.PN结

a.原理

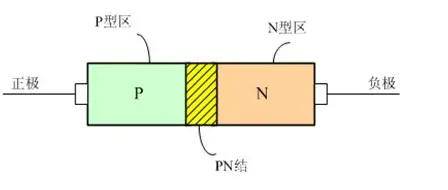

PN结是由一个N型掺杂区和一个P型掺杂区紧密接触所构成的。 在一块完整的硅片上,用不同的掺杂工艺使其一边形成N型半导体,另一边形成P型半导体,我们称两种半导体的交界面附近的区域为PN结。

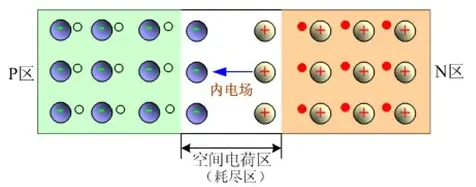

在P型半导体和N型半导体结合后,N型区内电子为多子,空穴为为少子,P型区内空穴为多子,电子为少子,在交界处就出现了电子和空穴的浓度差。然后一些电子从N型区向P型区扩散,一些空穴要从P型区向N型区扩散。结果就使P区失去空穴,留下了带负电的杂质离子,N区失去电子,留下了带正电的杂质离子。这些离子是不能移动的,称为空间电荷区,从而形成内电场,掺杂浓度越高,PN结越窄。

在空间电荷区形成后,由于电荷之间的相互作用,区域内形成了内电场,其方向是N区 ——> P区。同时,电场的方向与载流子扩散运动的方向相反,阻止扩散。这个电场将使N区的少数载流子空穴向P区漂移,使P区的少数载流子电子向N区漂移,漂移运动的方向正好与扩散运动的方向相反。最后,多子的扩散和少子的漂移达到动态平衡。

b.特性

想让PN结导通形成电流,必须消除其空间电荷区的内部电场的阻力。显然,给它加一个反方向的更大的电场,即P区接外加电源的正极,N区接负极,就可以抵消其内部自建电场,使载流子可以继续运动,从而形成线性的正向电流。而外加反向电压则相当于内建电场的阻力更大,PN结不能导通。

c.二极管&三极管

二极管就是基于PN结的单向导通原理工作的;而一个PNP结构则可以形成一个三极管,里面包含了两个PN结。二极管和三极管都是电子电路里面最基本的元件。

d.击穿性

雪崩击穿:阻挡层中的载流子漂移速度随内部电场的增强而相应加快到一定程度时,其动能足以把束缚在共价键中的价电子碰撞出来,产生自由电子—空穴对,新产生的载流子在强电场作用下,再去碰撞其它中性原子,又产生新的自由电子—空穴对,如此连锁反应,使阻挡层中的载流子数量急剧增加,像雪崩一样。雪崩击穿发生在掺杂浓度较低的PN结中,阻挡层宽,碰撞电离的机会较多,雪崩击穿的击穿电压高。

齐纳击穿:齐纳击穿通常发生在掺杂浓度很高的PN结内。PN结很窄,这样即使施加较小的反向电压(5V以下),结层中的电场却很强(可达2.5×105V/m左右)。在强电场作用下,会强行促使PN结内原子的价电子从共价键中拉出来,形成"电子一空穴对",从而产生大量的载流子。它们在反向电压的作用下,形成很大的反向电流,出现了击穿。

5.MOS(Metal Oxide Semiconductor金属氧化物半导体)

G:栅极

N Source:源极

N Drain:漏极

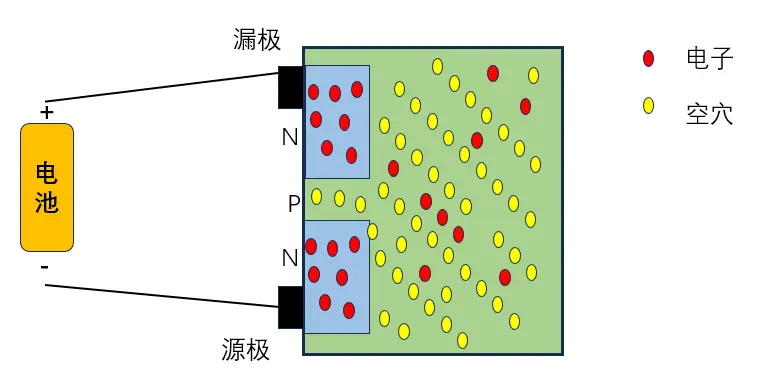

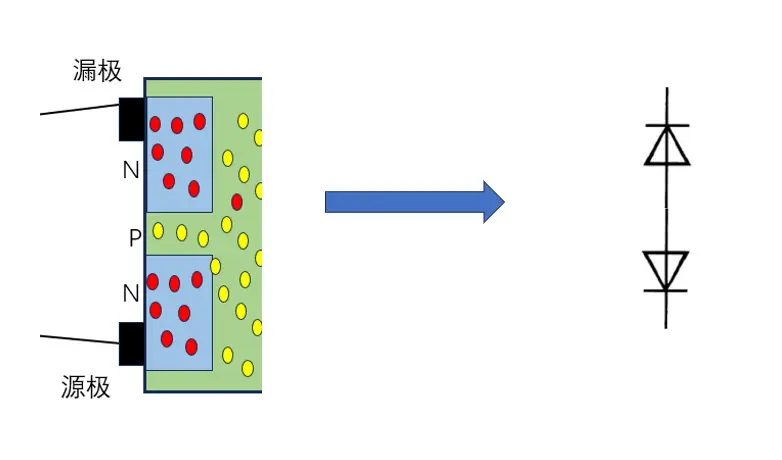

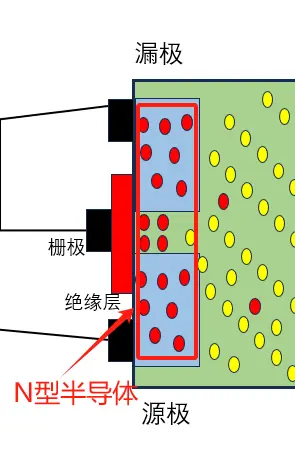

a.NMOS

先看没有栅极时的示意图,此时给源极和漏极通电,是不会导通的,中间的NPN结构可以想象成两个二极管相接,是截止的;

此时mos管截止

然后增加栅极,并给栅极也通电,此时栅极金属板上就有了电场,就会把P区中的电子吸引到绝缘层附近,同时把空穴赶走,电压越大,被吸引过来的电子越多,当电子足够多时,就形成了N沟道,就是N型半导体之间的沟道,此时N沟道取代了原来P型半导体中的空穴,导致之前的PN结消失

就可以把两块N型半导体+N沟道整个区域看作一整块N型半导体

最后看NMOS的电路符号,此时可能会有更透彻的理解;

中间的箭头符号就表示了电子的方向

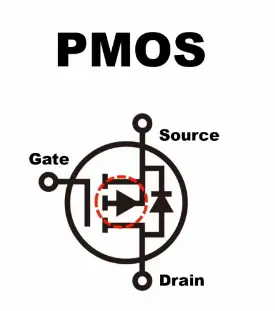

b.PMOS

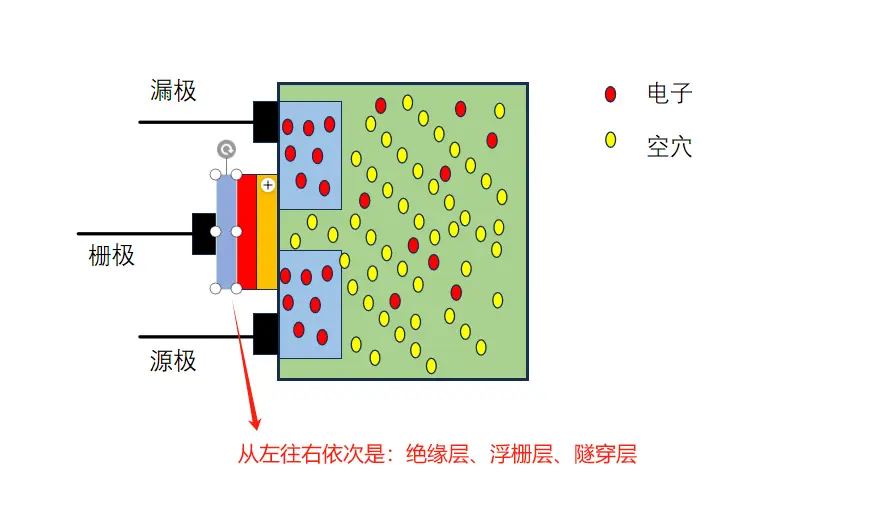

6.浮栅MOS

前面了解了常规MOS管的原理,常规晶体管只能控制截止和导通,下面来看浮栅MOS管有什么特别之处。

在之前的基础上增加了浮栅层和隧穿层,然后就可以存储信息了。那么是怎么存储信息的呢?

给栅极一个高压,电子就可以穿过隧穿层进入浮栅层,然后因为有绝缘层的存在,电子就在浮栅层止步了。如果在把电压撤走,此时这些电子依然会被锁在浮栅层,因为隧穿层本质上也是一种绝缘体【有兴趣可以去了解一下隧穿效应,这里就不做更深入的分析了】;

这样1bit数据就被存进去了;

好了,现在知道浮栅MOS怎么存储信息了,那它和目前SSD上大量使用的NAND Flash又是怎么联系在一起的呢?下篇会继续拓展【尽快更新ヾ(◍°∇°◍)ノ゙】

543

543

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?