2021.12.15

1、verilog里如果有符号数和无符号数做运算,会强制当作无符号运算

这就涉及verilog处理运算时的法则:

例如 c = a + b; 其中a和b都是四位数,c是五位。在计算时,verilog会将a和b都扩展到5位,然后再做加法,而如果a和b中有无符号数,则位宽扩展就按照无符号数来,也就是高位补0。所以如果a和b中既有无符号又有有符号,结果就不正确了。

解决方法是用 $signed()来修饰:c = a + $signed(b)这样在c = a + b,这个运算开始的扩位就会按照有符号数的方式进行扩位,在高位补符号位,加法得出的结果就是a、b视为有符号数的结果。

2、在Verilog语言中,有符号数signed以2进制补码形式表示。

2022.03.23

2、在Verilog语言中,有符号数signed以2进制补码形式表示。(但signed()括号里需要已经是补码,signed只起到扩充符号位的作用,不实现原码转补码)

4、"-"使用:

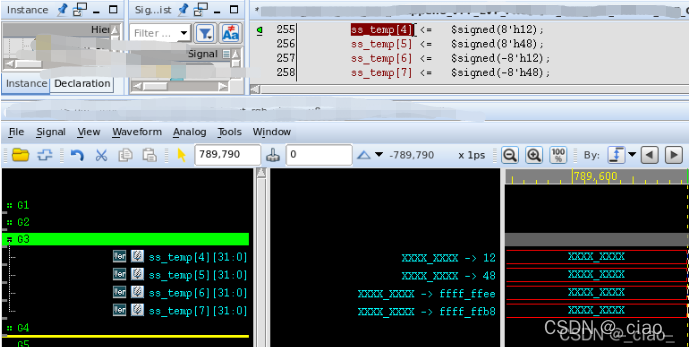

①使用负号似乎可以使得在位宽范围内正数的原码换算成补码:如下图8'h12和8'h48都能计算正确。

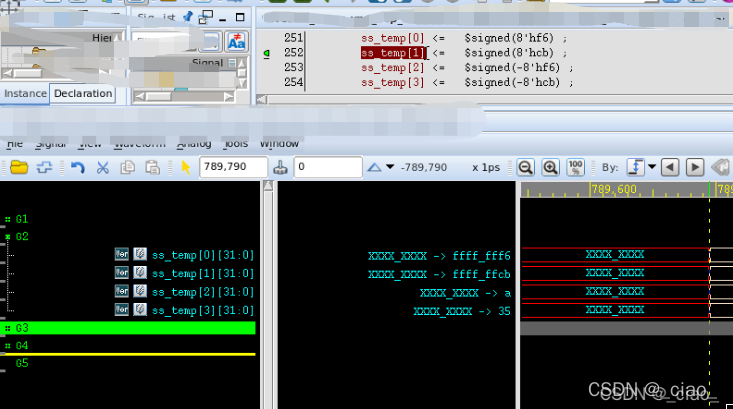

②使用负号似乎无法让负数的原码求得补码:如下图8'hf6和8'hcb全都计算错误

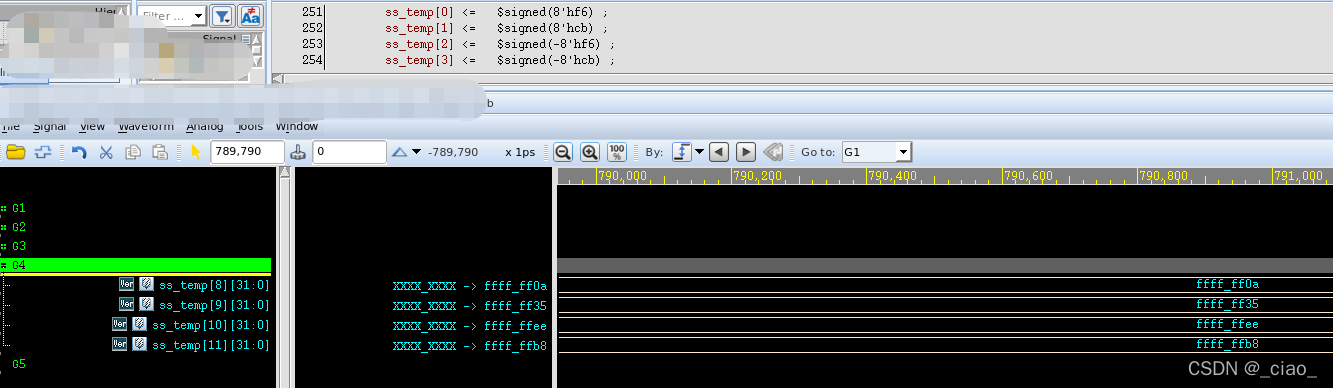

③使用负号视乎只是对无符号数所有位做了取反+1的操作:如下图仿真结果,对于8'hf6和8'hcb两个数在做了负号之后,在位宽不匹配的情况下,扩出来的位都被取反成1了。所以解释了signed(-8'hf6)和(-8'hf6)结果的不同,前者先按有符号数填充,最高位是1所以填充了一堆1,然后后取反➕1,结果为a,另一个先进行无符号数扩位,扩了一堆“0”,然后取反➕1,最后结果变为ffff_ff0a。

PS:以上是猜想,先暂记着,有空查手册手册手册!!!

本文探讨了Verilog中$signed和$unsigned在处理符号数和无符号数运算时的作用。当混合运算时,$signed确保运算按照有符号数规则进行,避免高位补0导致的错误。同时,文章指出$signed仅扩展符号位,不执行原码到补码的转换,并举例说明了负号在不同情况下的运算效果。

本文探讨了Verilog中$signed和$unsigned在处理符号数和无符号数运算时的作用。当混合运算时,$signed确保运算按照有符号数规则进行,避免高位补0导致的错误。同时,文章指出$signed仅扩展符号位,不执行原码到补码的转换,并举例说明了负号在不同情况下的运算效果。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?