Cadence是公司名,Allegro(俗称阿狸狗)是该公司旗下的EDA工具品牌,OrCAD是该公司收购公司的EDA工具品牌。

OrCAD这个产品线是Cadence收购来的,Allegro才是嫡系。

注意:dsn不能放在中文路径下。

-

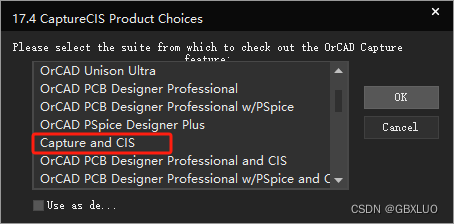

开机选capture and cis

CIS:Component Information System,元件信息系统,含有元件库管理之功能。

-

新建库:

选择菜单File—New—library,新建元件库

-

新建元件:

选中元件库文件(新建olb后缀文件),右键选择New Part新建元件。

-

查找相同的网络标号

选中网络所在的线段,然后鼠标右键,选中signals,左边会显示所有网络标号。

-

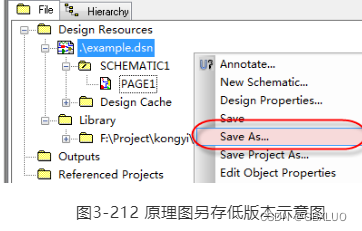

Orcad软件绘制的原理图存为低版本的方法

一种方法是:

第一步,需要选中降低原理图的根目录就是DSN文件,如图3-212所示,选中之后,点击鼠标右键,Save As,就可以存为低的版本:

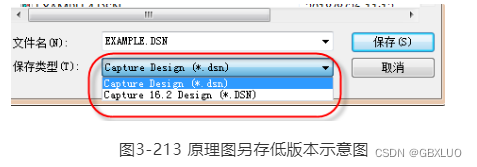

第二步,在弹出的界面中,如图3-213所示,在保存类型那一栏可以选择低的版本,一般是存为16.2的版本,这样就存为了低的版本了;

第三步,这里可以看到有这样的一个情况,就是Orcad存为低的版本的时候,只能存为一个版本,那就是16.2的版本。其实在Orcad设计的时候,16.2之前的版本,机制都是通用的,都可以打开,16.2以后版本的机制是一样的,所以存为低版本的时候,是以16.2为分界点来处理就可以了。

另一种方法是:

1.将高版本文件输出为EDIF文件,配置自己命名。

本文详细介绍了CadenceAllegroEDA工具的使用技巧,包括OrCAD的来源、CIS元件信息管理、原理图存为低版本方法、单位和格点设置、DRC检查规则及解决策略,以及PDF和FPGA约束脚本的生成。

本文详细介绍了CadenceAllegroEDA工具的使用技巧,包括OrCAD的来源、CIS元件信息管理、原理图存为低版本方法、单位和格点设置、DRC检查规则及解决策略,以及PDF和FPGA约束脚本的生成。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3704

3704

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?