一、波形文件与配置文件的说明

1、波形数据库文件(.WDB),其中包含所有的仿真数据。是vivado自动保存的文件;

因为.WDB文件自动保存的名称是一样的。如果想保存多次仿真的.WDB文件,在仿真完成后到xsim文件目录下将.WDB文件重命名,这样下一次仿真就不会覆盖这个.WDB文件。

2、波形配置文件(.WCFG),其中包含于波形配置文件中的对象相关联的顺序和设置,注意是配置文件,需要手动保存;

单个 .WDB可以对应多个 .WCFG文件, 可以通过打开 .WDB文件查看上一次保存下来的仿真波形(保存的波形文件需要在关闭工程后才能重新命令,不过可以复制粘贴后对粘贴的波形文件命名)。

注意:不能把这两个文件随便挪动到新的工程中打开,否则打开后的波形不对有异常。

二、波形文件与配置文件的保存:

波形数据库文件不需要手动保存,也没有可以手动保存的地方,是vivado自动保存在sim_1\behav\xsim文件夹下,文件名为:project_name.wdb

波形配置文件需要手动保存,在仿真波形窗口中选择保存按钮,或者file->Simulation Waveform->Save Configuration/Save Configuration As来保存;

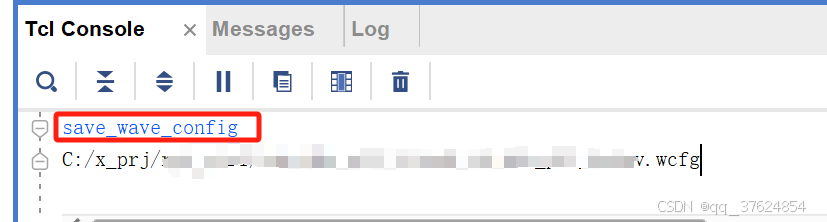

也可以在Tcl Console中输入:save_wave_config,如下图:

三、波形文件与配置文件的打开:

先打开波形文件:Flow->Open Static Simulation,选中保存的波形文件打开;

其次打开配置文件:File->Simulation Waveform->Open Configuration,打开你保存位置的配置文件即可重现你之前保存的仿真波形。

参考:

3320

3320

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?