三、同步开关噪声(SSN)

SSN是指器件在开关状态时产生的瞬间变化的电流(di/dt),在经过回流途径上存在的电感时,形成交流压降,从而引起噪声,也可称为△i噪声。

若是因为封装电感而引起的地平面波动,造成芯片地和系统地不一致,这种现象就是地弹。同理如果是因为封装电感引起的芯片和系统电源差异,就是电源反弹。

所以,综上所述:同步开关噪声并不完全是电源的问题,它对电源完整性产生的影响最主要的还是表现在地/电源反弹。

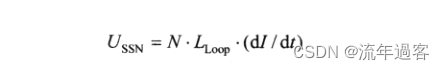

SSN主要是伴随着器件的同步开关输出(SSO)产生,开关速度越快,瞬间电流变化越显著,电流回路上电感越大,则SSN越严重:

其中,I:单个开关输出电流;N:同时开关的驱动数目;

Lloop:整个回流路径上的电感。

备注:

除了信号本身回流路径的电感外,相距较近的信号串扰也是导致同步开关噪声的因素。

分类:SSN可分为芯片内部开关噪声、芯片外部开关噪声

1、芯片内部开关噪声(on-chip)

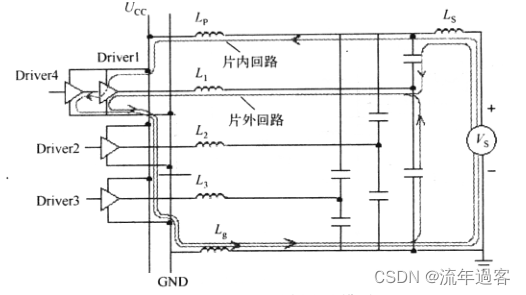

如下图所示,当Driver4开关时产生的噪声就是芯片内部开关噪声(此时Driver1为接收端),可以看到其回流路径只经过电源和地,与信号引脚的寄生电感无关;而当Driver1作为开关输出时,产生的就是芯片外部开关噪声,这时的电流经过信号线和地,但不经过芯片的电源引脚(信号跳变为1->0)

Lp和Lg为封装中电源和地的寄生电感;

Ls为系统电源的电感;

分析:

假设L为封装电源和地的总电感,而Lp和Lg上电流相反,所以:

L=Lp+Lg-2Mpg

Mpg:为Lp和Lg之间的耦合电感

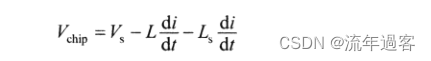

此时芯片实际电压为:

所以在瞬间开关时,加载在芯片的电源电压会下降。而这仅仅是假设只有一个内部驱动工作的情况,当有多个内部驱动工作的时候,造成的压降可想而知,从而导致器件的驱动能力降低。

所以为解决这种情况,通常采取以下措施:

(1)降低芯片内部驱动器开关速率以及同时开关的数目;

(2)降低系统供给电源的电感,高速电路设计中使用单独的电源层,并保持良好的电源、地耦合;

(3)降低芯片封装中的电源、地引脚的电感(可通过增加电源、地引脚数量;走线尽量短、通过铺铜等手段);

(4)增加电源、地的相互耦合电感也可减小总的回路电感,所以高速设计中电源和地的引脚要成对分布,且尽量靠近;

(5)在芯片封装内使用旁路电容,这样高频电流的回路电感会很小,从而减小SSN

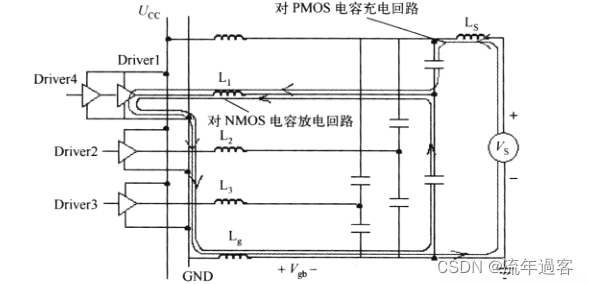

(6)给系统电源增加旁路电容(为高频的瞬变交流信号提供低电感的旁路,而低速信号仍然走系统电源回路),如下图所示:

2、芯片外部开关噪声(off-chip)

off-chip和on-chip最大的区别就是需要考虑信号线的电感。而这里又分为两种情况:

1->0跳变时,回流不经过封装的电源引脚;

0->1跳变时,回流不经过封装的地引脚。

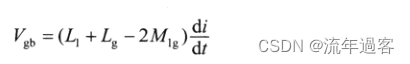

同理可计算封装电感造成的压降为:

此时芯片的地存在着Vgb的电压波动,这就是“地弹”;而同样0->1开关状态下,封装电感会给电源造成一定压降,就是所谓的“电源反弹”。

注意:

“地弹”是on-chip和off-chip同步输出综合的影响,且地弹噪声只来源于封装寄生电感,于系统的电源、地的电感无关(这也是SSN和地弹在概念上不同的根本所在)!

针对于off-chip噪声,可通过以下措施来解决:

(1)降低芯片内部驱动器开关速率及开关数目;

(2)降低封装回路电感,增加信号和电源、地的耦合电感;

(3)在封装内使用旁路电容,这样可让电源、地共同分担电流回路,可以减小等效电感。

3、等效电感衡量SSN

通过以上分析可知,实际中对于一个给定的电路(di/dt不变的情况),减小SSN就是减小信号回路的等效电感(Leff)。

Leff包括三部分:

on-chip开关输出的回路等效电感Leff.P

off-chip驱动从低到高开关输出的回路等效电感Leff.LH

off-chip驱动从高到低开关输出的回路等效电感Leff.HL

SSN的产生绝大部分都是源于芯片封装的问题,但是要判断高频封装的优劣最高的方法还是通过仿真来测试信号回路的等效电感来进行比较判断,Leff越大,那么SSN也就越大。

四、旁路电容

通过上述分析,无论是降低电源平面阻抗,还是减少SSN,旁路电容都扮演着举足轻重的地位,电源完整性设计的重点也在如何合理的选择和放置这些电容。

通过电容的等效阻抗公式会发现:工作频率越高,容值越大,则阻抗越小。

拓展:

电路中,可根据电容的作用不同分为以下几种:

(1)如果电容主要作用是给交流信号提供低阻抗通路,则称为旁路电容;

(2)如果电容主要是为了增加电源、地的交流耦合,减小交流信号对电源的影响,则称为去耦电容;

(3)如果用于滤波电路,则称为滤波电容。

想要理解电容在高速电路中扮演的重要角色的作用,就要先从电容的特性来了解一番电容的本质。

1、电容的频率特性:

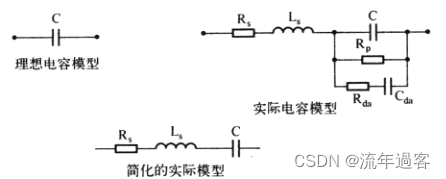

通过下图可知,实际的电容还包含着:

寄生串联电阻Rs(ESR),串联电感Ls(ESL),泄露电阻Rp,介质吸收电容Cda,介质吸收电阻Rda。

泄露电阻Rp也叫绝缘电阻,值越大,泄露的直流电流越小,性能越好,一般电容的Rp都很大,所以一般不需考虑;

介质吸收的等效RC电路反应了电容介质本身的特性,是一种有滞后性质的内部电荷分布,它使快速放电然后开路的电容器恢复一部分电荷,所以介质吸收太大的电容不能应用于采样保持电路;

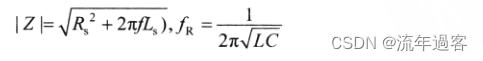

对电容的高频特性影响最大的是ESR、ESL,此时简化后的电容可看做一个串联谐振电路,其等效阻抗和串联谐振频率为:

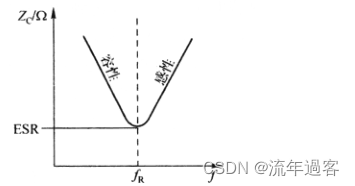

当电容在低频的时候(谐振频率以下),表现为电容性元件;

当频率增加(超过谐振频率)时,表现为电感性元件;

即:电容的阻抗随着频率的增加先增大、后减小;等效阻抗的最小值是在谐振频率时,其容抗、感抗正好抵消,此时阻抗恰好等于ESR。

2、电容封装及介质:

实际电容的特性主要受封装结构和介质材料的影响。

从封装来看主要就是直插式和表贴式(表贴式寄生电感要比直插式小很多,所以高频电路中都用表贴式);

从介质材料来看又分为陶瓷、云母、纸质、薄膜、电解等。

拓展:

(1)对于较大值得电容(大于10uF),一般封装较小的有更小的ESL、ESR!

(2)数字电路中使用最广泛的是陶瓷电容,具有介电系数高、绝缘度好,温度特性好等优点!

目前常用于陶瓷电容的介质有:Z5U(2E6)、X7R(2X1)、NPO(C0G)

Z5U:具有较高介电系数、成本低,常用于标称容量较高的大容量电容;但温度特性较差,常用于10-85℃;

X7R:介电系数较Z5U低,但电气性能稳定,适用于隔直、耦合、旁路、滤波电路及可靠性要求较高的场合;

NPO:电气特性最稳定,低损耗,适用于对稳定性、可靠性要求高的高频场合。

3、电容并联及反谐振:

不同容值的电容并联情况下,会因为每个电容的谐振频率不同导致工作频率处于两个(多个)谐振频率之间时,一些电容表现为容性,一些表现为感性,这就形成了一个LC并联谐振电路;

当处于谐振状态时,电感和电容之间进行周期性的能量交换,这样流经电源层的电流极小,电源层表现为高阻状态,这种情况即为:反谐振。

而如何降低反谐振带来的影响,就是电源完整性设计中的重点。

4、电容在PCB的摆放

实际中高频的小电容对瞬间电流的反应最快,所以高速设计中的关键就是高频小电容的处理,尽可能摆放的距离芯片电源引脚接近,以达到最佳旁路效果。

1660

1660

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?