偶数分频

N为偶数,使用一个计数器计数到N/2 -1,然后时钟输出取反,即完成了N分频。

时序图:

代码:

module div_even(

input clk,

input rst_n,

output reg clk_out

);

parameter N = 2; //N=2,此时M=4,即系统四分频

reg [31:0] counter;

always @(posedge clk or posedge rst_n) begin

if (!rst_n)

counter <= 0;

else if (counter == N-1)

counter <= 0;

else

counter <= counter + 1;

end

always @(posedge clk or posedge rst_n) begin

if (rst_n)

clk_out <= 0;

else if (counter == N-1)

clk_out <= ~clk_out;

end

endmodule

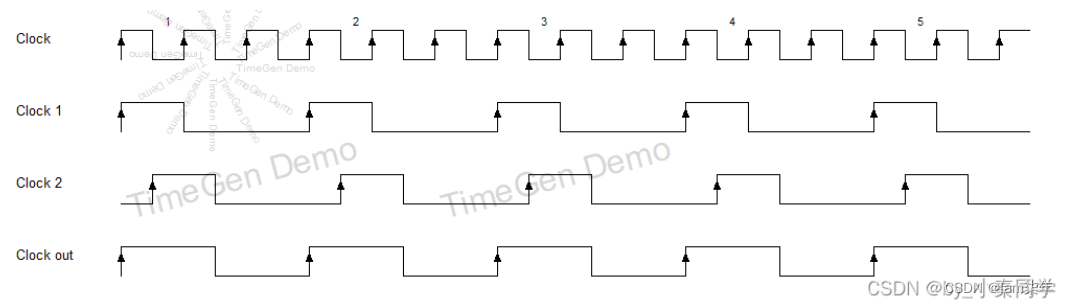

奇数分频

时序图:

50%占空比(占空比是指高电平占整个电路工作周期的百分比,50%占空比也就意味着高电平与低电平时长相等),奇数分频代码:

//奇数分频,50%占空比

module div_odd (

input clk,

input rst_n,

output clk_out

);

parameter N = 3;

reg [31:0] count;

reg clk_1,clk_2;

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

count <= 0;

else if (count== (N-1))

count<= 0;

else

count <= count+ 1;

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

clk_1 <= 0;

else if (count== (N-1))

clk_1 <= ~clk1;

else

clk_1 <= clk_1;

end

always @(negedge clk or negedge rst_n) begin

if (!rst_n)

clk_2 <= 0;

else if (div_cnt == ((N-1)/2))

clk_2 <= ~clk2

else

clk_2 <= clk_2;

end

assign clk_out = clk_1 | clk_2;

endmodule

参考:verilog时钟分频

参考:verilog各种分频大全

85

85

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?