Verilog 中always块组合逻辑中“非阻塞赋值”语句执行顺序

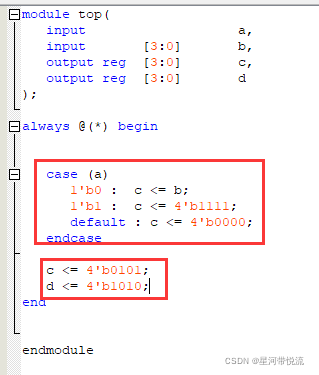

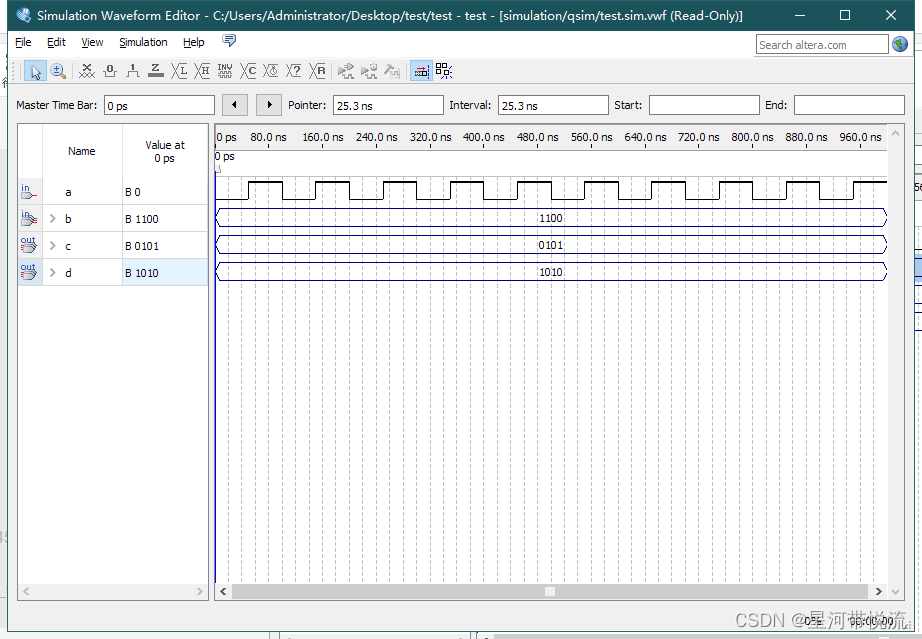

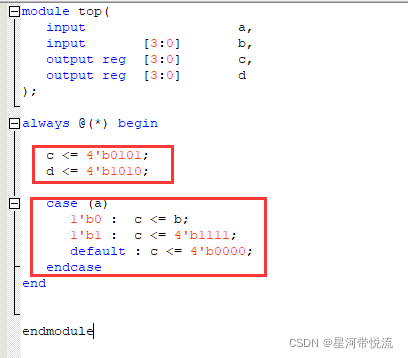

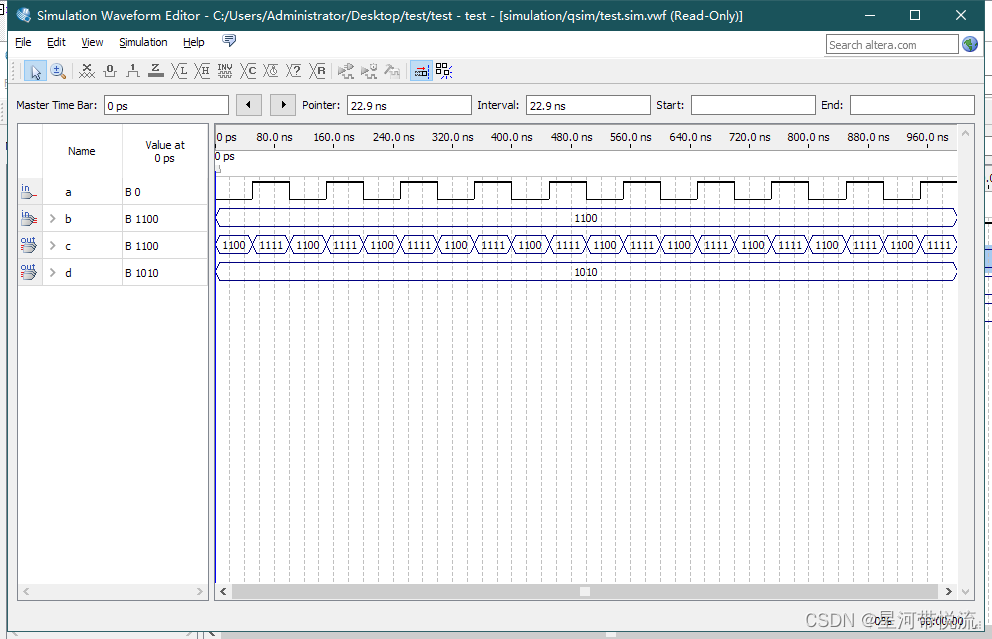

按照所学,always块中使用非阻塞赋值,在块结束时一起赋值,是一种“并行” 的执行顺序,但是如果always块中存在case、if…else等,在其内部和外部同时对同一reg进行赋值操作,那么会发生什么呢

============================================================================

============================================================================

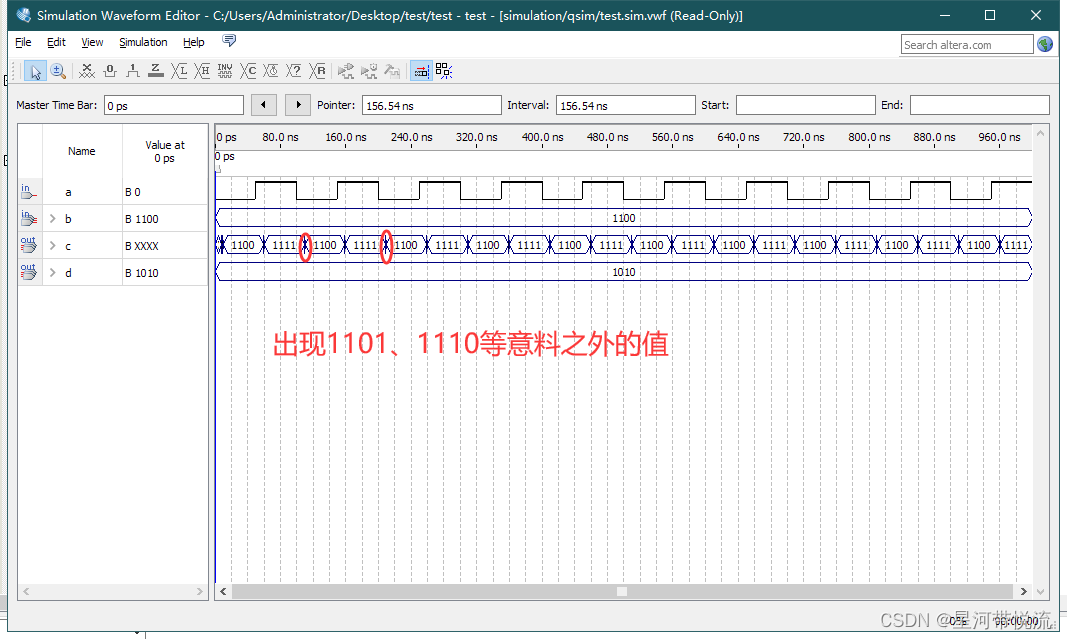

可以看出,不同的顺序,结果是由最后一次赋值决定的,其他测试也一样,只要有两次对同一个变量赋值,只会由最后一次赋值确定

可以看出,不同的顺序,结果是由最后一次赋值决定的,其他测试也一样,只要有两次对同一个变量赋值,只会由最后一次赋值确定

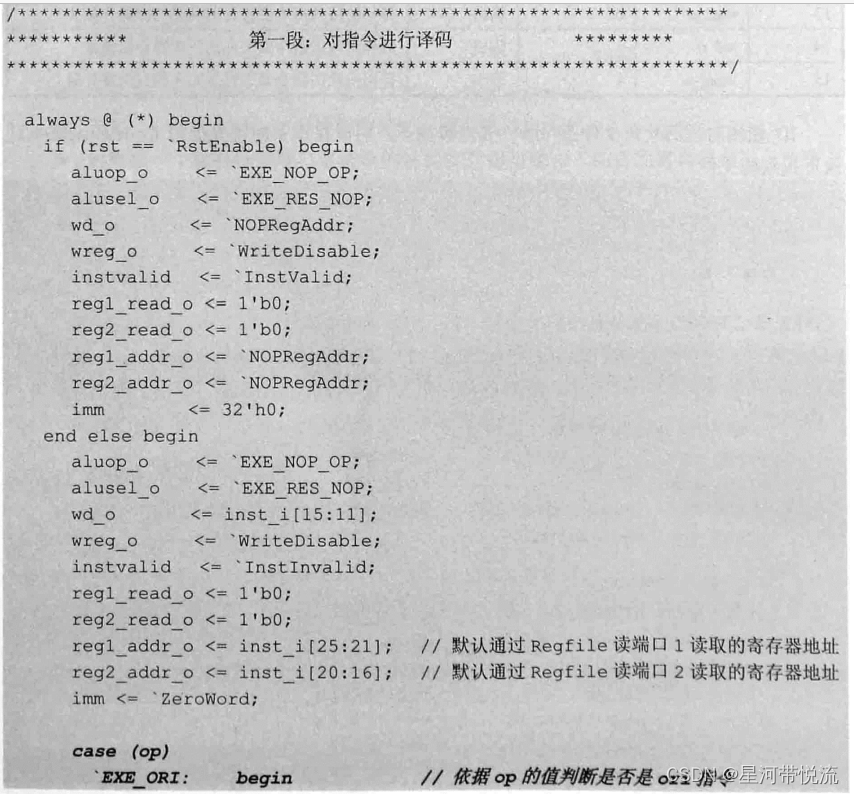

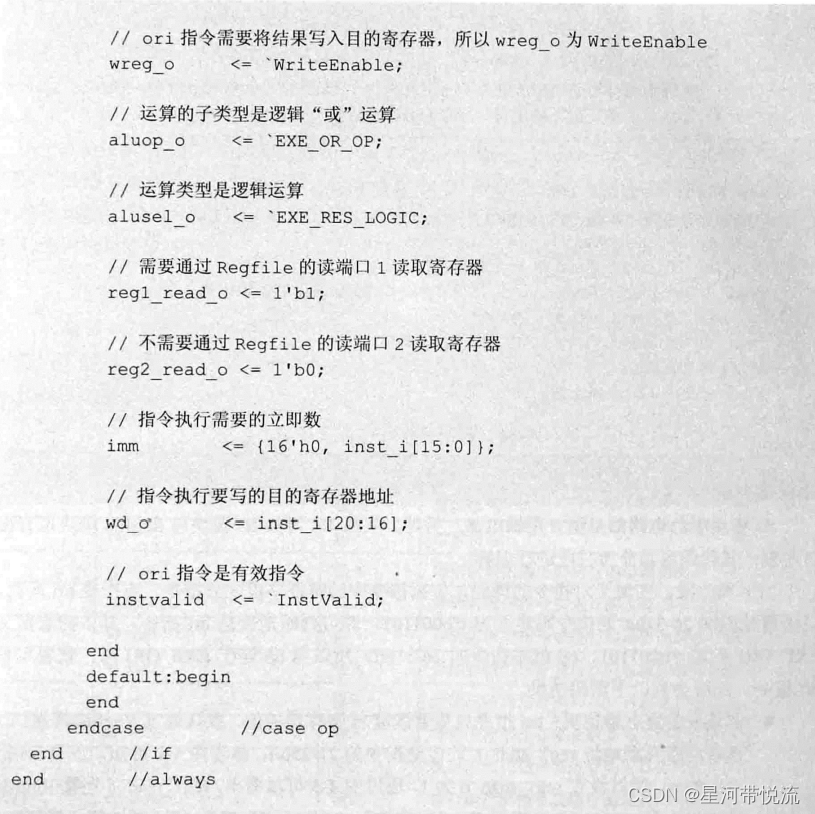

这个问题是我在学习《自己动手写CPU》一书时遇到的,书中代码如下:

书中这里在else分支里对多个变量进行了两次赋值,第一次是在case外,第二次是在case中,那么根据上面的结论,是否在case外的赋值是没有意义的,甚至在Run Timing Simulation中会导致亚稳态:

不知道是我理解错了,还是书中的错误,希望有大佬帮忙解答!

不知道是我理解错了,还是书中的错误,希望有大佬帮忙解答!

7260

7260

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?