实验的开发板:黑金AX516 开发板

本篇讲解如何向USB协议芯片写入数据。

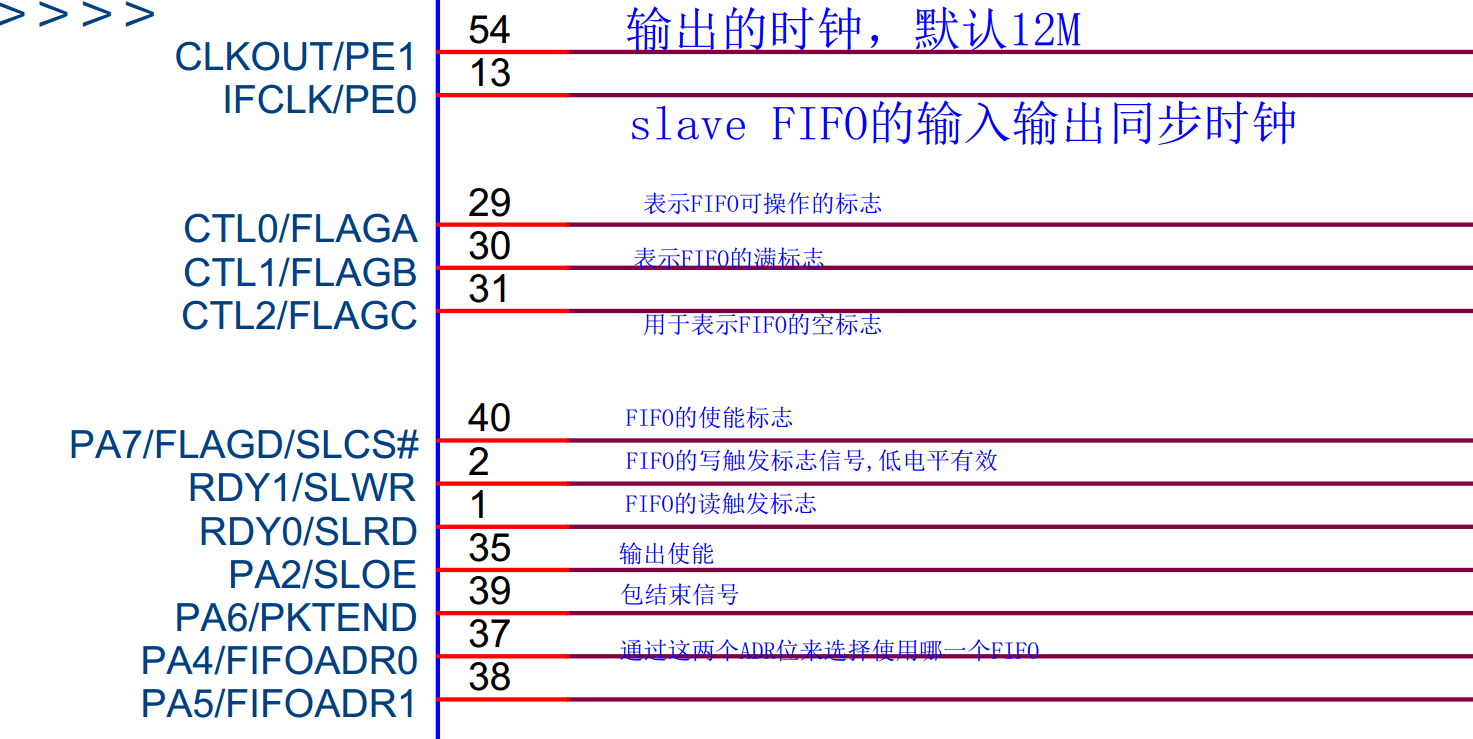

1.USB协议芯片引脚功能

主要的需要配置的功能引脚

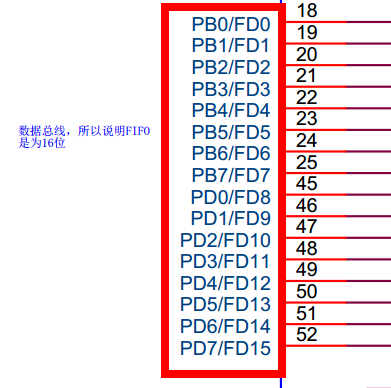

数据引脚

有用的引脚

ifclk , //同步时钟

s_rst_n ,

usb_full , //满标志

usb_empty , //空标志

usb_slcs , //FIFO使能标志

usb_slwr , //FIFO写触发标志

usb_slrd , //FIFO的读触发标

usb_sloe , //FIFO的输出使能

usb_fifoadr , //FIFO片选信号

usb_fdata //FIFO的数据信号

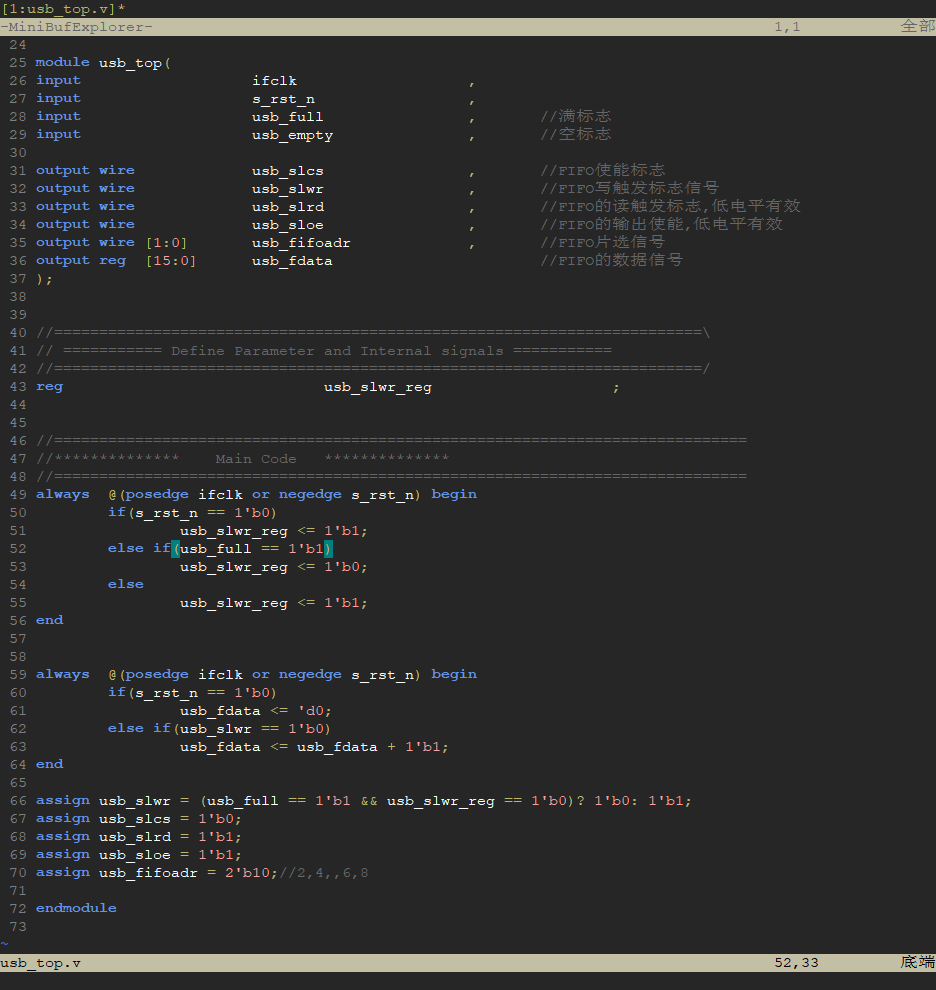

2.写测试代码

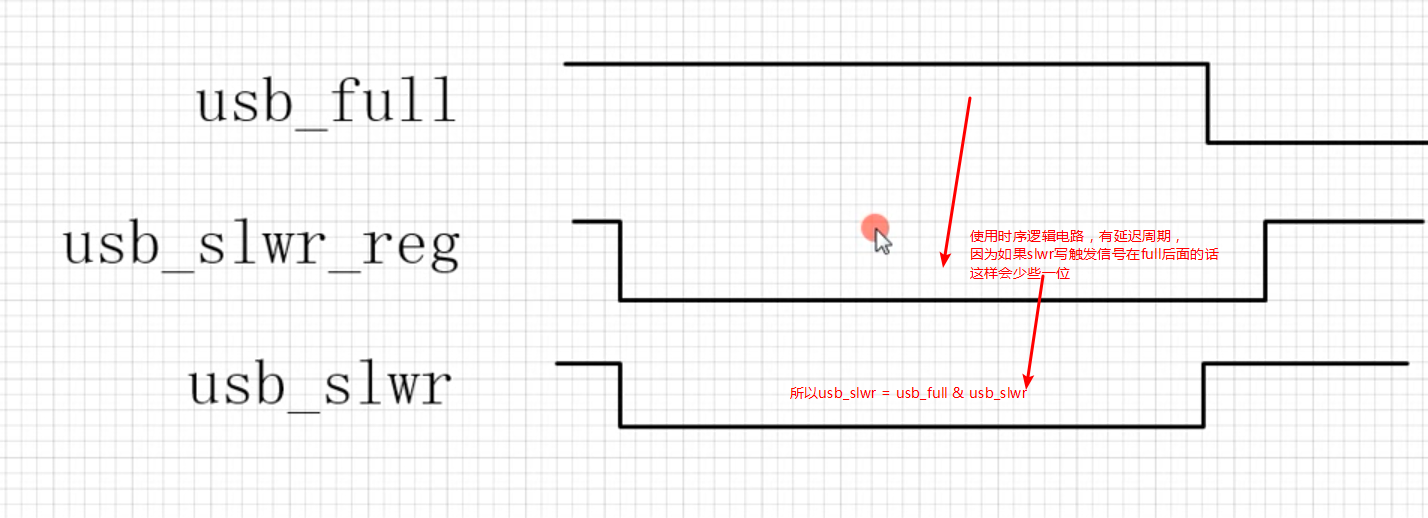

波形图:

代码主要功能是需要拉低usb_slwr写触发信号,去触发写操作。

然后将代码编译下载到板子上。

测试FIFO的

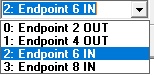

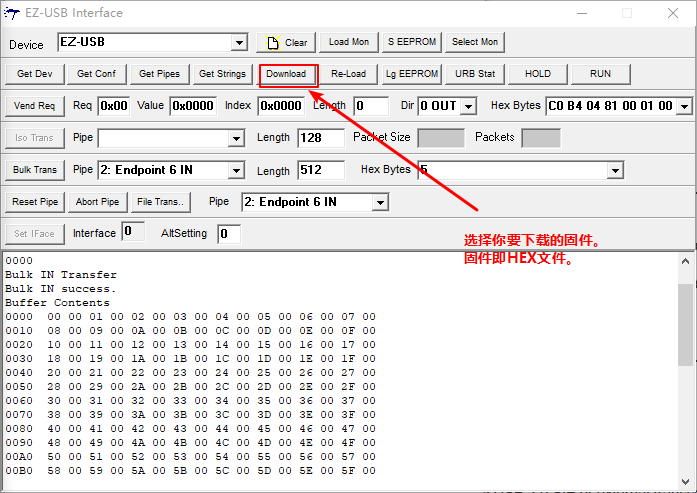

在USB软件这个有个FIFO选择,一个USB有4个FIFO,分别是2,4,6,8.

这里的IN表示:USB TO PC

OUT PC TO USB

代码中我们选择IN的endpoint 6 in.3.将固件下载到USB芯片中。

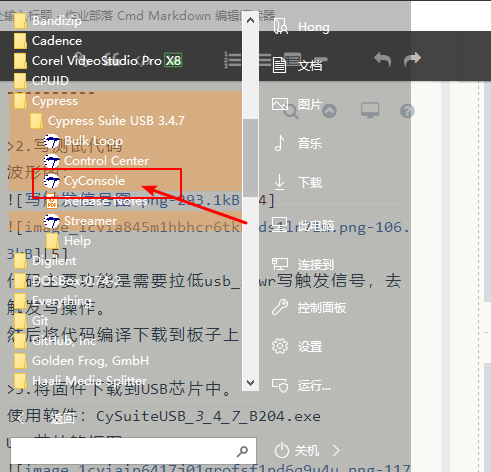

使用软件:CySuiteUSB_3_4_7_B204.exe

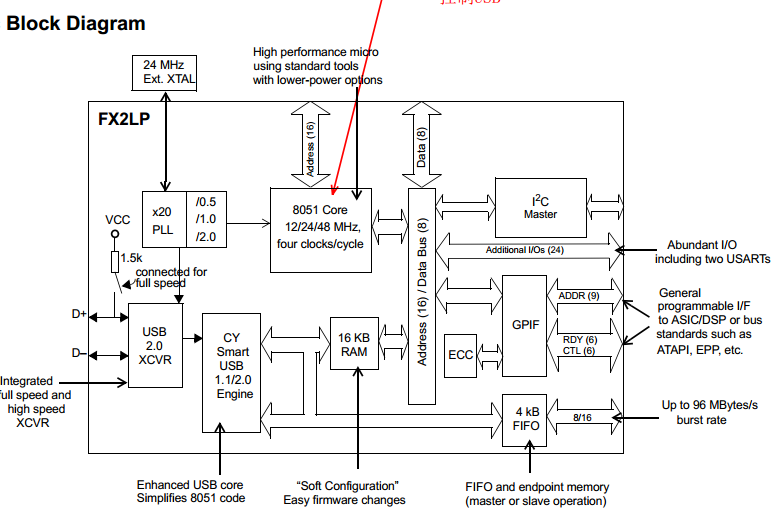

USB芯片的框图

他里面有个8051的核,固件就是相当于下载进去的程序,即USB协议代码。

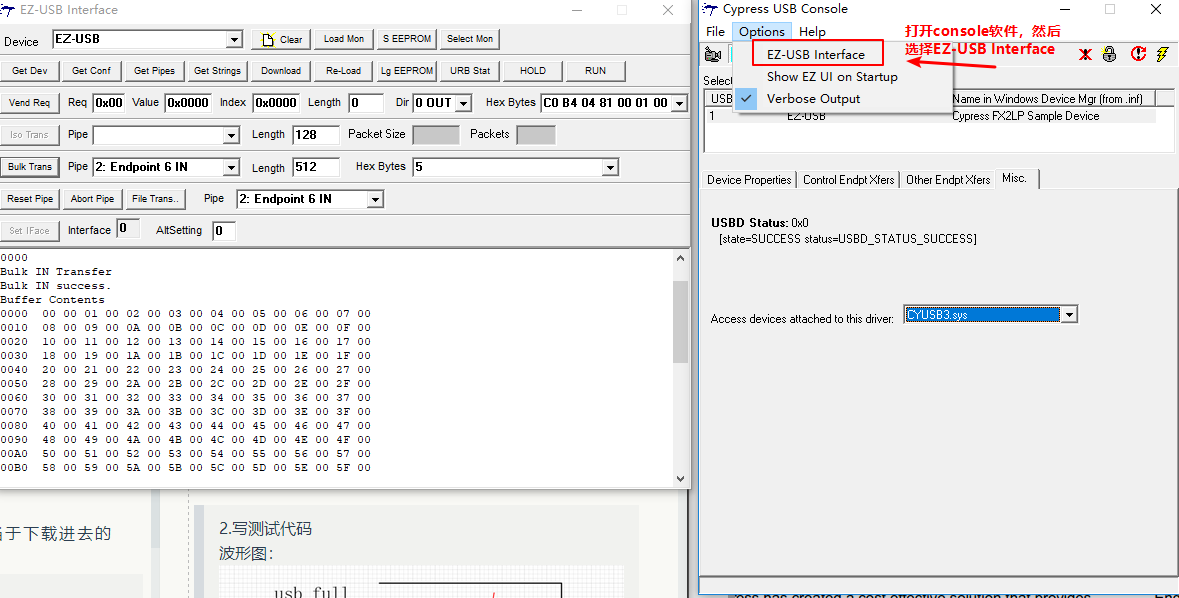

打开软件

然后选择Interface

点击download

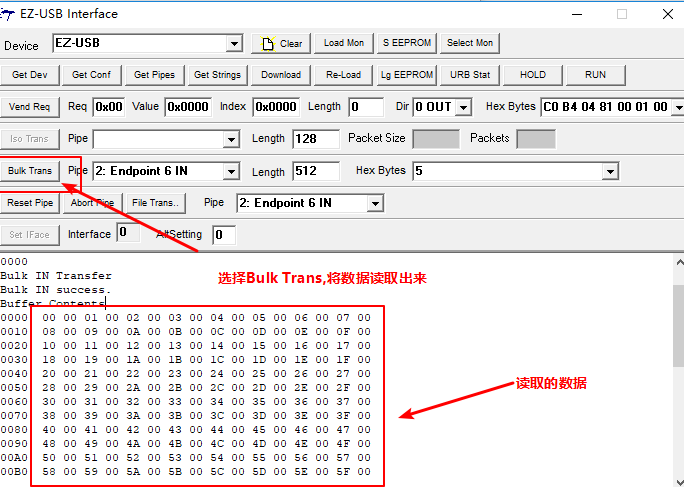

4.读取FIFO的数据,看写入是否正常

这个USB数据是采用大端模式的,所以高位字节数据存放在内存的低地址,低位字节数据存在高位地址。

大端小端模式的区别:

1) Little-Endian就是低位字节排放在内存的低地址端,高位字节排放在内存的高地址端。

2) Big-Endian就是高位字节排放在内存的低地址端,低位字节排放在内存的高地址端。

1110

1110

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?