IIC 接口

IIC总线概述

IIC总线简介

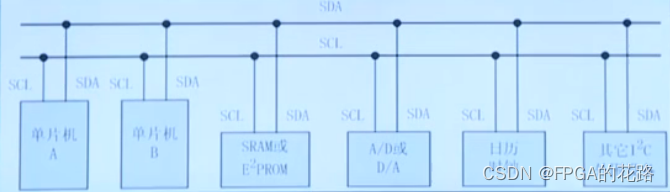

IIC总线是Philips公司在八十年代初推出的一种串行、半双工总线,主要用于近距离、低速的芯片之间的通信;IIC总线有两根双向的信号线一根数据线 SDA 用于收发数据,一根时钟线 SCL 用于通信双方时钟的同步;IIC总线硬件结构简单,成本较低,因此在各个领域得到了广泛的应用。

IIC总线是一种多主机总线,连接在IIC总线上的器件分为主机和从机,主机有权发起和结束一次通信,而从机只能被主机呼叫;当总线上有多个主机同时启用总线时,IIC也具备冲突检测和仲裁的功能来防止错误产生;每个连接到IIC总线上的器件都有一个唯一的地址(7bit),且每个器件都可以作为主机也可以作为从机(同一时刻只能有一个主机),总线上的器件增加和删除不影响其他器件正常工作;IIC总线在通信时总线上发送数据的器件为发送器,接收数据的器件为接收器;

IIC总线通信过程

-

主机发送起始信号启用总线;

-

主机发送一个字节数据指明从机地址和后续字节的传送方向;

-

被寻址的从机发送应答信号回应主机;

-

发送器发送一个字节数据;

-

接收器发送应答信号回应发送器;

… …(循环步骤4、5)

-

通信完成后主机发送停止信号释放总线。

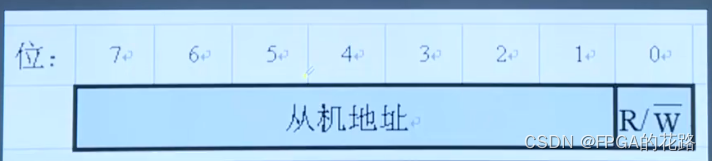

IIC总线寻址方式

IIC总线上传送的数据是广义的,既包括地址,又包括真正的数据。

主机在发送起始信号后必须先发送一个字节的数据,该数据的高7位为从机地址,最低位表示后续字节的传送方向,'0’表示主机发送数据,'1’表示主机接收数据;总线上所有的从机接收到该字节数据后都将这7位地址与自己的地址进行比较,如果相同,则认为自己被主机寻址,然后再根据第8位将自己定为发送器或接收器。

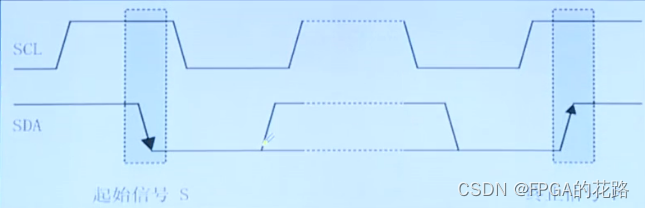

IIC总线信号实现

起始信号、停止信号

-

SCL为高电平时, SDA由高变低表示起始信号

-

SCL为高电平时, SDA由低变高表示停止信号

-

起始信号和停止信号都是由主机发出,起始信号产生后总线处于占用状态停止信号产生后总线处于空闲状态

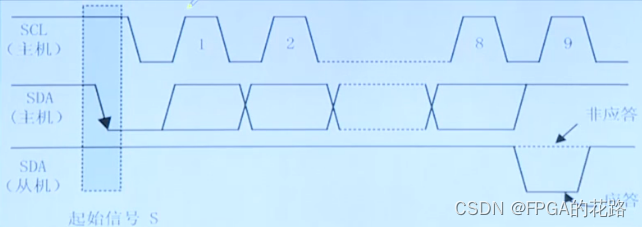

字节传送与应答

IIC总线通信时每个字节为8位长度,数据传送时,先传送最高位,后传送低位,发送器发送完一个字节数据后接收器必须发送1位应答位来回应发送器即一帧共有9位

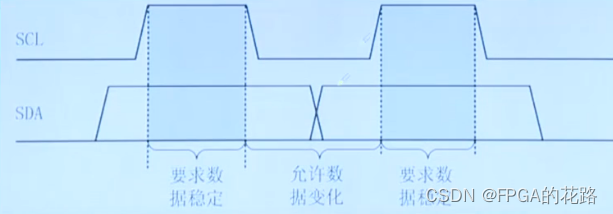

同步信号

IIC总线在进行数据传送时,时钟线SCL为低电平期间发送器向数据线上发送一位数据,在此期间数据线上的信号允许发生变化,时钟线SCL为高电平期间接收器从数据线上读取一位数据,在此期间数据线上的信号不允许发生变化,必须保持稳定。

IIC典型时序

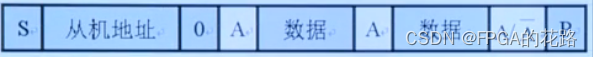

- 主机向从机发送数据

- 停止发送有两种情况:①主机不想发了;②从机不想应答了。但是终止信号只能是主机发出

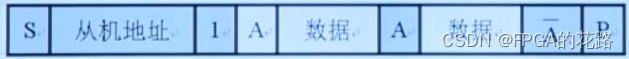

- 从机向主机发送数据

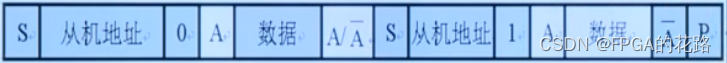

- 主机先向从机发送数据,然后从机再向主机发送数据

- 变更操作方向的时候不用发停止信号,如果发了停止信号再变更,有可能总线使用权就被别的主机抢走了

注:阴影部分表示数据由主机向从机传送,无阴影部分则表示数据由从机向主机传送;A表示应答,A非表示非应答,S表示起始信号,P表示终止信号

别的主机抢走了

注:阴影部分表示数据由主机向从机传送,无阴影部分则表示数据由从机向主机传送;A表示应答,A非表示非应答,S表示起始信号,P表示终止信号

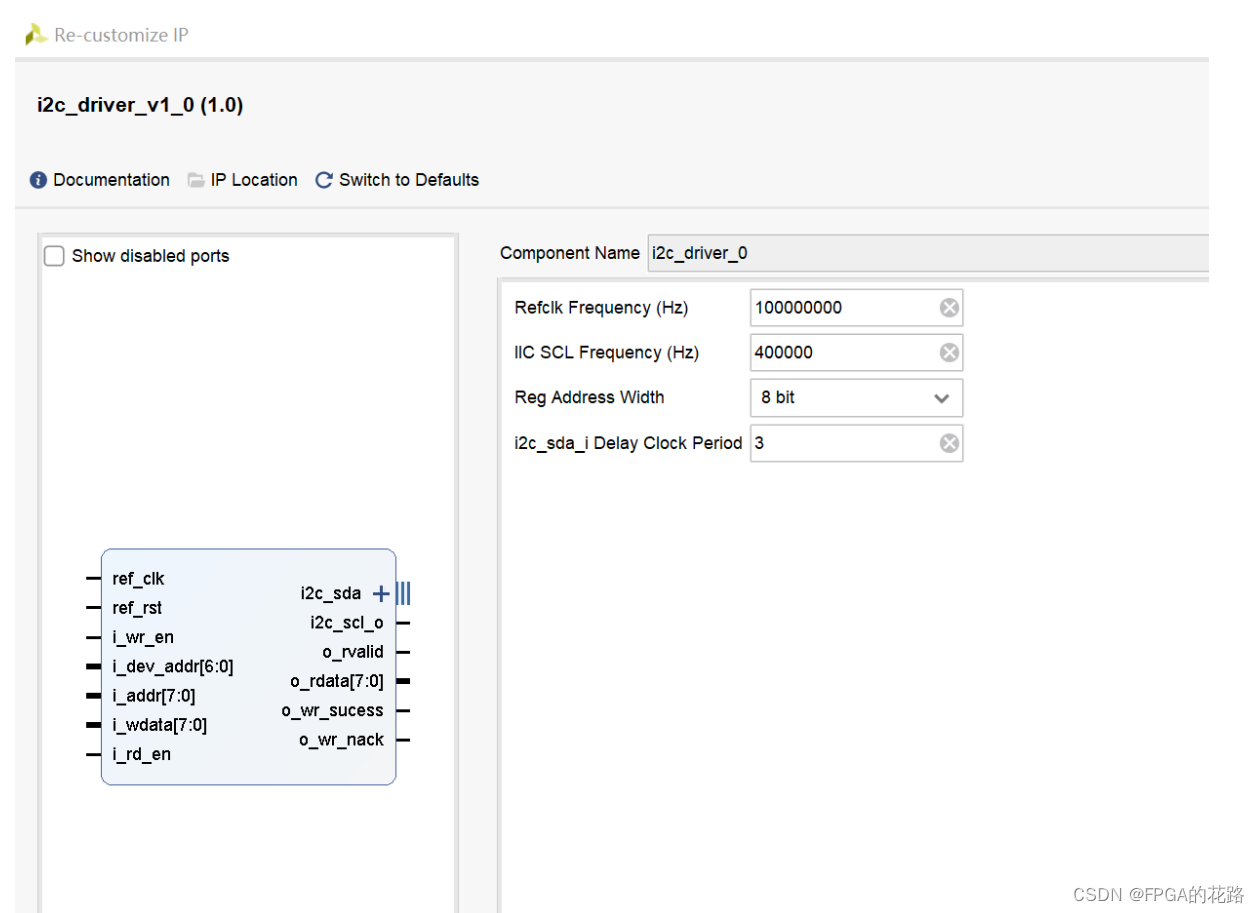

IP设计

IP 例化界面

IP 接口

| 信号 | 方向 | 说明 |

|---|---|---|

| i2c_scl_o | output | i2c 时钟信号 |

| i2c_sda_i | input | i2c 数据输入信号 |

| i2c_sda_o | output | i2c 数据输出信号 |

| i2c_sda_t | output | i2c 数据三态使能信号,高电平为输入,低电平为输出 |

| i_wr_en | input | 写使能 |

| i_dev_addr[6:0] | input | 从设备地址 |

| i_addr[ADDR_W-1:0] | input | 读写操作地址,支持位宽8/16bit |

| i_wdata[7:0] | input | 写数据。单字节写操作时写使能在 o_wr_sucess 置位时拉低;多字节写操作时写数据在 o_wr_sucess 置位时更新数据 |

| i_rd_en | input | 读使能。若要停止读操作时,在 o_rvalid 置位后拉低读使能信号 |

| o_rvalid | output | 读数据有效指示,高脉冲有效 |

| o_rdata[7:0] | output | 读数据 |

| o_wr_sucess | output | 完成一个字节写操作指示,高脉冲有效 |

| o_wr_nack | output | 写操作未响应指示 |

若要变更操作方向,在写使能或者读使能信号拉低前置位读使能或者写使能,这样可以避免发送停止信号,导致总线使用权被抢走。

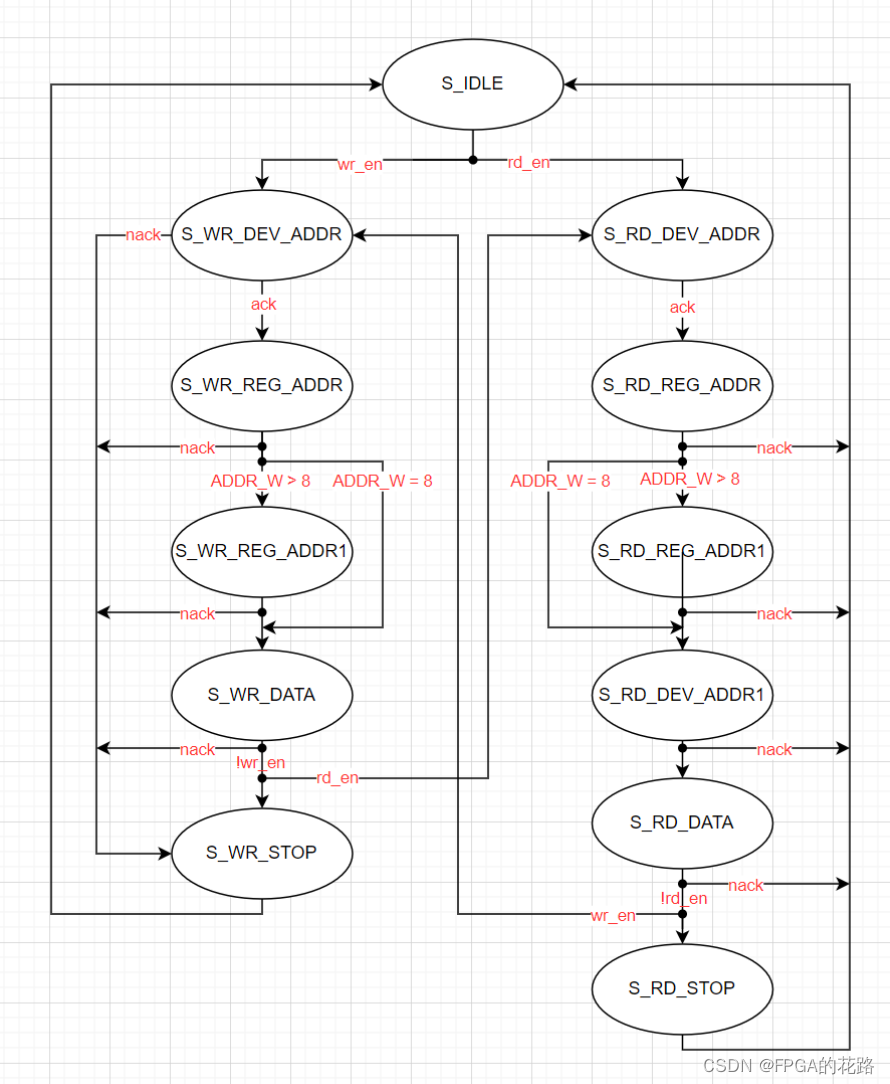

IP 状态机

IP 验证

使用 24LC04 EEPROM 进行读写测试。

-

24LC04 EEPROM 容量为 4Kbit(2*256*8bit),由 2 个 256 byte 的 block 组成,通过 IIC 总线进行通信。

-

设备地址为 7‘b1010xxx,bit[0]表示 block 地址选择,对应两个 block,操作地址为 8bit,对应 256 byte 数据。

-

支持页操作,长度为 16 byte,超过该长度会回卷

469

469

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?