第1章 集成电路物理设计方法

1、技术发展三个方面:工艺节点(nm)、逻辑门数(百万门)、晶圆直径(mm、英寸)

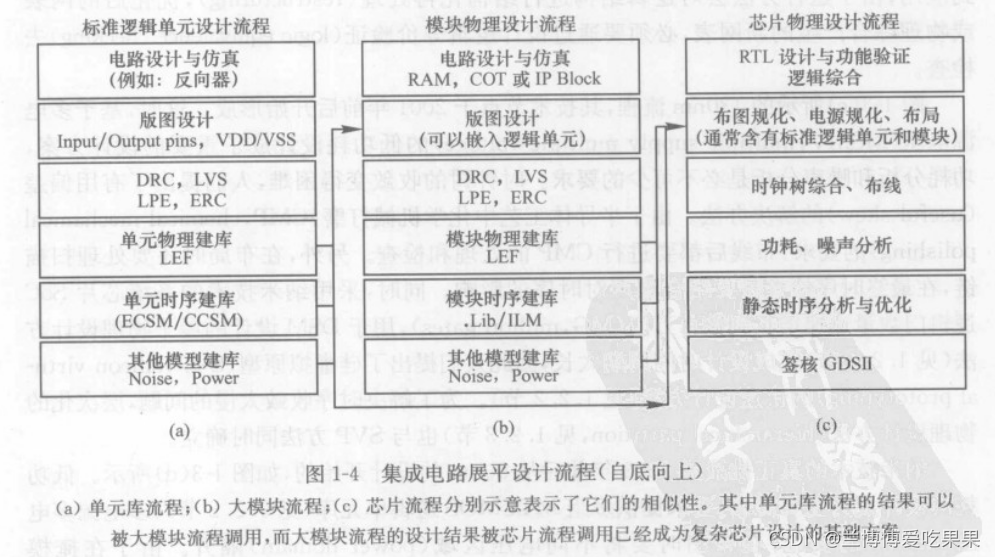

2.1、展平式物理设计流程(自底向上):

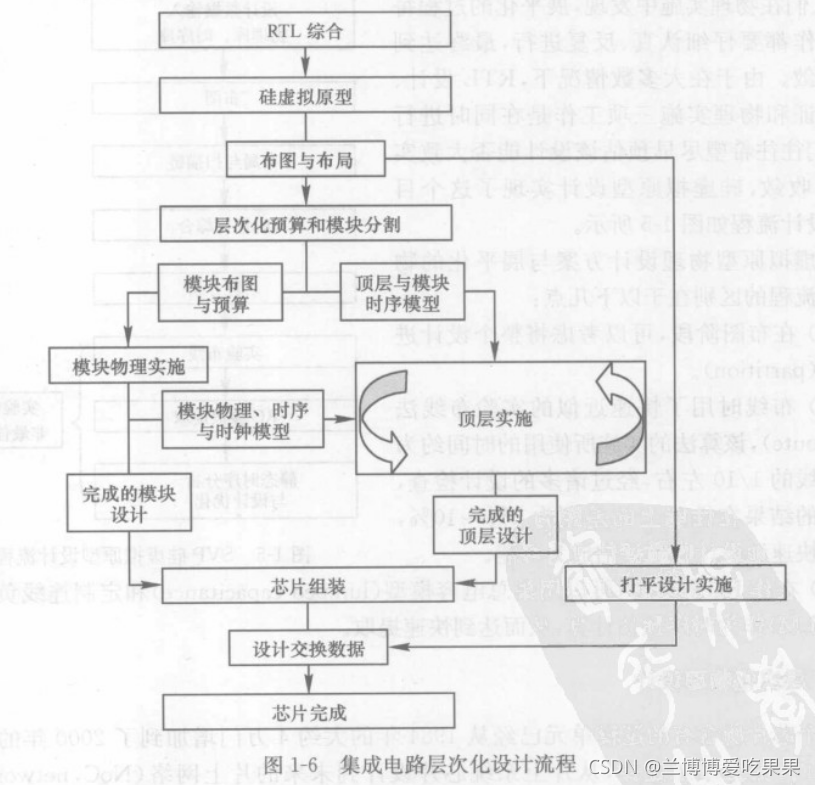

2.2、层次化物理设计流程(自上向下):

每个模块的物理设计过程都是一个完整的展平化物理设计过程,它假定每个模块都是已收敛的黑匣子。层次化物理设计方案的最大优点是它将很大的设计化成多个小设计。

3、设计收敛三大部分:数据系统、优化引擎、分析引擎

数据系统由读取、处理和储存的功能组成;优化引擎主要指基于算法去实现逻辑优化、布局优化和布线优化的EDA工具方法;分析引擎主要是指用于时序分析、功耗分析和噪声(信号完整性)分析的EDA工具。

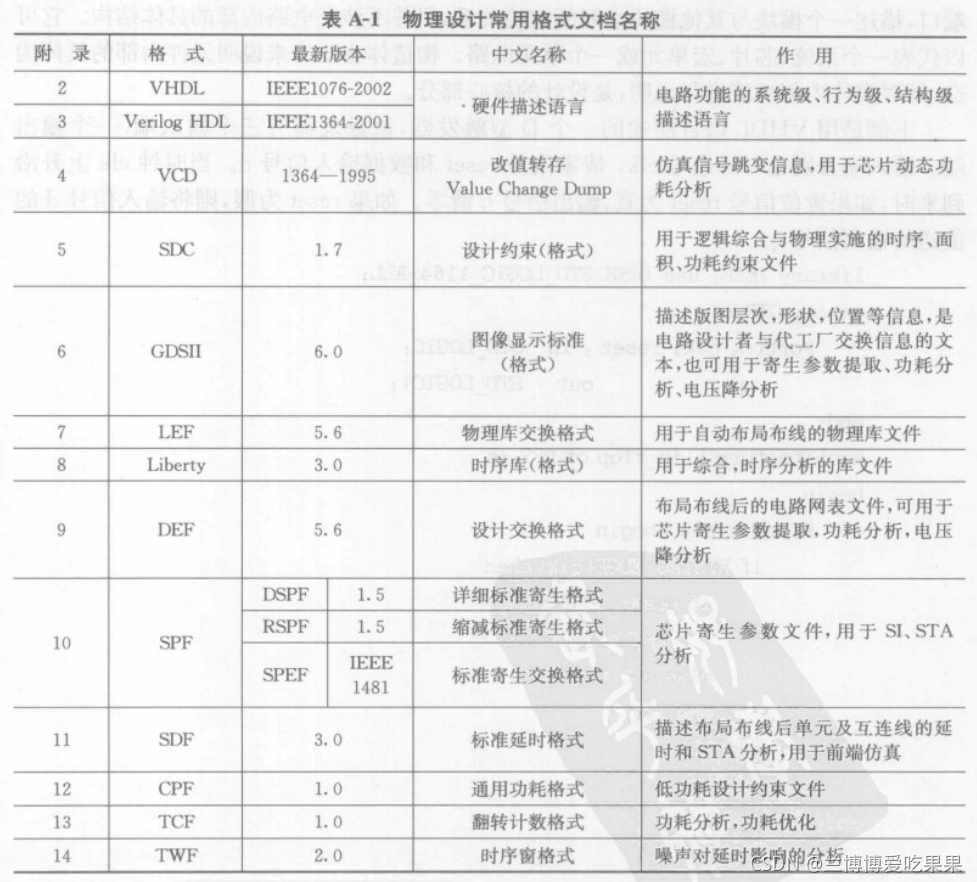

4、物理设计常用格式

第2章 物理设计建库与验证

1、设计规则检查(DRC)和电路规则检查(LVS)是物理验证的两项主要工作。

1.1、DRC主要目的是检查版图中所有因违反设计规则而引起潜在断路、短路或不良效应的物理验证过程。它对版图使用图形运算函数找出那些违反规则的地方。

1.2、LVS主要目的是验证版图与电路原理图的电路结构是否一致。内容包括:所有信号的电气连接关系是否一致;器件类型尺寸是否一致。它将原始电路图的网表(门级Verilog网表,需要转换为SPICE网表)与版图中提取出来的电路图的网表(SPICE网表)加以比较。

2、版图(电容)寄生参数提取(LPE)和寄生电阻提取(PRE)

3、一个完整的单元库一般包含这些逻辑单元类别:1) 标准单元 2) 模块宏单元 3) 输入输出单元(I/O)

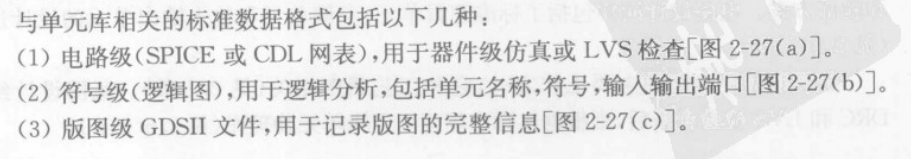

4、标准数据格式:

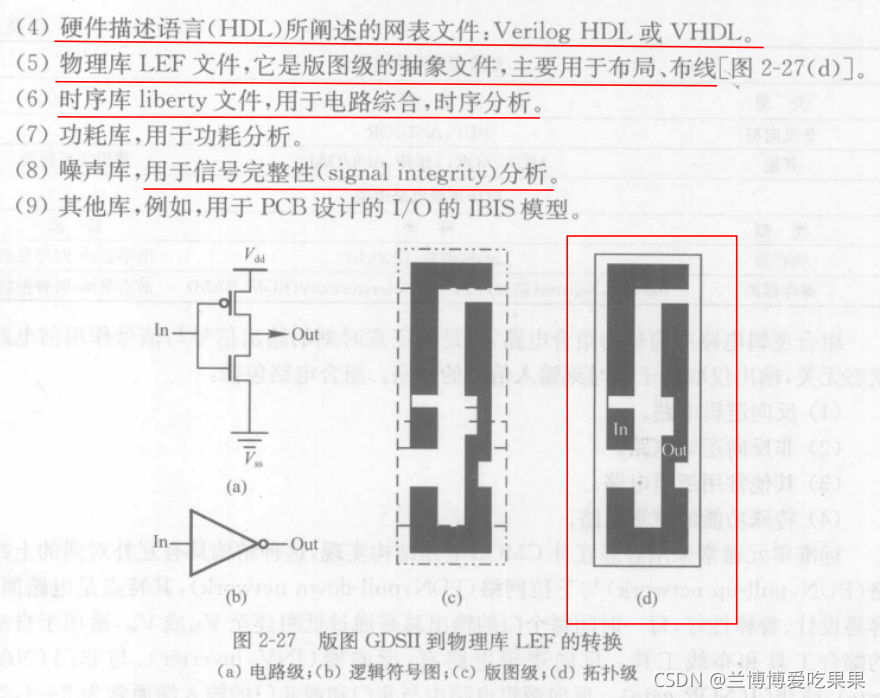

5、物理库文件(LEF格式)及时序库文件(.lib格式)

物理库文件是对版图的抽象描述。

时序库文件描述的是单元库各个单元时序信息。

第3章 布图规划和布局

1、布图规

本文详细介绍了集成电路物理设计的各个方面,包括技术发展、设计流程、设计收敛、物理验证、布图规划、时钟树综合、布线、静态时序分析、功耗分析和信号完整性。同时,讨论了低功耗设计策略和技术,并强调了最终验证和签核的重要性。内容涵盖了DRC、LVS、布图规划、时钟树综合、布线优化、功耗计算和信号完整性分析等多个关键步骤,为数字集成电路设计提供了全面的指导。

本文详细介绍了集成电路物理设计的各个方面,包括技术发展、设计流程、设计收敛、物理验证、布图规划、时钟树综合、布线、静态时序分析、功耗分析和信号完整性。同时,讨论了低功耗设计策略和技术,并强调了最终验证和签核的重要性。内容涵盖了DRC、LVS、布图规划、时钟树综合、布线优化、功耗计算和信号完整性分析等多个关键步骤,为数字集成电路设计提供了全面的指导。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

705

705

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?