第一章 集成电路物理设计方法

1.1 数字集成电路设计挑战

1.2 数字集成电路设计流程

前两节内容讲述的是数字集成电路发展与流程,知识体系比较宏观和简单,请读者自行了解即可。

1.3 数字集成电路设计收敛

实现设计收敛任务:①数据系统;②优化引擎;③分析引擎

数据系统:由读取、处理和储存的功能组成数据系统由读取、处理和储存的功能组成。(核心:数据)

优化引擎:主要是指基于算法去实现逻辑优化、布局优化和布线优化的EDA工具方法。(核心:优化EDA)

分析引擎:主要是指由设计工程师借助EDA工具用于时序分析、功耗分析和噪声(信号完整性)分析的EDA工具。(核心:EDA分析,对于芯片物理设计,关键在于分析引擎)

1.3.1 时序收敛

时序的要求:通过 SDC去表达、约束和检验的。

静态时序分析任务:寻找最长延时路径以及最坏情况下的延时。

拓展SSTA概念:

1.3.2 功耗分析

1.功耗分析 静态功耗+动态功耗

静态功耗分析:时序库→器件功耗数据 电压降和电迁移效应:物理库→金属物理工艺数据

动态功耗分析:需要设计仿真数据 目前适用于从功能验证、RTL综合、形式验证、到布局布线约束的通用功耗格式文件(CPF,cemmon power format)目前正得到极大重视和应用。

2.低功耗设计

注意:芯片功耗最大的为时钟电路的功耗,主要解决技术是采用门控电路、时钟数综合和多电源电压

1.3.3 可制造性分析

设计检验、设计产额和制造、设计质量

小结:

时序收敛的目的是保证芯片在要求的工作环境中,达到理想的性能,它通过静态时序分析等手段,预测芯片在各种条件下的工作频率,同时借助于约束和优化引擎从而达到路径优化最终实现主频的提高;(实现功能)

功耗分析的结果则体现了芯片的能耗大小,芯片内部电压降和电流的分布,也反映了芯片工作稳定的程度,我们需要将芯片的功耗、压降电迁移等参数控制在一定的范围内;(满足能耗)

可制造性设计是纳米工艺条件下所研究的一个热点,它的目的是提高良品率,从而降低生产成本,提高产品的利润。三者相辅相成,共同指导并约束着数字集成电路的物理实现。(保证制造)

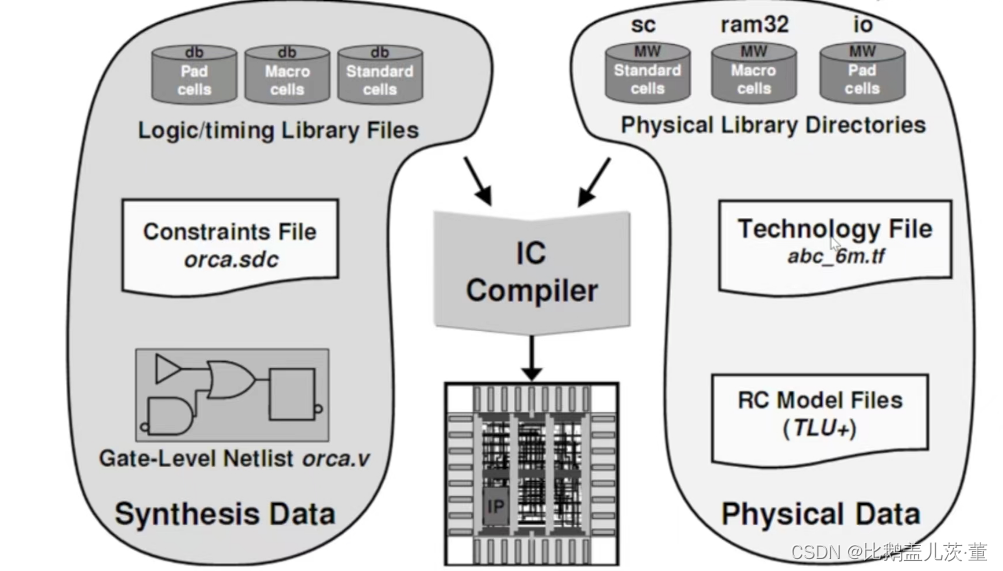

1.4 数字集成电路设计数据库

883

883

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?