一、CPU架构

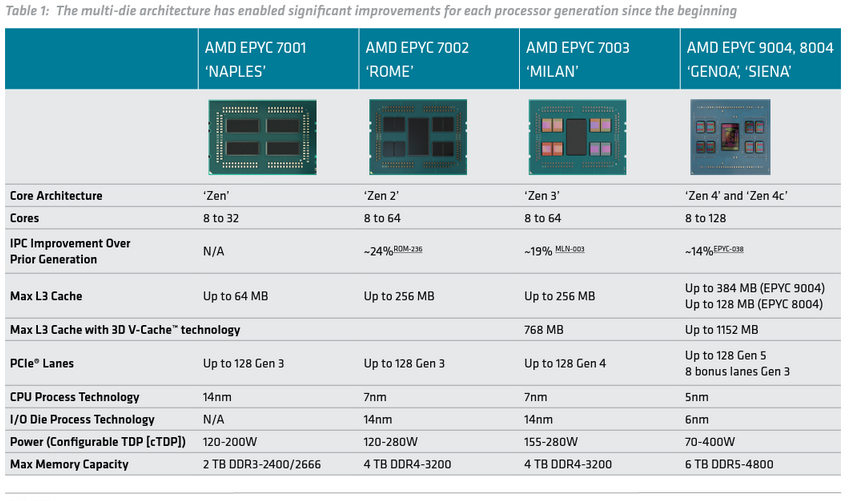

AMD服务器级处理器演进:

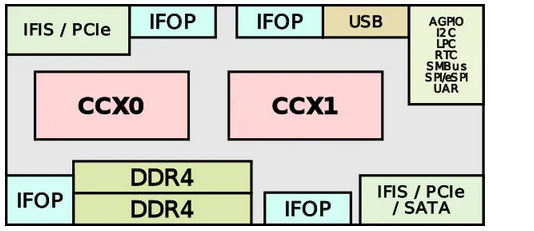

Zeppelin

参考链接:wikichip: Zeppelin

通过infinity fabric总线将单die分成多die的SoC架构,每个Die包含两个CPU核(CCX)、2各DDR通道、USB、低功耗IO以及多个IFOP和IFIS serdes接口。

如下所述中,Zen系列中的每个die都是一个Zeppelin

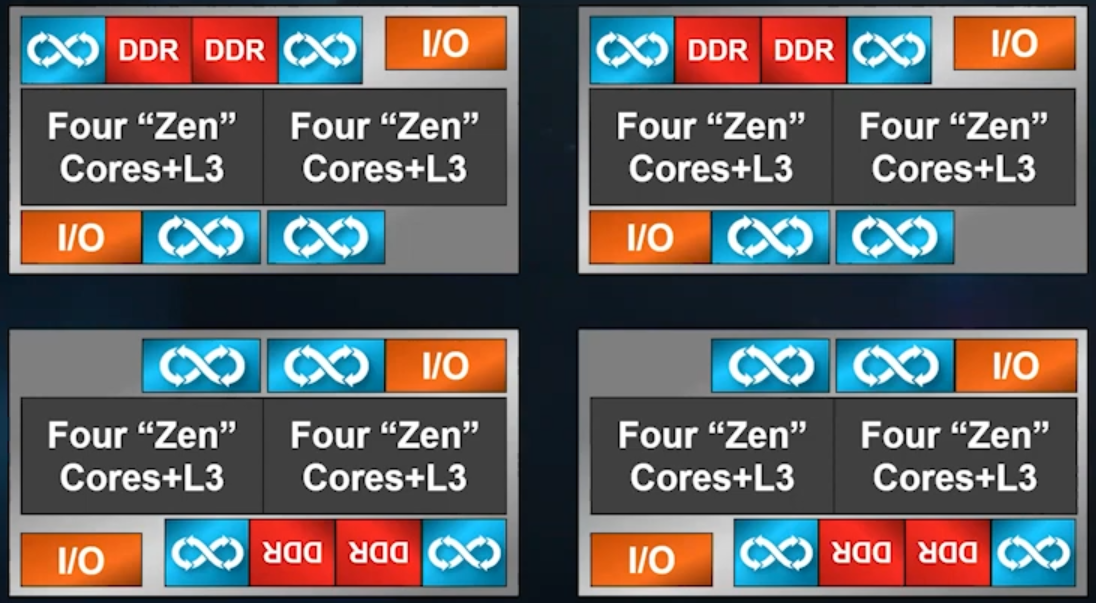

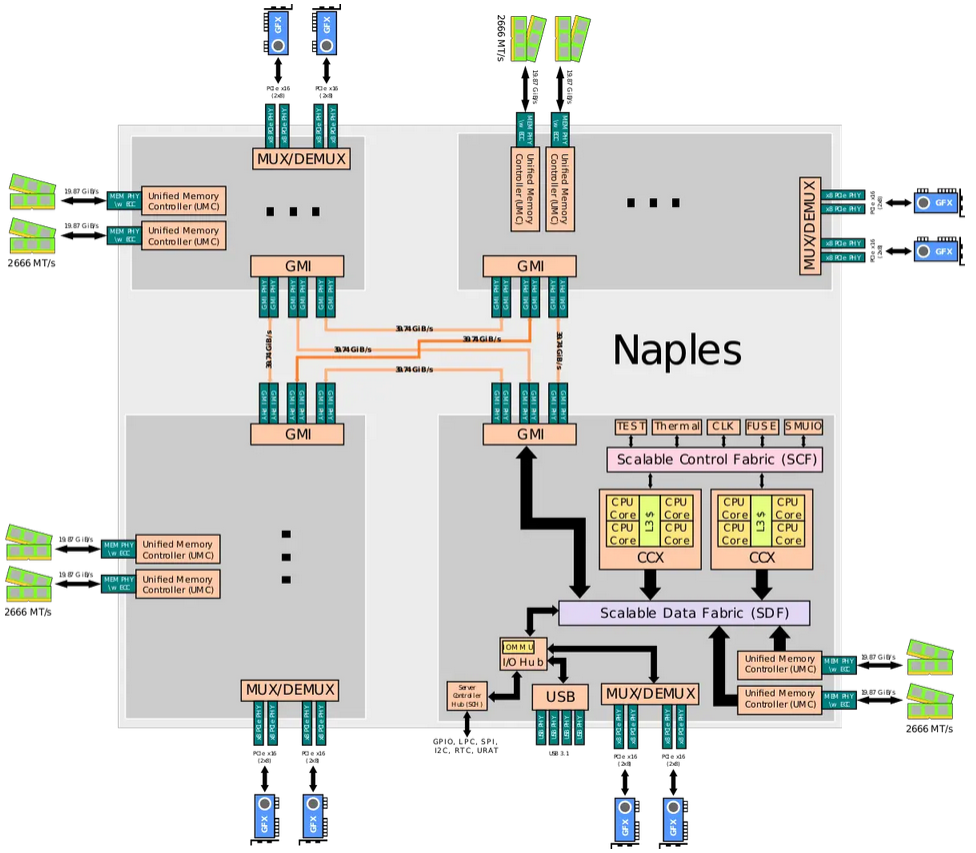

Naples(EPYC1)

4 die SoC架构

- 32个zen架构core

- 8个DDR4通道

- x128 PCIe4

- 4*213 mm2

- GF14nm

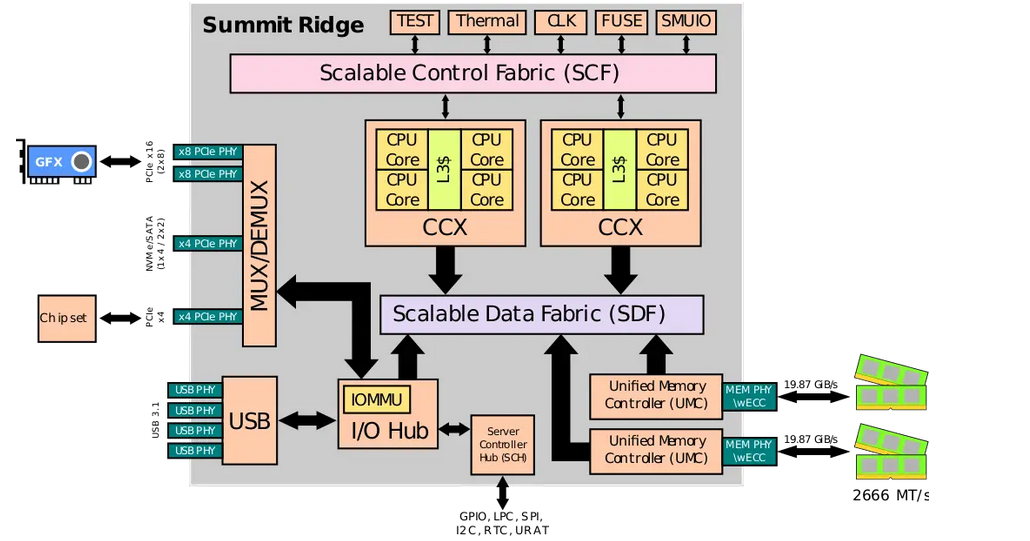

单die架构:

单die架构应用于Summit Ridge系列,即高端桌面应用场景。

- CCX

CPU complex,每个CCX包含4个CPU core,CCX间可以通过Infinity Fabric通信(SCF+SDF)

CCX间任务的分配由cache-corherent non-uniform memory access(ccNUMA-aware)实现,确保线程不会从一个CCX迁移到另一个是很重要的,由于CCX间数据通信需要额外的延迟,线程的搬移会引起不必要的性能损耗。

双die架构:

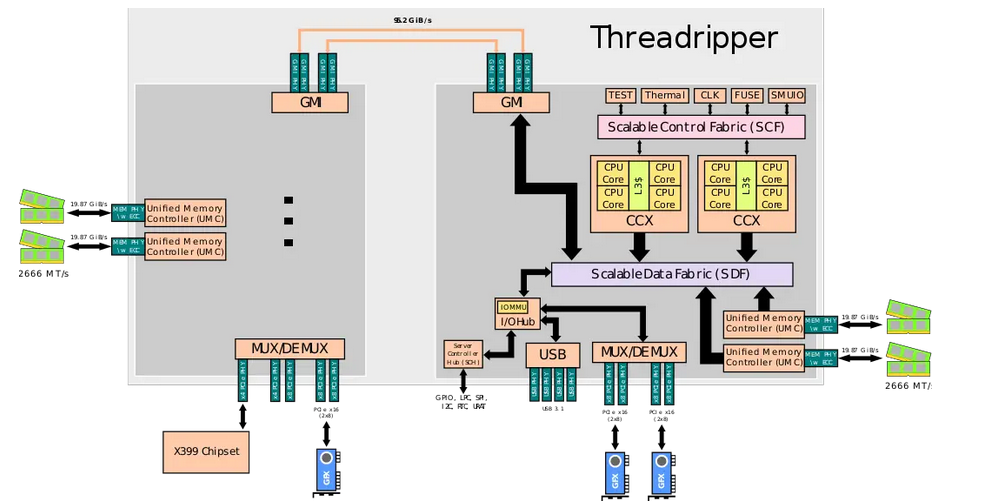

双Die架构应用于Ryzen Threadripper系列,即高性能桌面或工作站场景。

两个die通过Infinity Fabric协议处理,并经GMI(global memory interconnect)接口相连

- GMI接口

die-to-die的IFOP接口,每个时钟cycle传输16B read + 16B write。

四die架构

四die用于EPYC系列,即服务器场景。EPYC系列的die和Threadripper系列相同。

-

每个die有四组GMI接口,但只有和其他die最近的三组接口被使用

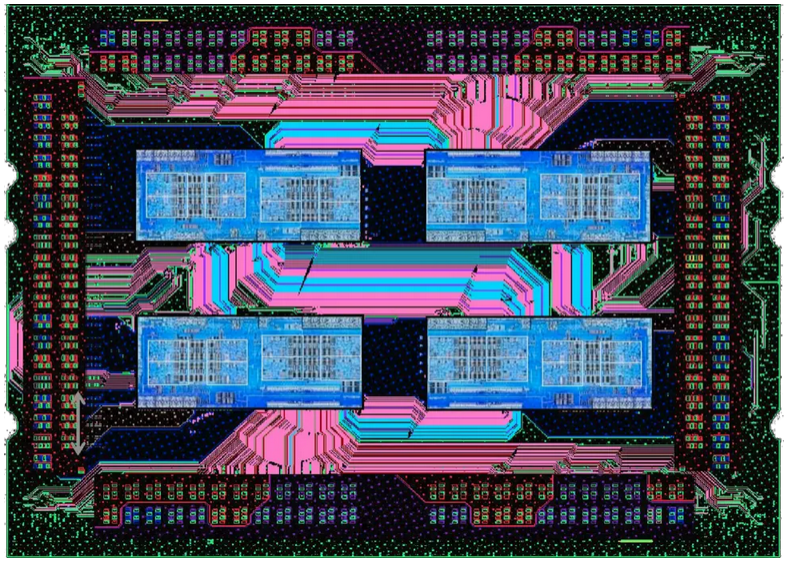

如图是EPYC系列die互连某层的布局布线图,视图上方和下方的粉色布线是die的UMC出来的接口,视图中间的粉色和蓝色布线是双向的GMI链路,左下和右上die的连接被隐藏了,左上芯片和右上芯片摆放位置相

本文详细介绍了AMD的CPU架构,包括Zen系列的单die、双die和四die架构在桌面及服务器场景的应用,如EPYC(代号Zeppelin、Rome、Milan、Genoa)系列。Zen架构采用chiplet技术,通过InfinityFabric实现die间互联,优化内存访问延迟。此外,文章还提到了GPU架构如MI200,以及3DV-cache技术提升缓存密度和性能。

本文详细介绍了AMD的CPU架构,包括Zen系列的单die、双die和四die架构在桌面及服务器场景的应用,如EPYC(代号Zeppelin、Rome、Milan、Genoa)系列。Zen架构采用chiplet技术,通过InfinityFabric实现die间互联,优化内存访问延迟。此外,文章还提到了GPU架构如MI200,以及3DV-cache技术提升缓存密度和性能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7803

7803

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?