题目

描述

要求实现一个交通红绿灯,具有红黄绿三个小指示灯和一个行人按钮,正常情况下,机动车道指示灯按照60时钟周期绿灯,5个时钟周期黄灯,10个时钟周期红灯循环。当行人按钮按下,如果剩余绿灯时间大于10个时钟,则缩短为10个时钟,小于10个时钟则保持不变。

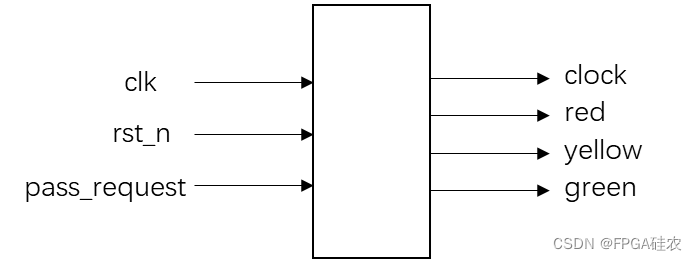

模块的信号接口图如下:

请使用VerilogHDL语言实现,并编写testbench验证功能。

代码

设计

`timescale 1ns/1ns

module triffic_light

(

input rst_n, //异位复位信号,低电平有效

input clk, //时钟信号

input pass_request,

output reg [7:0]clock,

output reg red,

output reg yellow,

output reg green

);

parameter RED=0;

parameter GREEN=1;

parameter YELLOW=2;

reg [1:0] state,next_state;

//60 clk green

//5 clk yellow

//10 clk red

always@(posedge clk,negedge rst_n)

if(~rst_n)

state<=RED;

else

state<=next_state;

always@(*)

begin

case(state)

RED:if(clock==1)

next_state=GREEN;

else

next_state=RED;

YELLOW:if(clock==1)

next_state=RED;

else

next_state=YELLOW;

GREEN:if(clock==1)

next_state=YELLOW;

else

next_state=GREEN;

default:next_state=RED;

endcase

end

//led

always@(*)

case(state)

RED:{red,yellow,green}=3'b100;

YELLOW:{red,yellow,green}=3'b010;

GREEN:{red,yellow,green}=3'b001;

default:{red,yellow,green}=3'b000;

endcase

//clock

always@(posedge clk,negedge rst_n)

if(~rst_n)

clock<=10; //red

else

case(state)

RED:if(clock==1)

clock<=60;

else

clock<=clock-1;

YELLOW:if(clock==1)

clock<=10;

else

clock<=clock-1;

GREEN:

if(pass_request)

if(clock>10)

clock<=10;

else

clock<=clock-1;

else if(clock==1)

clock<=5;

else

clock<=clock-1;

default:clock<=10;

endcase

endmodule

测试平台

module test;

reg clk;

reg rst_n;

reg pass_request;

wire [7:0] clock;

wire red;

wire yellow;

wire green;

//clk

initial

begin

clk=0;

forever

#5 clk=~clk;

end

//rst_n

initial

begin

rst_n=0;

#100

rst_n=1;

end

//

initial

begin

pass_request=0;

//

repeat(20)

@(posedge clk);

wait(green&&clock==18);

pass_request<=1;

@(posedge clk);

pass_request<=0;

//

repeat(40)

@(posedge clk);

wait(green&&clock==9);

pass_request<=1;

@(posedge clk)

pass_request<=0;

end

//inst

triffic_light U

(.*

/*

input rst_n, //异位复位信号,低电平有效

input clk, //时钟信号

input pass_request,

output reg [7:0]clock,

output reg red,

output reg yellow,

output reg green

*/

);

endmodule

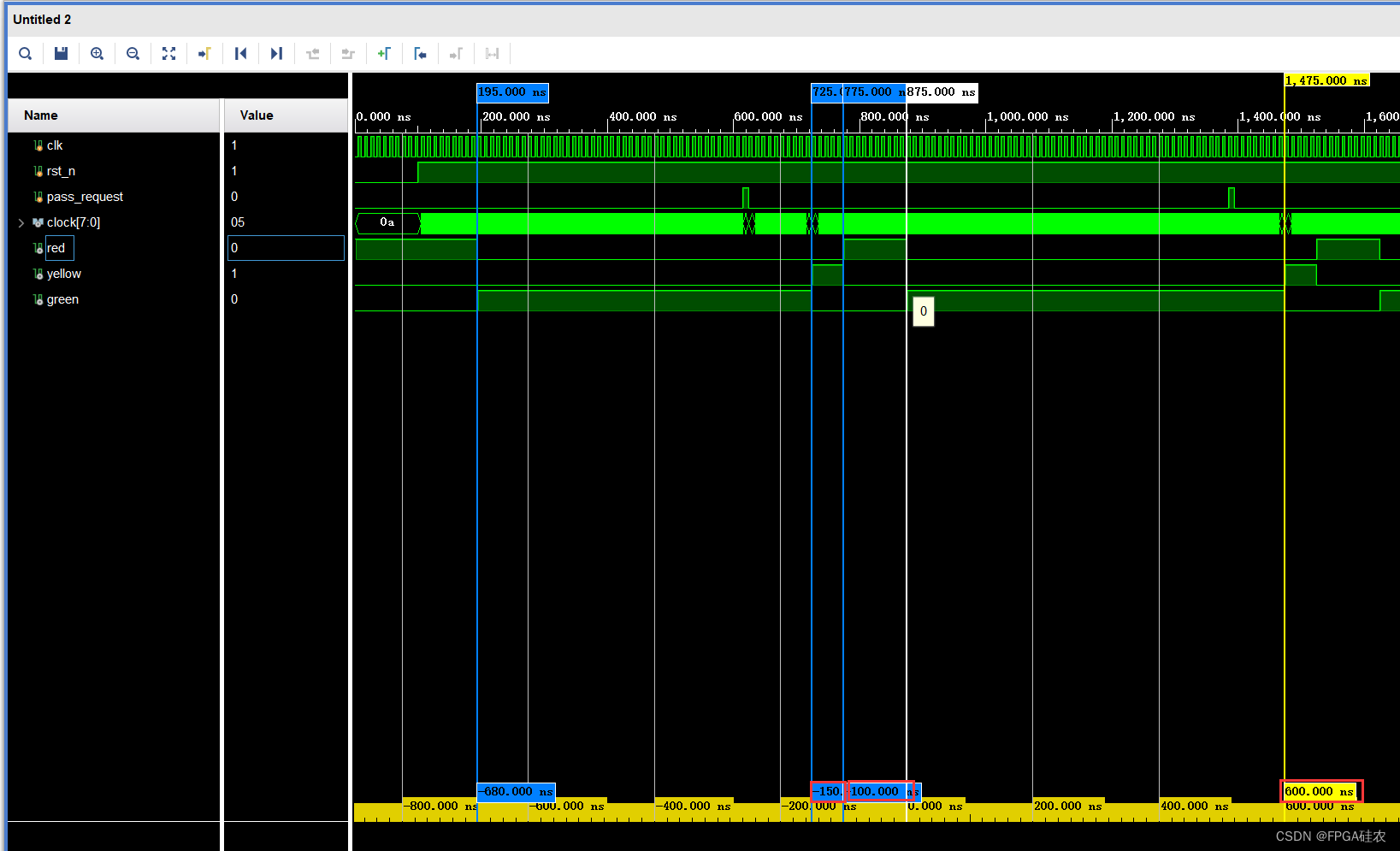

结果

正常情况下,绿灯60个周期,黄灯5个周期,红灯10个周期

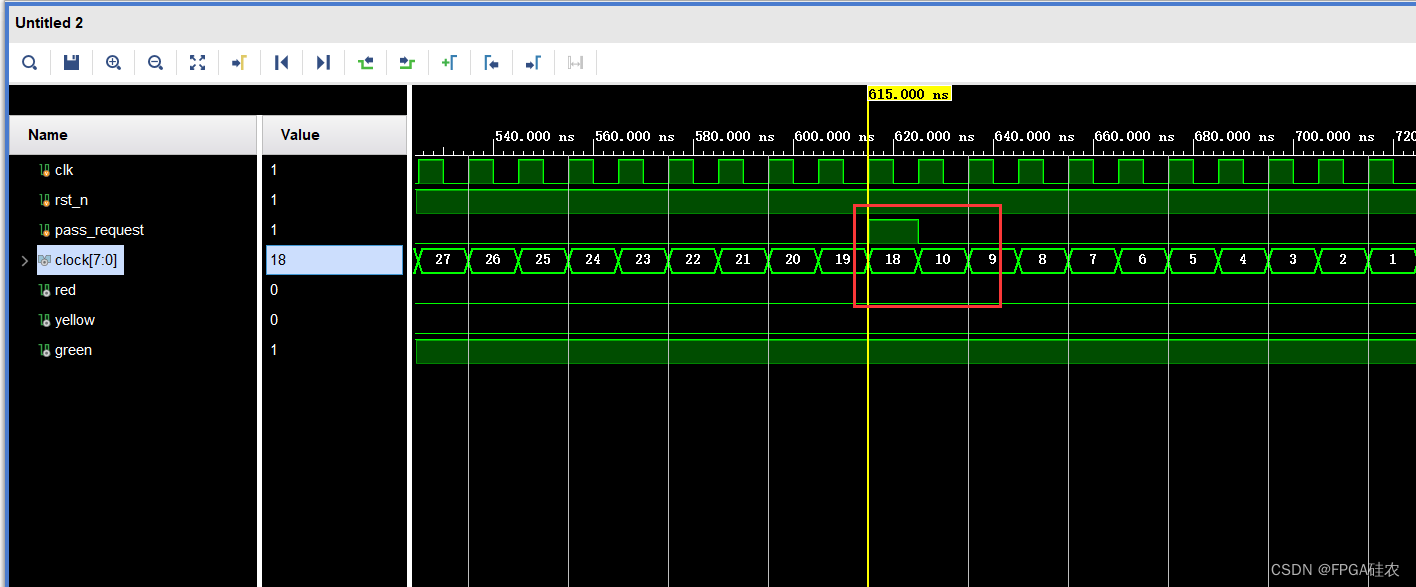

绿灯且大于10个周期的时候,行人按下

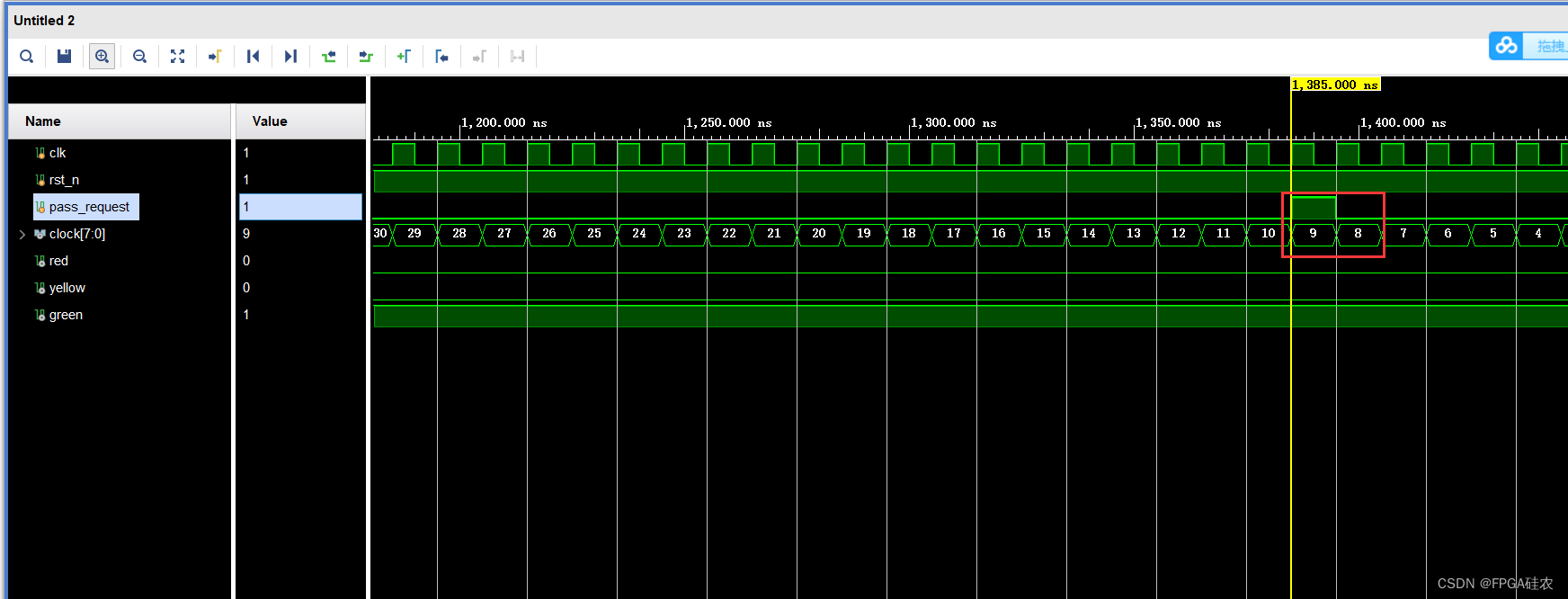

绿灯且小于等于10个周期的时候,行人按下

本文介绍如何使用Verilog HDL语言设计一款交通信号灯模块,包含红绿黄指示灯及行人按钮控制。在正常情况下遵循60绿5黄10红的周期,行人按钮在绿灯小于10个周期时会调整时长。通过testbench进行了功能验证。

本文介绍如何使用Verilog HDL语言设计一款交通信号灯模块,包含红绿黄指示灯及行人按钮控制。在正常情况下遵循60绿5黄10红的周期,行人按钮在绿灯小于10个周期时会调整时长。通过testbench进行了功能验证。

1668

1668

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?