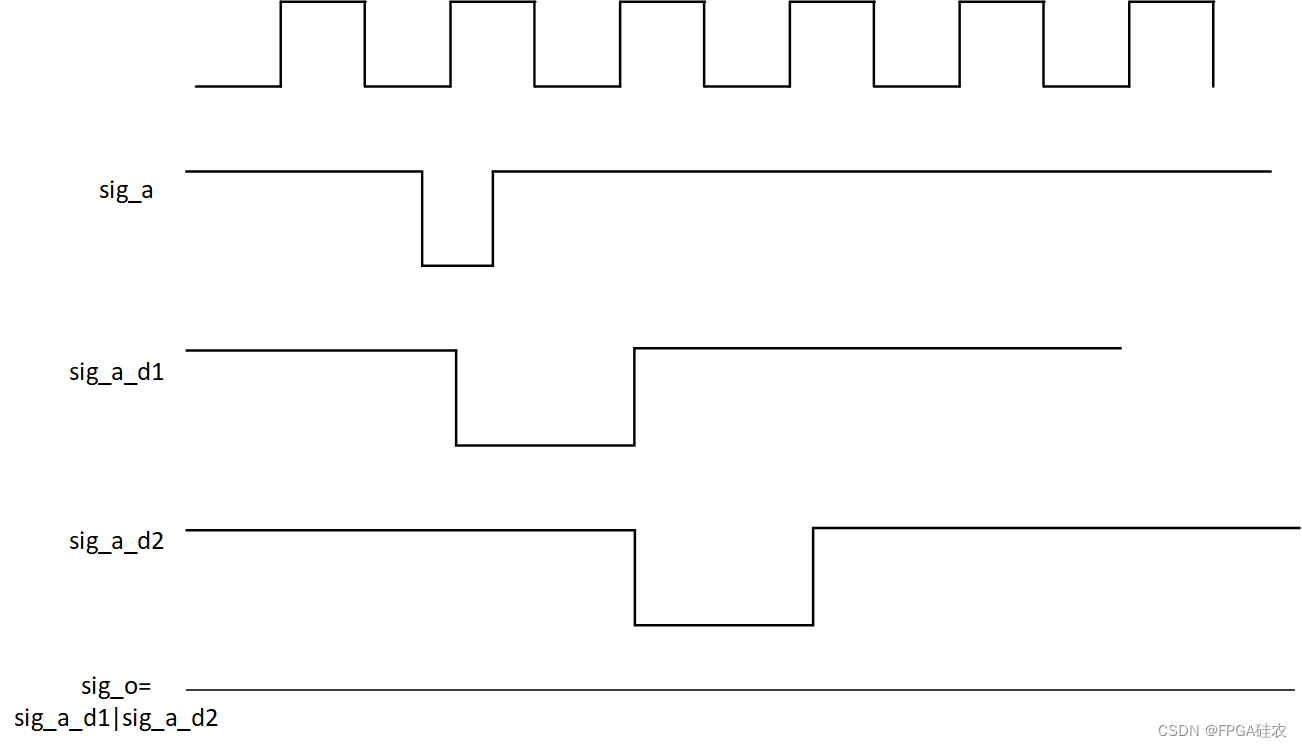

小于一个时钟周期的低电平毛刺的消除,可采用两级触发器打拍+或门的方式解决,如下图所示:

代码:

always@(posedge clk,posedge rst)

if(rst)

{sig_d2,sig_d1}<=2'b11;

else

{sig_d2,sig_d1}<={sig_d1,sig};

//

assign sig_o=sig_d1|sig_d2;

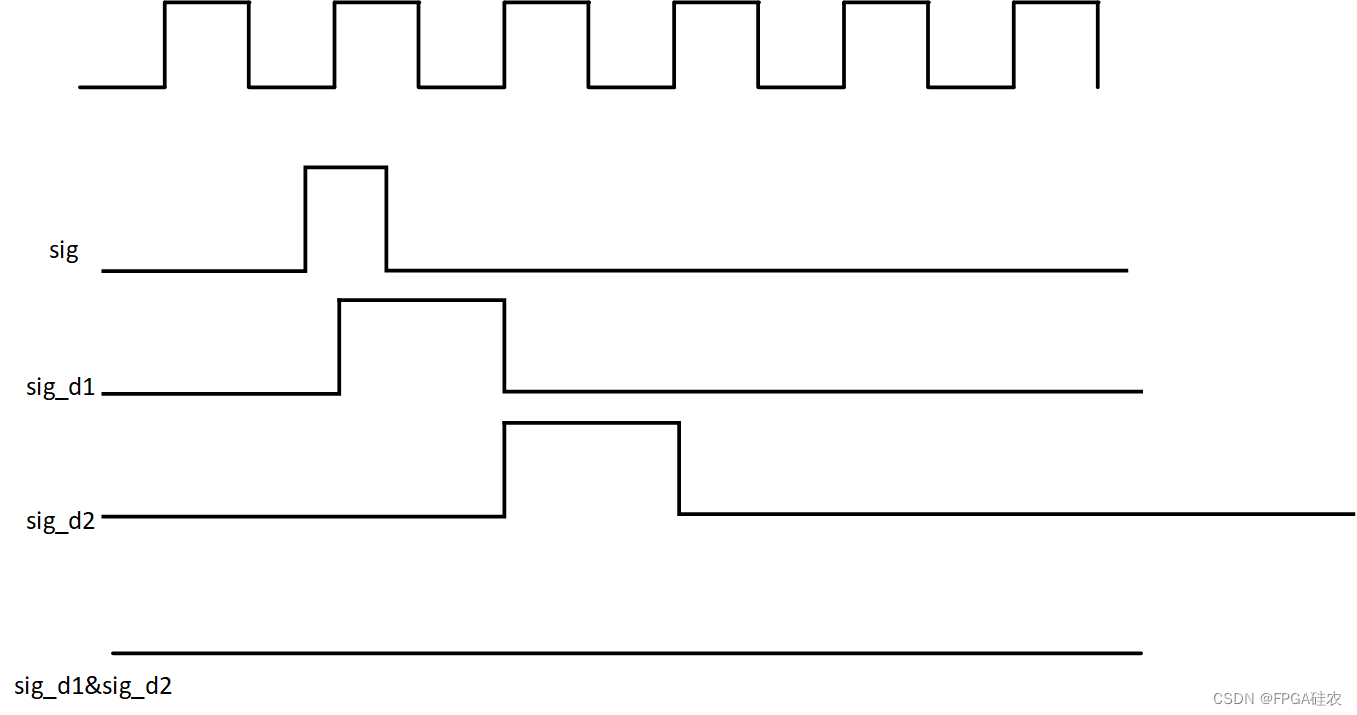

高电平有效的毛刺的去除:

如上图所示,对于小于1个周期的高电平毛刺,可以采用打两拍+与门的方式实现,代码如下

always@(posedge clk,posedge rst)

if(rst)

{sig_d2,sig_d1}<=0;

else

{sig_d2,sig_d1}<={sig_d1,sig};

//

assign sig_o=sig_d2&sig_d1;

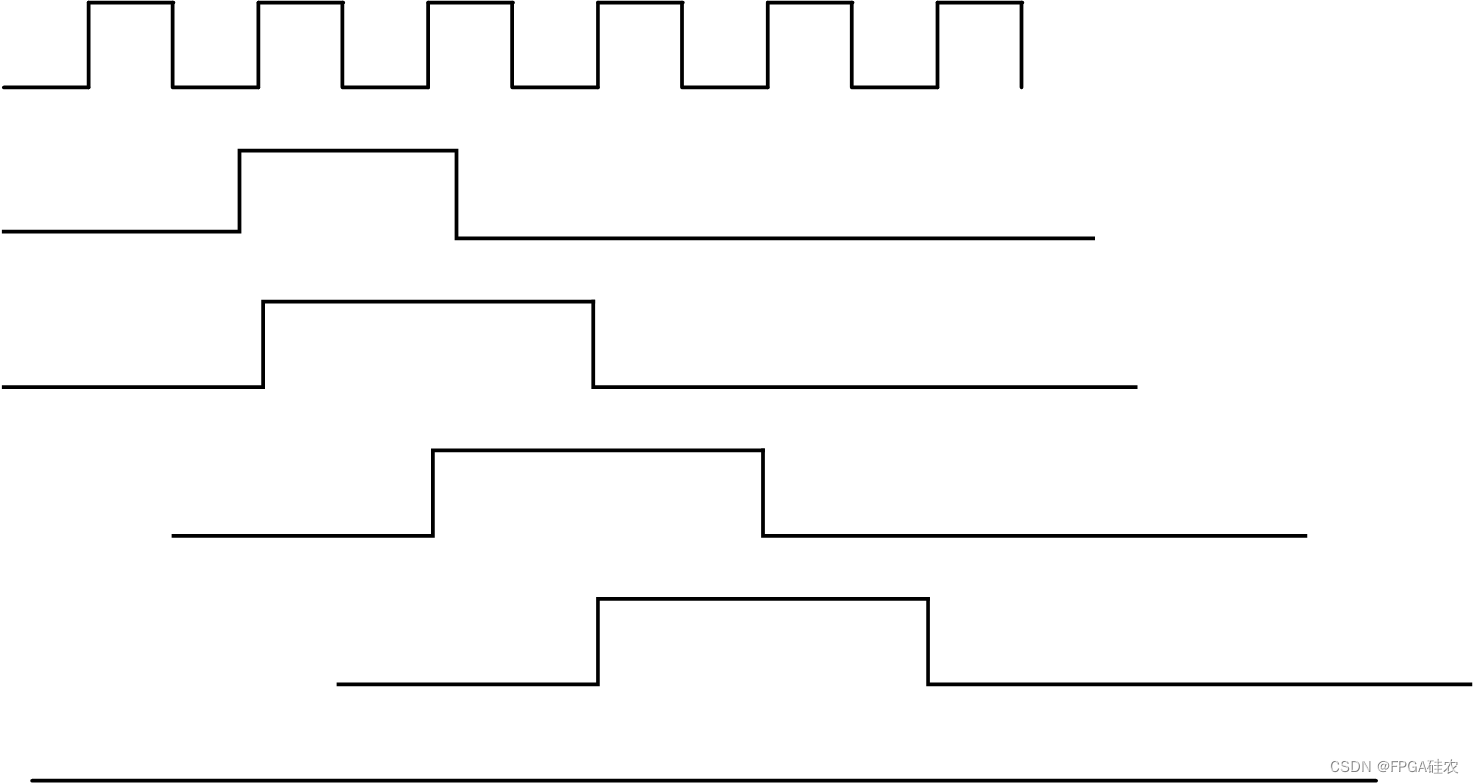

当毛刺宽度大于一个周期小于两个周期时,可采用打三拍+与门的方式实现:

如上图所示,当毛刺宽度大于一个周期小于2个周期时,打两拍+与门无法滤除,需要打三拍才行。

代码

reg [2:0] sig_ff;

always@(posedge clk,posedge rst)

if(rst)

sig_ff<=0;

else

sig_ff<={sig_ff[1:0],sig};

//

assign sig_o = &sig_ff;

总结

- 当需要消除高电平的毛刺时,采用与门,当需要消除低电平的毛刺时,采用或门。

- 若毛刺宽度介于N和N+1个周期,则需要N+2级触发器采样,然后再进行与(或)。

2736

2736

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?