前提:

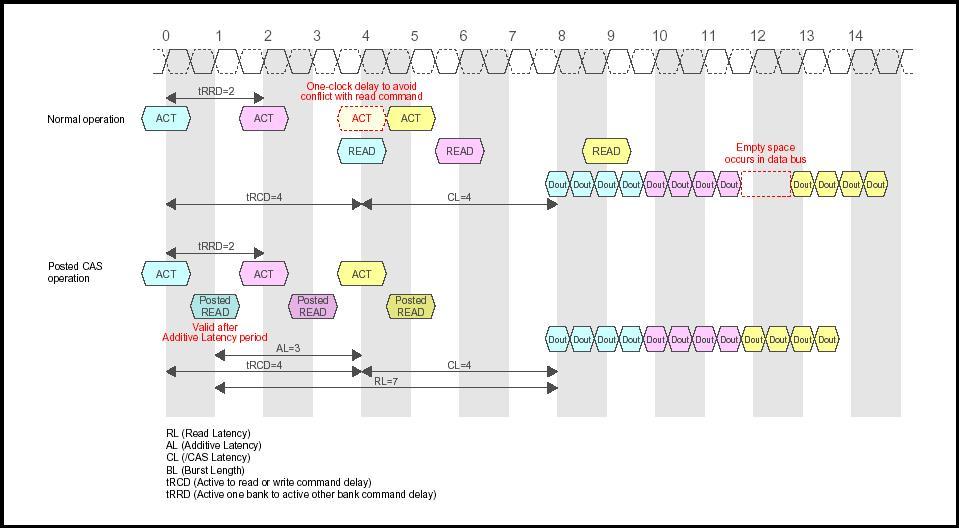

要求①、相邻两个ACT指令间隔两个时钟周期。

要求②、RL、AL、CL、BL、tRCD、tRRD这些时间参数都是固定的值

一、常规情况,

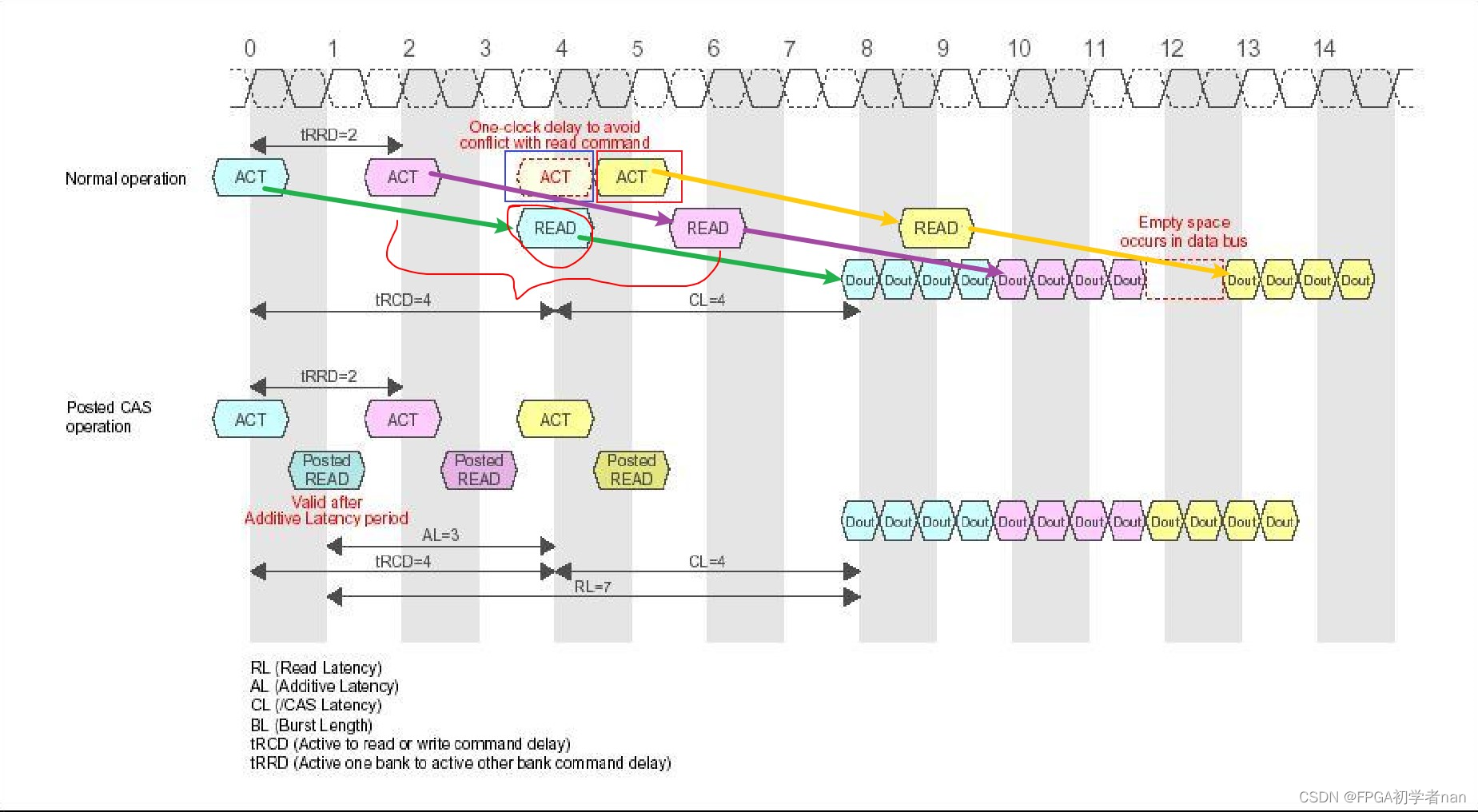

1、两端绿色箭头的意思(紫色、橙色同理):

在ACTIVE指令(行有效)后,需要等待一段时间(tRCD),才能继续发送READ指令(列有效)。而在READ命令发出后,读出的数据要经过一段时间(CL),才能出现在输出端。

2、冲突产生的例子

按照要求①,黄色ACT应该处于图中虚线位置。

按照要求②,蓝色ACT和蓝色READ之间,有个 tRCD=4 的延迟,所以蓝色READ应该出现在图中所示位置。粉色ACT和粉色READ之间,也有个 tRCD=4 的延迟。而在两个粉色命令之间,会发现黄色ACT命令和蓝色READ命令冲突!

3、解决冲突的办法

把原本应该出现在虚线位置的橙色ACT命令延后一个时钟周期,让它和蓝色READ命令避开。

4、冲突产生的后果

当橙色ACT命令延迟一个时钟周期后,读出的数据也延迟一个时钟周期。而粉色的ACT命令没有变化,它还是在原来的时刻读出数据。这么一来导致数据总线出现了一个时钟周期的空缺。

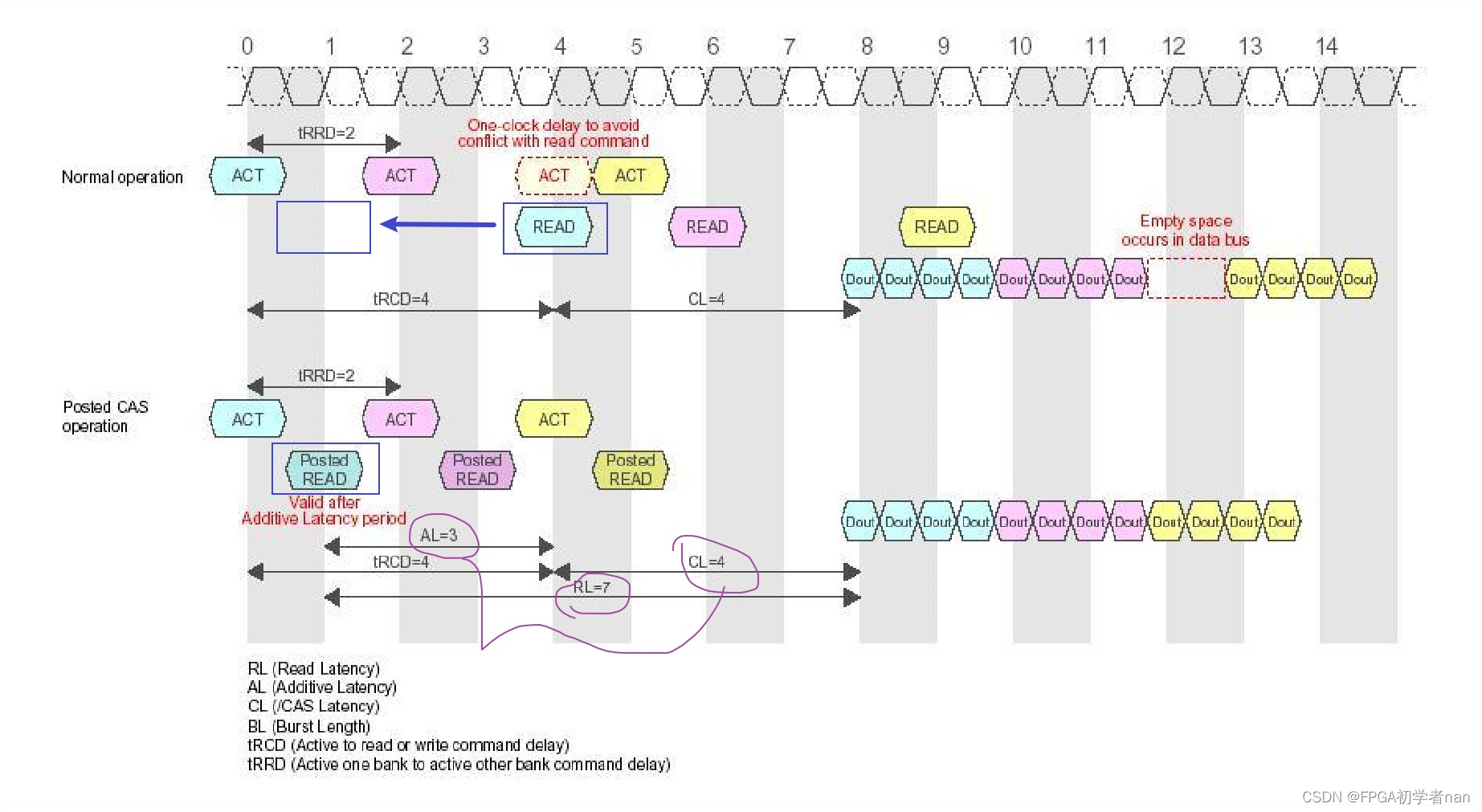

仔细分析冲突产生的原因

发现是 常规情况下,ACT和READ之间有时间间隔,即行激活和列激活(CAS)之间有延迟(tRCD),容易让其他指令闯进来。

本质的解决办法:让前置列激活(Posted CAS)。例如图中把READ都前置到紧邻ACT的位置。

这样做有两个好处:

①、让每个时钟上升沿都有对应的指令执行,而不会像常规的情况下,上升沿1、3、5 指令是空闲的。效率更高了。

②、不会让数据传输产生间隔。

从上图,可以看出,

AL本质上是指:列激活比常规情况的列激活提前了多少周期。

CL仍然指:常规情况下,读指令发出后到输出端产生信号的延时。

RL(AL+CL)指的是:前置CAS的情况下,读指令发出后到输出端产生信号的延时。

文章讨论了内存控制器如何处理ACT和READ指令之间的延迟(tRCD),以及冲突的解决办法。通过引入前置CAS,可以提高效率,消除数据传输间隔。AL表示列激活的提前量,CL保持为读指令到输出的延迟,RL是前置CAS情况下读指令后的延迟时间。

文章讨论了内存控制器如何处理ACT和READ指令之间的延迟(tRCD),以及冲突的解决办法。通过引入前置CAS,可以提高效率,消除数据传输间隔。AL表示列激活的提前量,CL保持为读指令到输出的延迟,RL是前置CAS情况下读指令后的延迟时间。

7464

7464

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?