AMBA:vip_exeplem:/share/tools/eda1/synopsys/vip-2021.09/vip/svt/amba_svt/latest

doc:/share/tools/eda1/synopsys/vip-2021.09/vip/svt/amba_svt/latest/doc/class_ref/axi_svt_uvm_class_reference/html:执行firefox index.html

example:/share/tools/eda1/synopsys/vip-2021.09/vip/svt/amba_svt/latest/examples/sverilog/

pcie vip:/share/ip/corsica/synopsys/DW_HOME/iip/DWC_pcie_ctl/latest/doc

1、env:

svt_apb_system_env apb_sys_env;

svt_axi_system_env pci_sys_env;

svt_apb_system_configuration apb_cfg;

svt_axi_system_configuration pci_ace_cfg;

在build phase里面创建(create):apb_cfg;并对相关变量赋值:

apb_cfg.paddr_width = svt_apb_system_configuration::PADDR_WIDTH_13;

apb_cfg.pdata_width = svt_apb_system_configuration::PDATA_WIDTH_32;

/** Master setup */

apb_cfg.create_sub_cfgs(1);

apb_cfg.is_active = 1;

apb_cfg.slave_cfg[0].is_active = 0;

/** Enable UVM APB Ral Adapter */

apb_cfg.uvm_reg_enable = 1;

set给apb_sys_env:uvm_config_db#(svt_apb_system_configuration)::set(this, "apb_sys_env", "cfg", apb_cfg);

再创建apb_sys_env;(get 是vip内部写好的);

pci_sys_env的流程和上面一样,只是axi_cfg需要关注的配置参数不同也相对多一点;

需要关注的axi_cfg参数:

pci_ace_cfg.create_sub_cfgs(0, 1, 0, 0, 0);

//create_sub_cfgs ( int num_masters = 1, int num_slaves = 1, int num_ic_master_ports = 0, int num_ic_slave_ports = 0, int num_lp_masters = 0 )

pci_ace_cfg.num_masters = 0;

pci_ace_cfg.num_slaves = 1;

pci_ace_cfg.common_clock_mode = 0;(这个为0时外面连接给vip_if的clk和复位才会起效果,在AXI stream那个模块感觉就是这个原因导致激励一直没有发出去,没有时钟和复位)

//This parameter(common_clock_mode) indicates whether a common clock should be used for all the components in the system or not.

// When set, a common clock supplied to the top level interface is used for all the masters, slaves and interconnect in the system.

pci_ace_cfg.slave_cfg[0].is_active = 1;

pci_ace_cfg.slave_cfg[0].axi_interface_type = svt_axi_port_configuration::ACE_LITE;

pci_ace_cfg.slave_cfg[0].protocol_checks_enable = 1;

pci_ace_cfg.slave_cfg[0].addr_width = 64;

pci_ace_cfg.slave_cfg[0].data_width = 512;

pci_ace_cfg.slave_cfg[0].addr_user_width = 58;//命令通道user的位宽

pci_ace_cfg.slave_cfg[0].data_user_width = 58;//数据通道user的位宽

pci_ace_cfg.slave_cfg[0].resp_user_width = 58;//resp通道user的位宽

pci_ace_cfg.slave_cfg[0].single_outstanding_per_id_enable = 1;//路径上的id是否要唯一,会有check

pci_ace_cfg.slave_cfg[0].exclusive_access_enable = 1;//独占访问:

pci_ace_cfg.slave_cfg[0].default_arready = 0;//设置axi的信号默认值,类似的还有awready等;

pci_ace_cfg.slave_cfg[0].id_width = 17;//是指awid/arid/bid等的宽度

//set_addr_range(slave id,地址min,地址max)

pci_ace_cfg.set_addr_range(0, 64'h0, 64'hffff_ffff_ffff_ffff);//设置接口上的地址范围,会有check

pci_ace_cfg.slave_cfg[0].aruser_enable = 1;//使能aruser,类似的还有:awuser_enable,buser_enable等

乱序和outstanding的设置//需要设置vip相关宏,不然默认的可能不支持///

pci_ace_cfg.slave_cfg[0].reordering_algorithm = svt_axi_port_configuration::ROUND_ROBIN;//PRIORITIZED/RANDOM

pci_ace_cfg.slave_cfg[0].write_resp_reordering_depth = `SVT_AXI_MAX_WRITE_RESP_REORDERING_DEPTH

pci_ace_cfg.slave_cfg[0].num_outstanding_xact = `SVT_AXI_MAX_NUM_OUTSTANDING_XACT;

pci_ace_cfg.slave_cfg[0].num_read_outstanding_xact = `SVT_AXI_MAX_NUM_OUTSTANDING_XACT;

pci_ace_cfg.slave_cfg[0].num_write_outstanding_xact = `SVT_AXI_MAX_NUM_OUTSTANDING_XACT;

关闭vip的一些打印:这个是利用uvm的机制,uvm_object可以控制内部成员的打印级别:

todo

2、vip用到的一些宏(define.v):

`define SVT_APB_MAX_ADDR_WIDTH 32

`define SVT_APB_MAX_DATA_WIDTH 32

`define SVT_AXI_MAX_NUM_SLAVES_1

`define SVT_AXI_MAX_NUM_MASTERS_1

`define SVT_AXI_MAX_LP_MASTERS_1

`define SVT_APB_MAX_NUM_MATERS_1

`define SVT_APB_MAX_NUM_SLAVES_1

`define SVT_AXI_MAX_DATA_WIDTH 512

`define SVT_AXI_MAX_ID_WIDTH 17

`define SVT_APB_DISCONNECT_TOP_LEVEL_APB_IF_SIGNALS //为什么要用到这个?

`define SVT_AXI_MAX_ADDR_USER_WIDTH 24

`define SVT_AXI_MAX_DATA_USER_WIDTH 24

`define SVT_AXI_MAX_BRESP_USER_WIDTH 24

//wells//for outstanding

`define SVT_AXI_MAX_READ_DATA_REORDERING_DEPTH 256

`define SVT_AXI_MAX_NUM_OUTSTANDING_XACT 256

`define SVT_AXI_MAX_WRITE_RESP_REORDERING_DEPTH 256

//为了构造各种长延时和长反压需要给大点,不然会约束冲突;

`define SVT_AXI_MAX_WRITE_RESP_DELAY 15000

`define SVT_AXI_MAX_RVALID_DELAY 15000

`define SVT_AXI_MAX_WREADY_DELAY 15000

`define SVT_AXI_MAX_ADDR_DELAY 20000

`define SVT_AXI_MAX_IDLE_WREADY_DELAY_ARR_SIZE 2000

3、mem模型:是直接用svt_mem声明的;(主要是构建req_bd_ring)

然后外面包一个write/read函数,里面其实是调用vip的svt_mem的write/read函数(后门方式);(这两个函数有一个对齐要求;);

在这个类里面有针对mem byte级别读写的函数:

提供了write_byte() 和read_byte() 两个按字节地址实现后门读写的方法,原型如下:

task write_byte(input bit[`SVT_AXI_MAX_ADDR_WIDTH-1:0] addr, bit[7:0] data);

task read_byte(input bit[`SVT_AXI_MAX_ADDR_WIDTH-1:0] addr, output bit[7:0] data);

设置mem模型未初始化的地址区域的值(通过set_meminit来设置);

4、axi_vip设置不同延时的rsp:构建slv_seq extends svt_axi_slave_base_sequence;

参考vip的example:/share/tools/eda1/synopsys/vip-2021.09/vip/svt/amba_svt/latest/examples/sverilog/tb_axi_svt_uvm_basic_active_passive_sys/env

里面都有一些典型场景,参考着来即可;

在构建的slave seq里面随机transaction的成员变量即可实现相应的功能;

在tc的build phase指定一下要启动的seq:uvm_config_db#(uvm_object_wrapper)::set(this, "env.ddr_sys_env.slave*.sequencer.run_phase", "default_sequence",slv_rsp_seq_corner::type_id::get());

其他场景:【新思验证小课堂】【AXI VIP】如何在aw channel之前发送w channel?_哔哩哔哩_bilibili

5、svt_axi_transaction:常用成员变量

physical_data 就是接口的数据形式

data svt_axi_transaction的data是会剔除低位的无效数据

wstrb 也是只保留有效位,低位要是无效会去掉

enable_interleave 控制这个包要不要交织

rvalid_delay[] dut(master)发起读请求命令arready/arvalid(读命令通道)后,slv_vip返回数据(rvalid通道)的延时大小;

wready_delay[] slv_vip收到wvalid后延时多久返回wready=1给DUT(master)

addr_ready_delay 是指dut(master)发起arrvalid后延时多长时间后slv_vip拉起arready;(awrvalid和awready也是用这个参数)

addr_valid_delay vip_agt是master才会使用:

bready_delay Applicable for ACTIVE MASTER only. 就是slv_dut发了bvalid后,master_agt这边多久回bready;

bvalid_delay Applicable for ACTIVE SLAVE only. 在变量reference_event_for_bvalid_delay指定事件触发开始计时,计到后,active_slv_agt才会返回bready信号给master_dut;

6、svt_axi_port_configuration:控制agent方面的cfg类

read_addr_chan_idle_val :当vld=0时,伴随信息的控制;所以后面检索vip时,可以按group去检索;他们已经做好了归类了

read_data_chan_idle_val :和上面类似;

write_resp_chan_idle_val :和上面类似;

(INACTIVE_CHAN_X_VAL,INACTIVE_CHAN_Z_VAL,INACTIVE_CHAN_LOW_VAL,INACTIVE_CHAN_HIGH_VAL:/

INACTIVE_CHAN_RAND_VAL,INACTIVE_CHAN_PREV_VAL(保持hold))

7、顶层的interface设置:

svt_axi_if u_svt_ddr_ace_if();

uvm_config_db #(virtual svt_axi_if)::set(null, "uvm_test_top.env.ddr_sys_env", "vif" ,u_svt_ddr_ace_if);

//驱动源在右边

assign u_svt_ddr_ace_if.slave_if[0].aclk = clk;

assign u_svt_ddr_ace_if.slave_if[0].aresetn = rst_n;

//

assign u_svt_ddr_ace_if.slave_if[0].awakeup = u_ddr_ace_if.awakeup;

//

assign u_svt_ddr_ace_if.slave_if[0].araddr = u_ddr_ace_if.araddr;

assign u_svt_ddr_ace_if.slave_if[0].arbar = 0;

assign u_svt_ddr_ace_if.slave_if[0].arburst = u_ddr_ace_if.arburst;

assign u_svt_ddr_ace_if.slave_if[0].arcache = u_ddr_ace_if.arcache;

8、VIP接口的连接

vip_env声明创建:

svt_apb_system_env apb_sys_env;

svt_axi_system_env axi_sys_env;

端口声明:

uvm_tlm_analysis_fifo #(svt_apb_transaction) apb_mnt_scb_fifo;

uvm_tlm_analysis_fifo #(svt_axi_transaction) axi_mnt_scb_started_fifo;

(build phase里面创建,connect_phase里面连接)

connect_phase:

apb_sys_env.master.monitor.item_observed_port.connect(apb_mnt_scb_fifo.analysis_export);

scb.apb_port.connect(apb_mnt_scb_fifo.blocking_get_export);

axi_sys_env.slave[0].monitor.item_started_port.connect(axi_mnt_scb_started_fifo.analysis_export);

scb.axi_started_port.connect(axi_mnt_scb_started_fifo.blocking_get_export);

master场景跨4k异常需要配置下面这个宏:(后面进一步熟悉一下)(13:8k)

`define SVT_AXI_TRANSACTION_ADDR_RANGE_NUM_LSB_BITS 13

【新思验证小课堂】【VIP】AXI 如何发送超出4K boundary的command?_哔哩哔哩_bilibili

axi握手超时的配置:watchdog timeout

svt_axi_system_configuration

axi VIP master 构造异常情况:

1)如果想发addr和wstrb mismatch 的激励可以参考这个配置:wysiwyg_enable;ignore_wstrb_check_for_xx;

apb接口寄存器模型集成:

参考:vip的example,里面有apb的寄存器模型集成例子;tb_apb_svt_uvm_basic_ral_sys文件夹

在env的build_phase里面例化寄存器模型,并set到vip env下面的master;

注意需要配置这个参数:

FQA(遇到的一些问题)

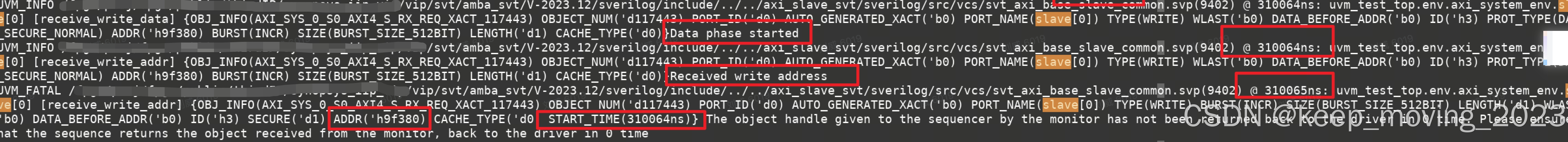

1:AXI VIP slave报错:没有及时返回rsp;

之前遇到过这种问题是:seq那边返回rsp加了延时导致的

这里是:axi_slv_seq是设置在main_phase阶段的,但是axi_agengt的采样组件在run_phase,main_phase结束后,axi接口还有业务导致的; 解决策略:直接把tc的main_phase结束时间加大;

网上其他的一些参考:

新思AXI_VIP - 第2页 - IC验证讨论 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

文章详细介绍了AMBAVIP的配置过程,包括svt_apb_system_env和svt_axi_system_env的创建与配置,如地址和数据宽度、从属配置、时钟模式、用户位宽等参数。还提到了内存模型的设置,VIP接口的连接,以及异常情况的构造。此外,文章涵盖了VIP用到的宏定义和接口的连接方法。

文章详细介绍了AMBAVIP的配置过程,包括svt_apb_system_env和svt_axi_system_env的创建与配置,如地址和数据宽度、从属配置、时钟模式、用户位宽等参数。还提到了内存模型的设置,VIP接口的连接,以及异常情况的构造。此外,文章涵盖了VIP用到的宏定义和接口的连接方法。

2344

2344

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?