1)如何查看波形的毛刺(glitch)

参考:公众号:IC学社

需要添加仿真选项:+fsdb+glitch=0

“值得说明的是,glitch 对 design 是非常不好的,需要规避,设计代码中应该具有检查 glitch 的机制”

2)查看仿真的time_slot过程;

参考:公众号:IC学社

默认情况是没有expand delta;

仿真选项:+fsdb+delta

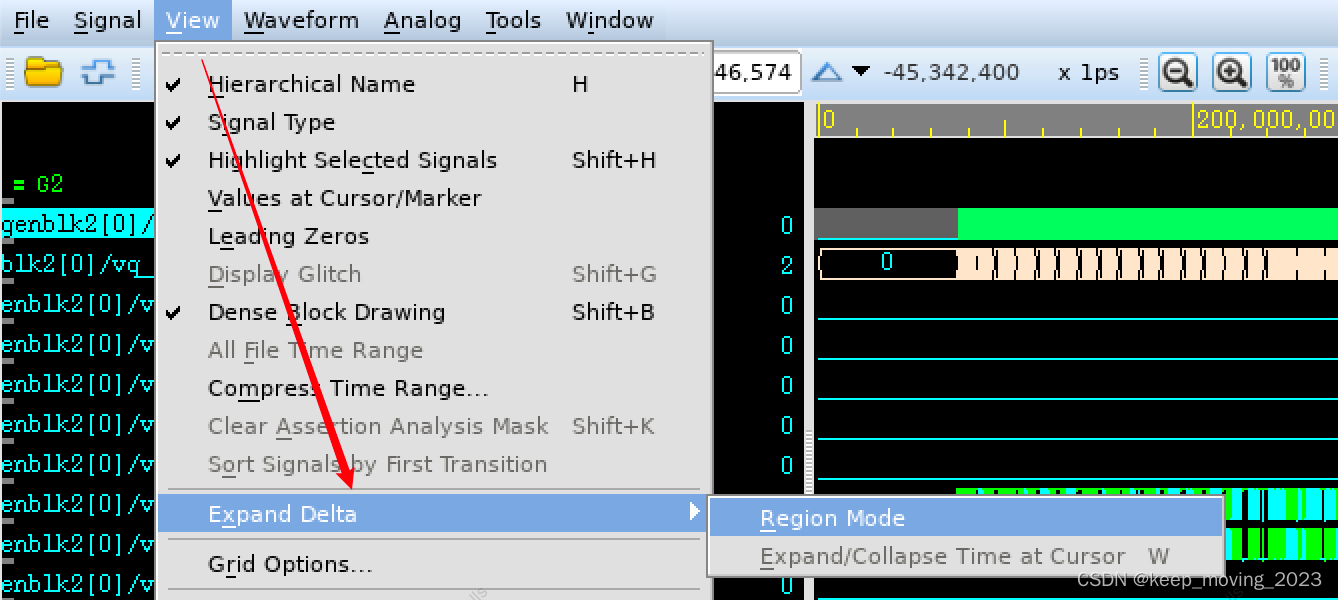

查看方式:

扩展 delta 共有两种选项:

- Region Mode 此选项仅适用于 fsdb 中有 region information 时,Region Mode 会展开 time slot,对每一个 region 中的值的变化显示出来,region 主要有 Active -> NBA -> Re-active -> Re-NBA 等,time slot 中的 region 来自于 SV 的标准 IEEE 1800-2012,更新的标准是 IEEE 1800-2017 和 IEEE 1800-2023。

- Expand/Collapse Time at Course 在光标处展开或者折叠,以显示信号在展开的光标区域的变化,或者展开的 region 内信号的变化。

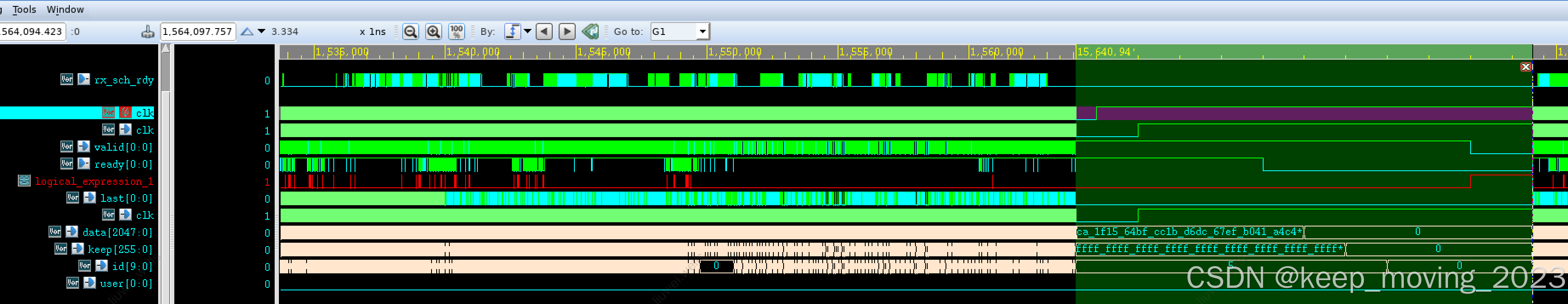

展开看到的效果:在仿真时间片内,硬件的时钟上升沿和TB里面的上升沿在time_slot里面是有先后差异的

查看event_sequence:可以看到一个信号在time_slot的变化过程。

查看event_sequence:可以看到一个信号在time_slot的变化过程。

其中踩过的坑就是,在drv里面用了wait(interface.rdy === 1)这个条件,会把time_slot里面的毛刺抓到(仿真选项加一下:+fsdb+glitch=0;可以直接在波形上看到这个毛刺),导致一些非预期的驱动行为。

网上其他同学的经验参考:IC验证总结_vcs fsdb+delta-CSDN博客

3, vcs仿真效率分析

参考:https://www.cnblogs.com/thisway2014/p/16693466.html

VCS提供了一套对编译时间和仿真时间分析优化的工具,在compile 和simulation option中加入相应的option;

在simulation log path会多出simulation profile log: profileReport.html ;

打开html 分析各方法消耗掉的仿真时间和资源,如constraint solver, function coverage, PLI等;

compile option:

-lca -simprofile mem+timesimulation option:

-simprofile time+mem // 最好只开一个,两者会互相影响

+ntb_solver_debug=profile //对解约束的性能分析参考:vcs simulator profile_vcs profile-CSDN博客

-simprofile [mem/time/noprof]

mem : 仿真过程收集服务器内存消耗状态

time: 仿真过程收集设计和TB内各个模块仿真时间消耗状态。

noprof: 告诉VCS不去收集仿真时间和内存消耗状态。

eg: -simprofile time+mem -simprofile_dir_path xxx

6177

6177

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?