目录

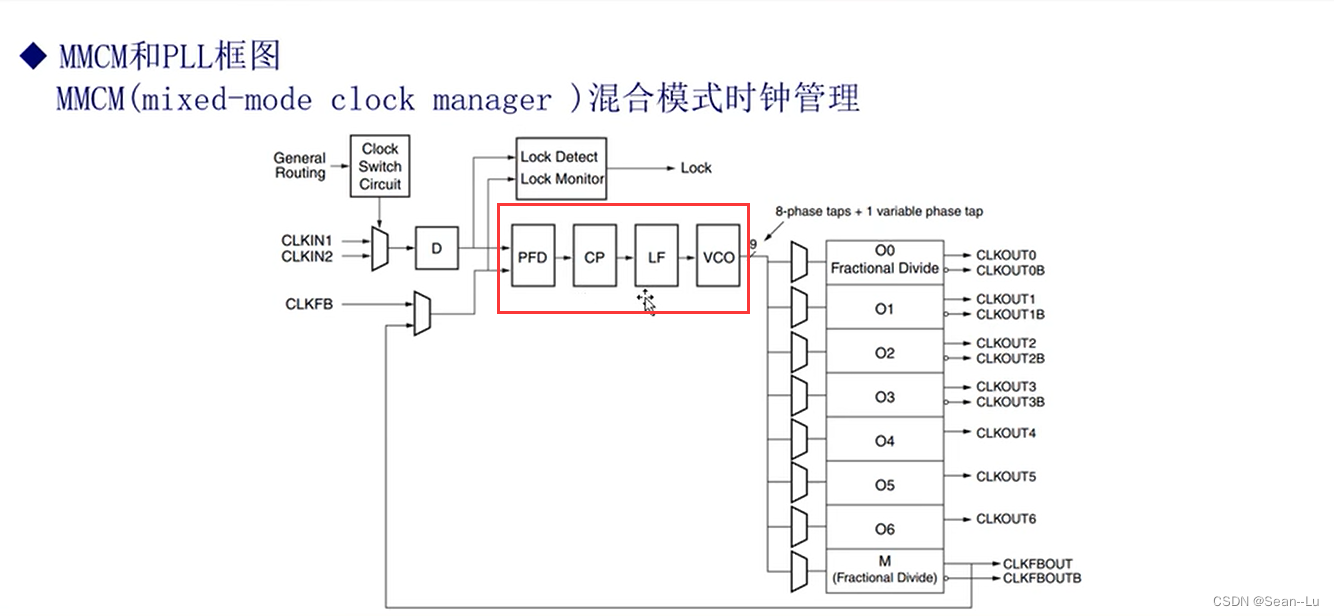

1. 电荷泵锁相环(CPPLL),重要名词:PFD、CP、LF、VCO

2. AXI4-Lite协议、DRP接口——动态调整输出时钟频率的作用

实验要求:

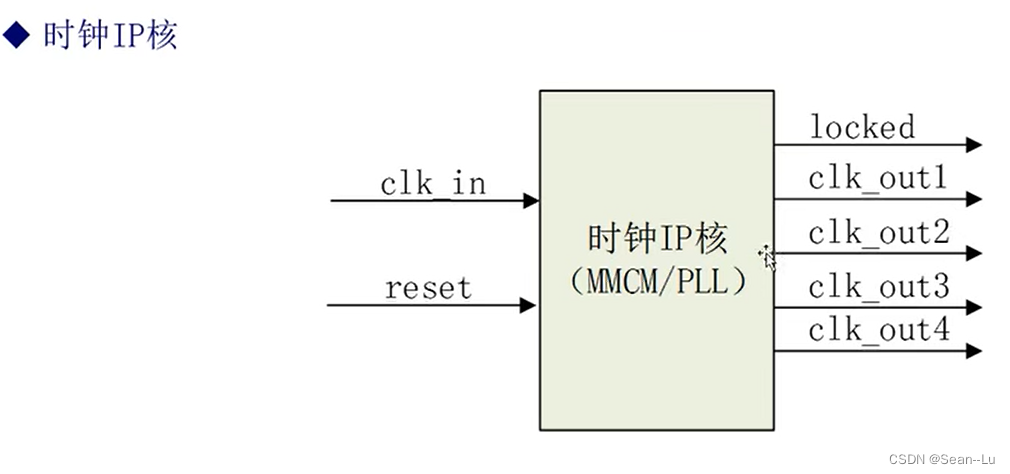

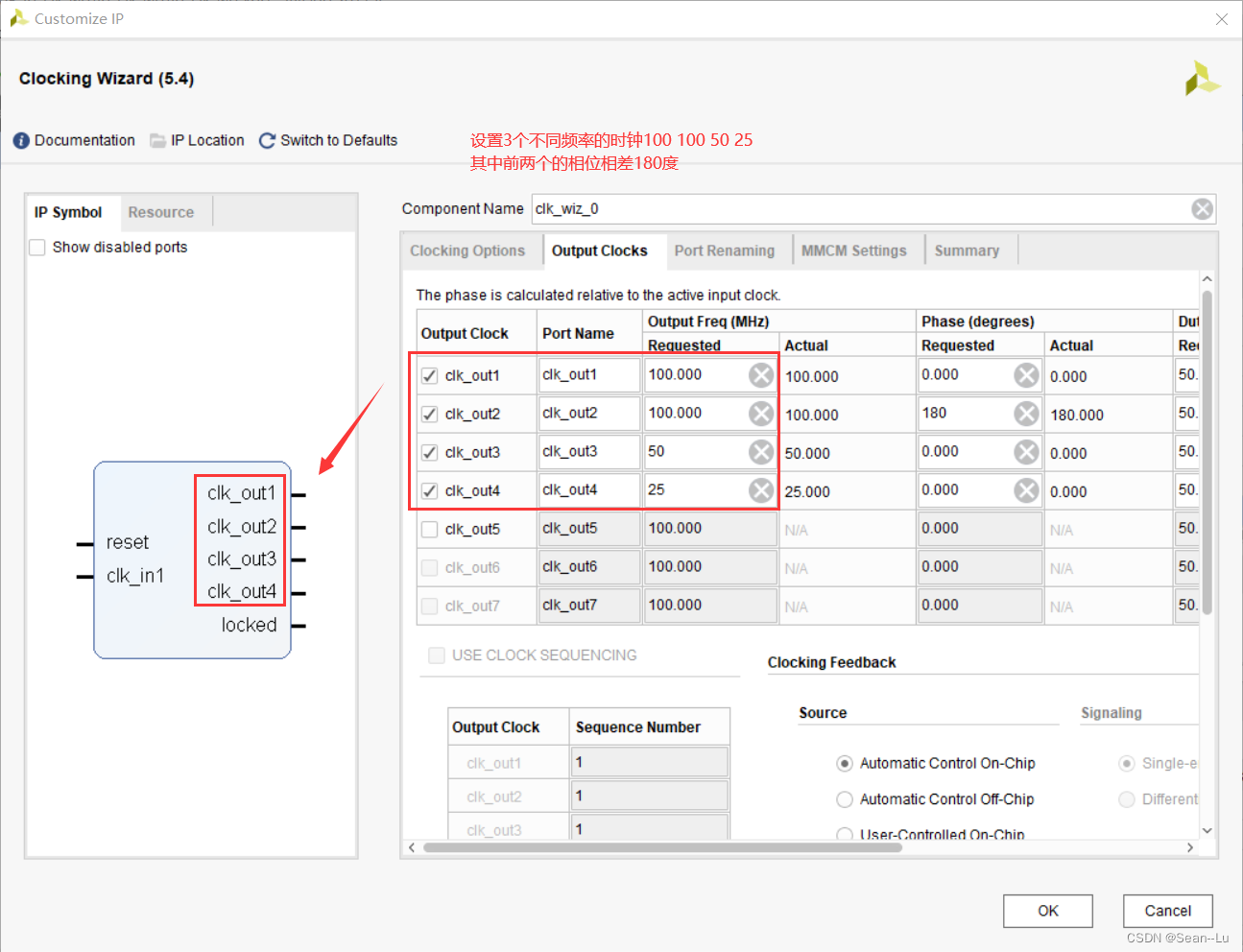

正点原子,利用时钟IP核,得到4个时钟输出:

1. 电荷泵锁相环(CPPLL),重要名词:PFD、CP、LF、VCO

学习文章地址:http://t.csdn.cn/SYGIr

2. AXI4-Lite协议、DRP接口——动态调整输出时钟频率的作用

学习文章地址:http://t.csdn.cn/Ltjqe

学习文章地址:http://t.csdn.cn/GOPOu

动态配置接口DRP(Dynamic Reconfiguration Port),学习文章地址:

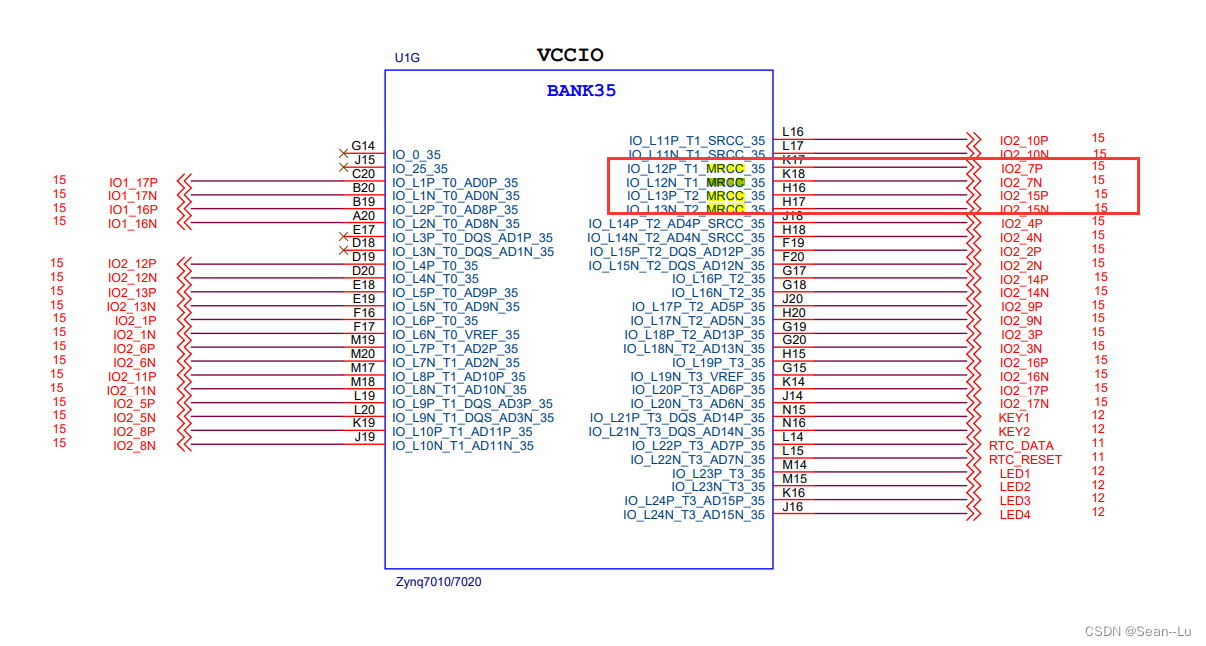

3. 查看时钟输出

1.理论上使用示波器查看输出,但是设备限制。

我们可以使用ILA逻辑分析仪 + 编写testbench文件,进行分析!

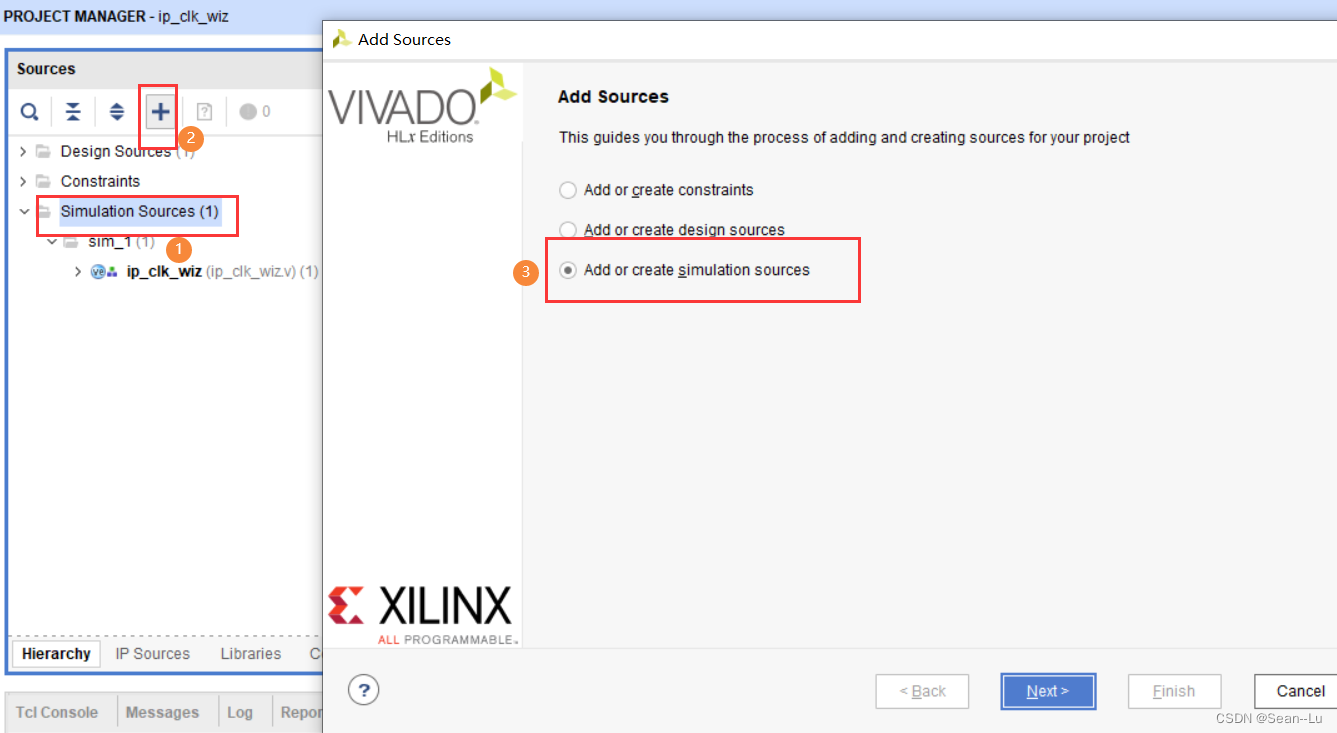

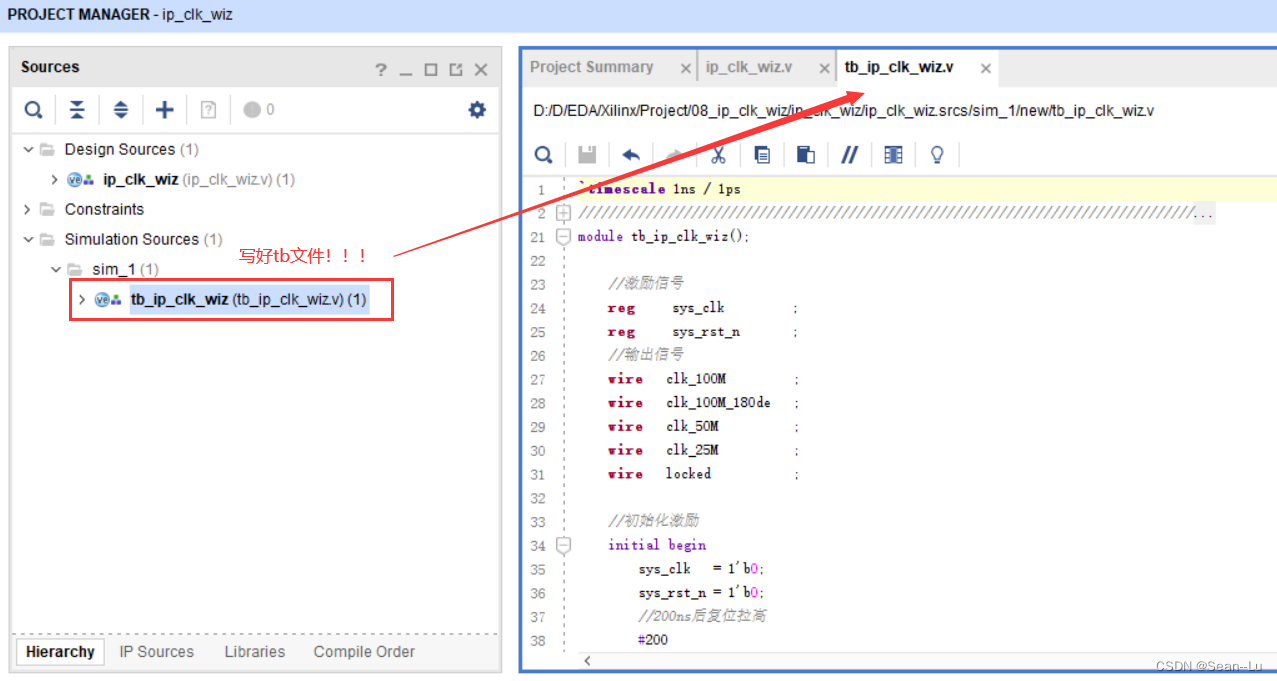

2. 创建tb文件,命名一般tb_文件名

3. 完成仿真文件设置

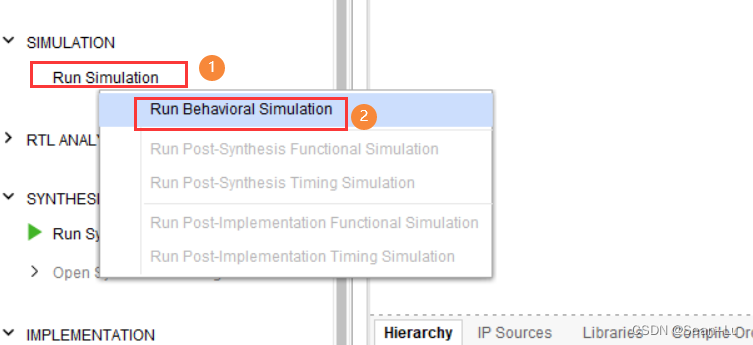

4. 打开仿真

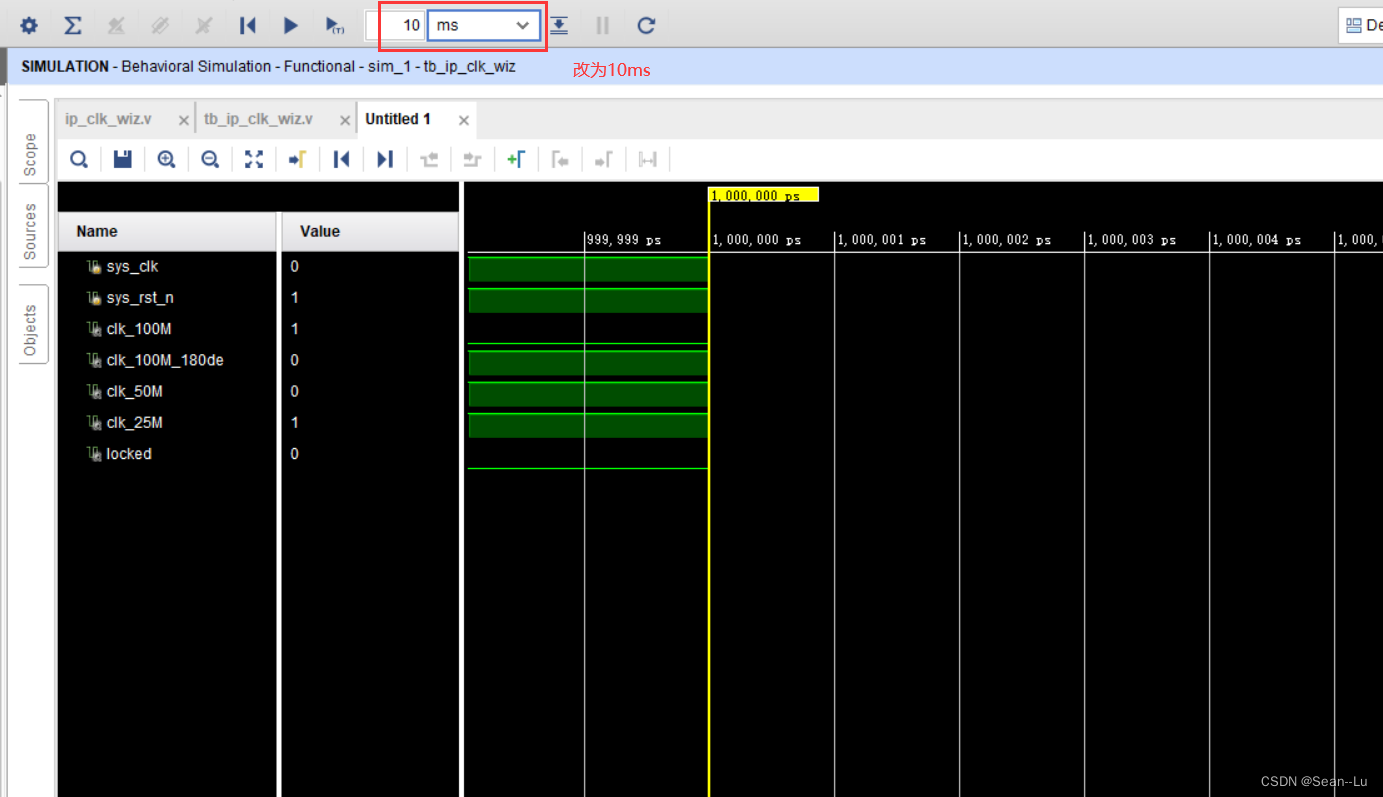

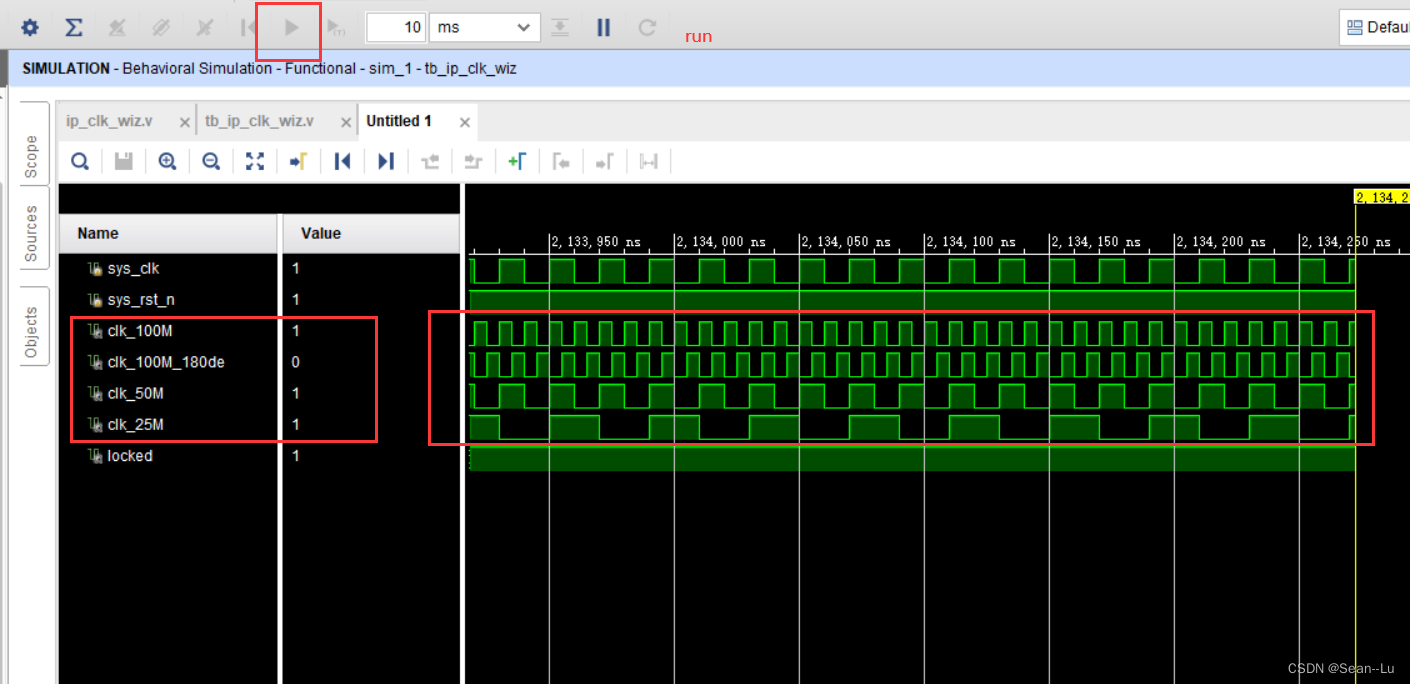

5. 仿真输出

跑仿真,MMCM IP时钟核使用成功!

675

675

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?