目录

2.首先添加整体时钟和复位,然后打开IP Catalog,添加Ram IP核

3. 找到生成的veo文件,复制到.v文件中,例化好,然后写激励文件

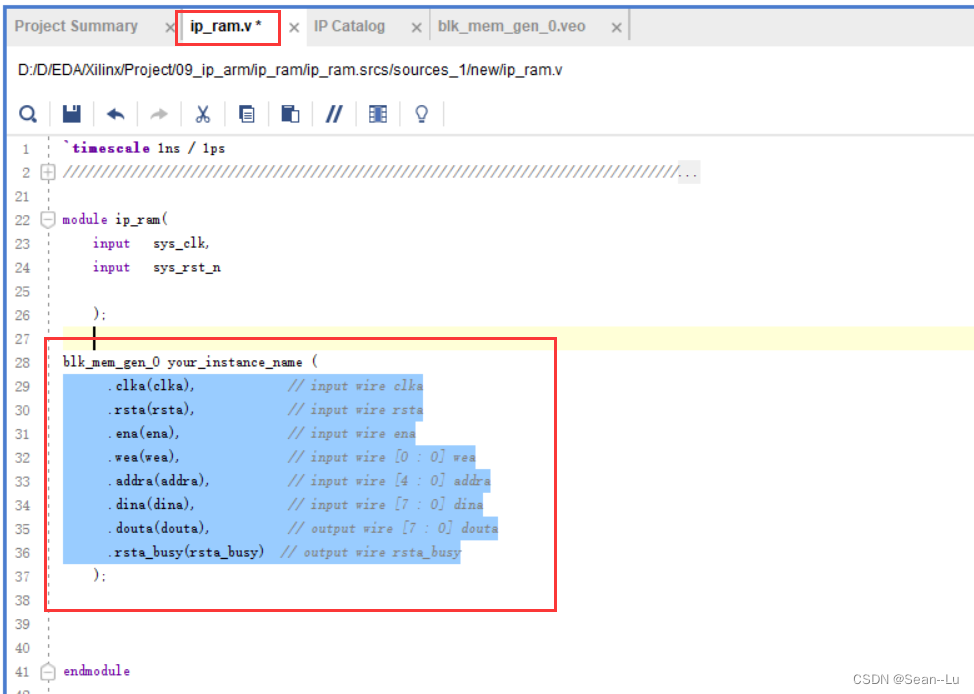

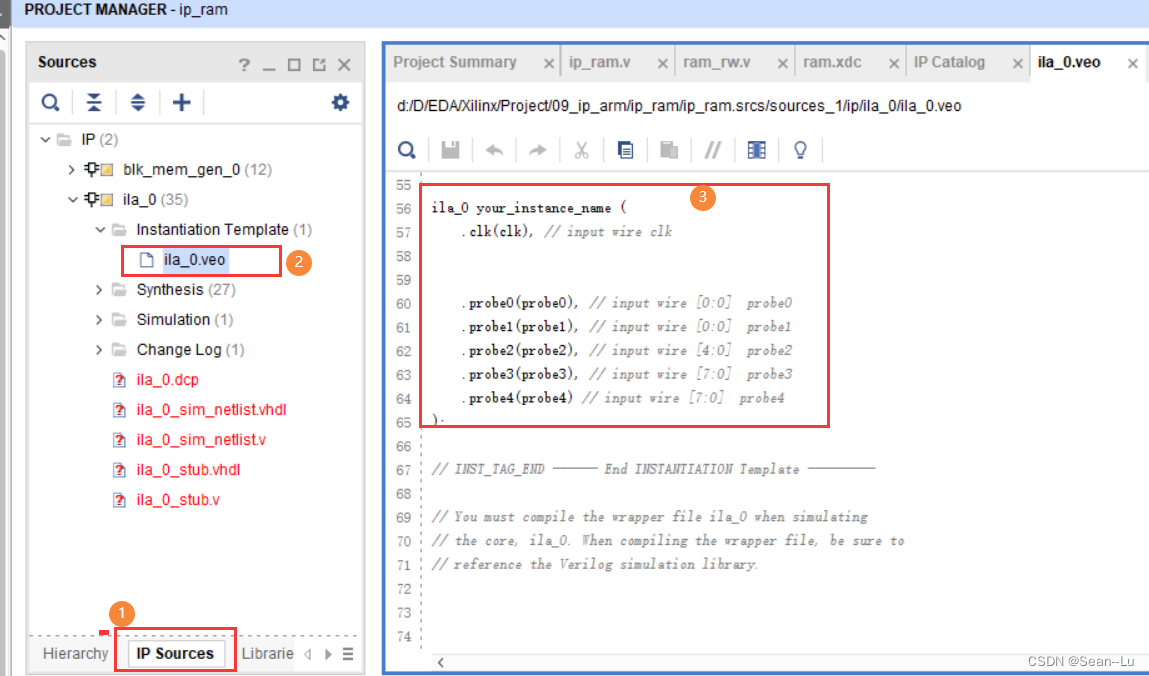

1.复制到.v文件中,例化需要等到激励文件写好后才能输入到这边例化编辑

3.先综合一下,还要做xdc约束,下载bit流到板子,再做ILA逻辑分析

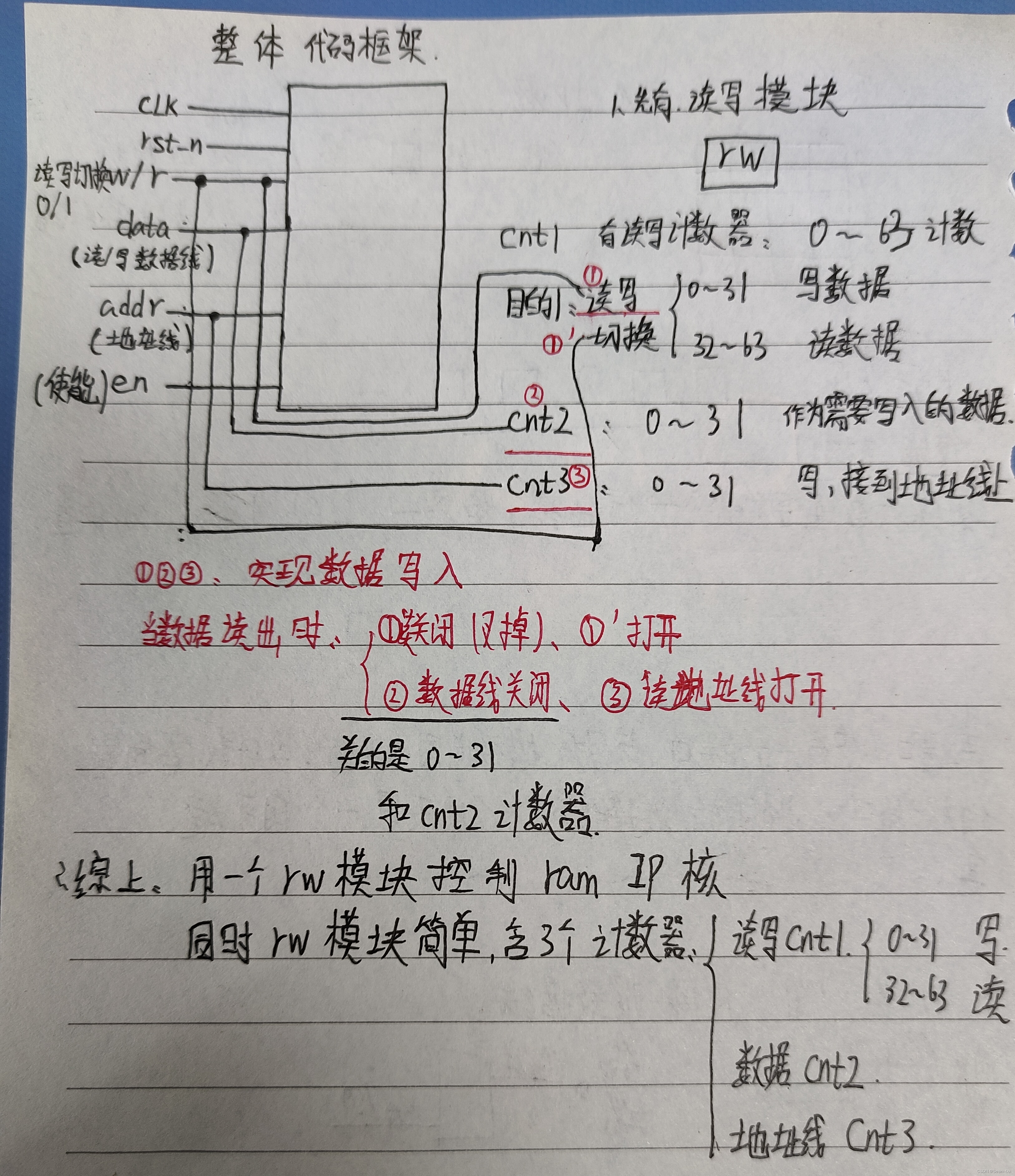

1. 整体代码框架

2.根据整体框架实现

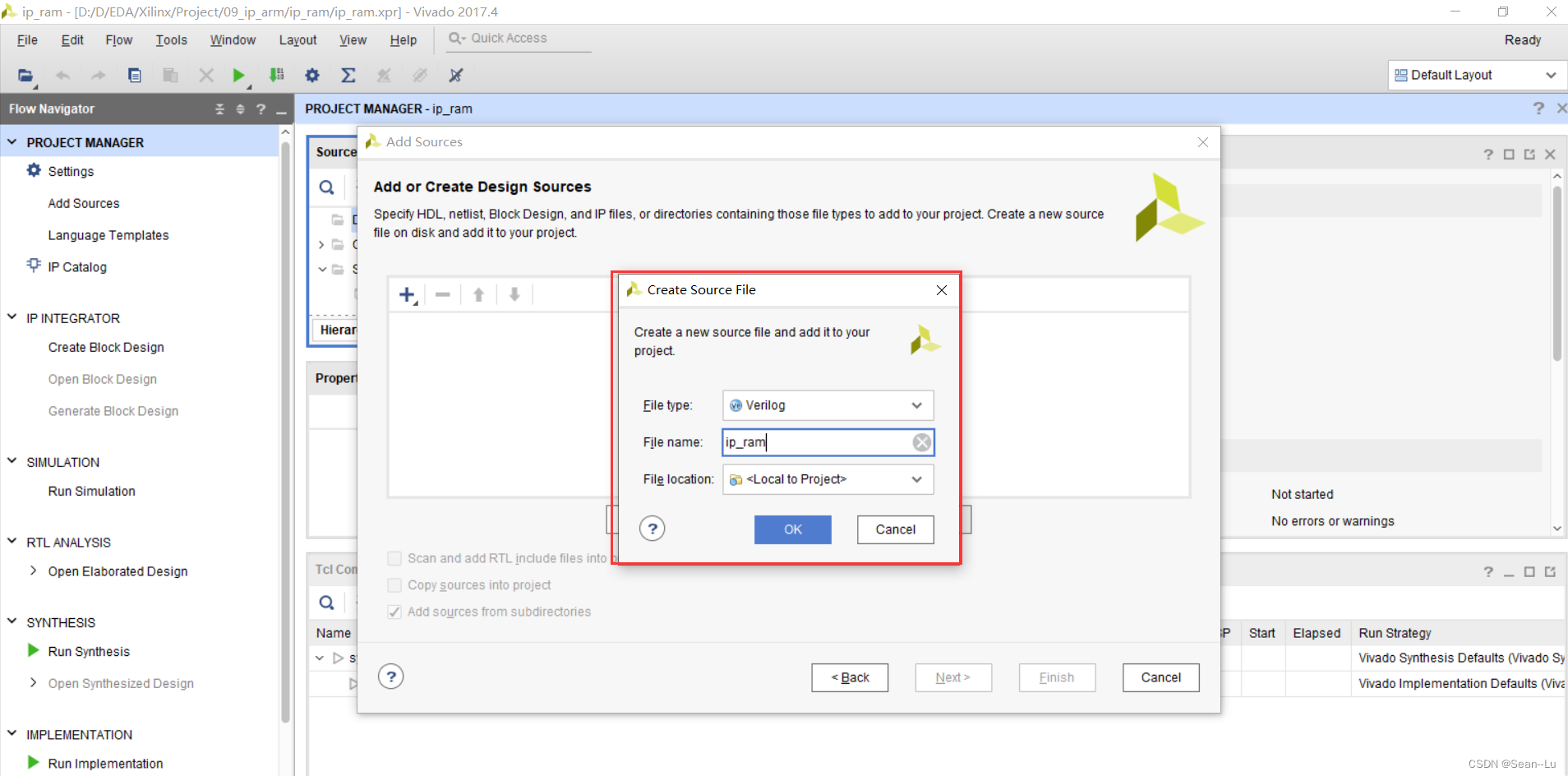

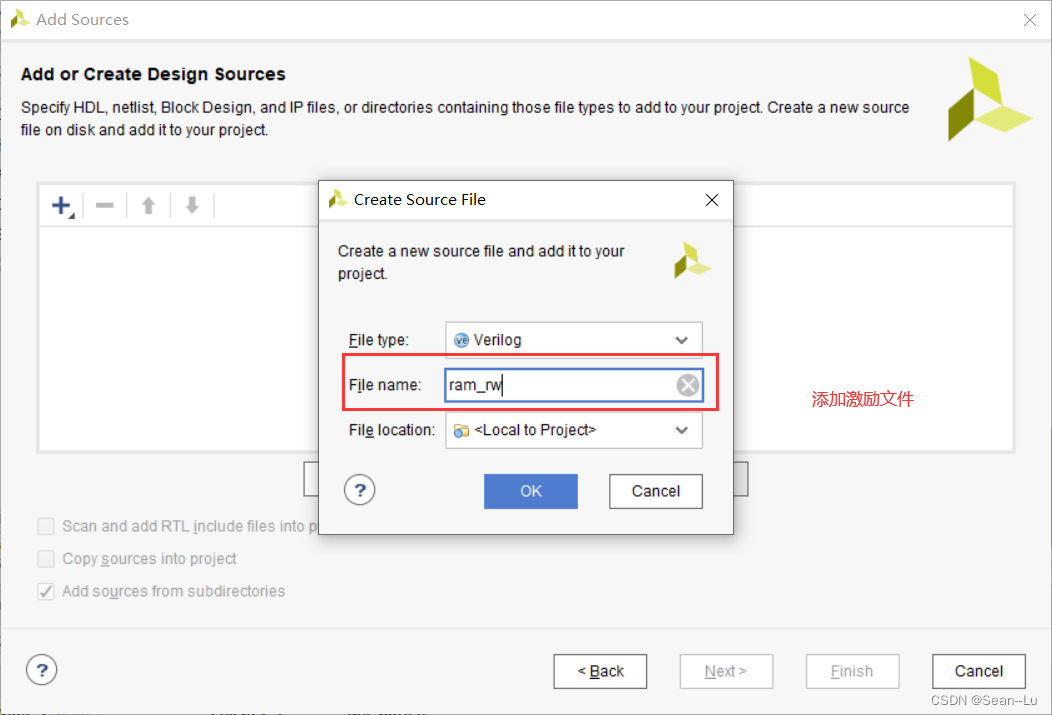

1.创建.v文件

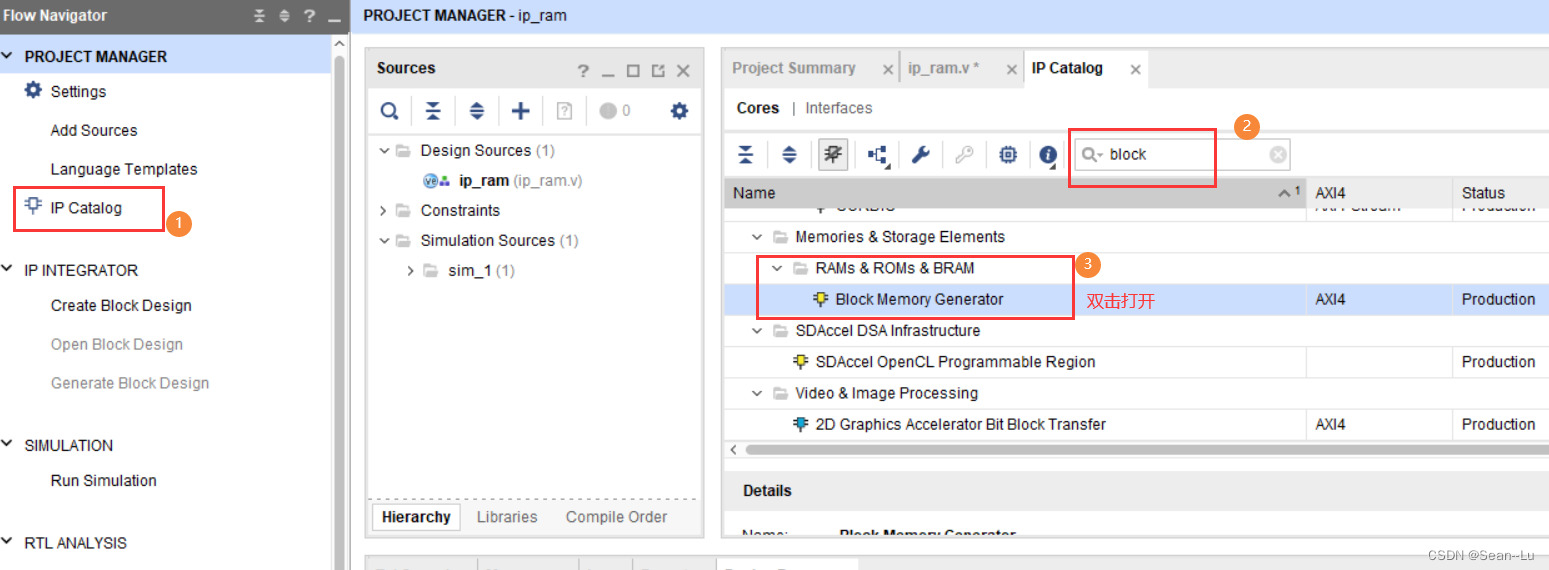

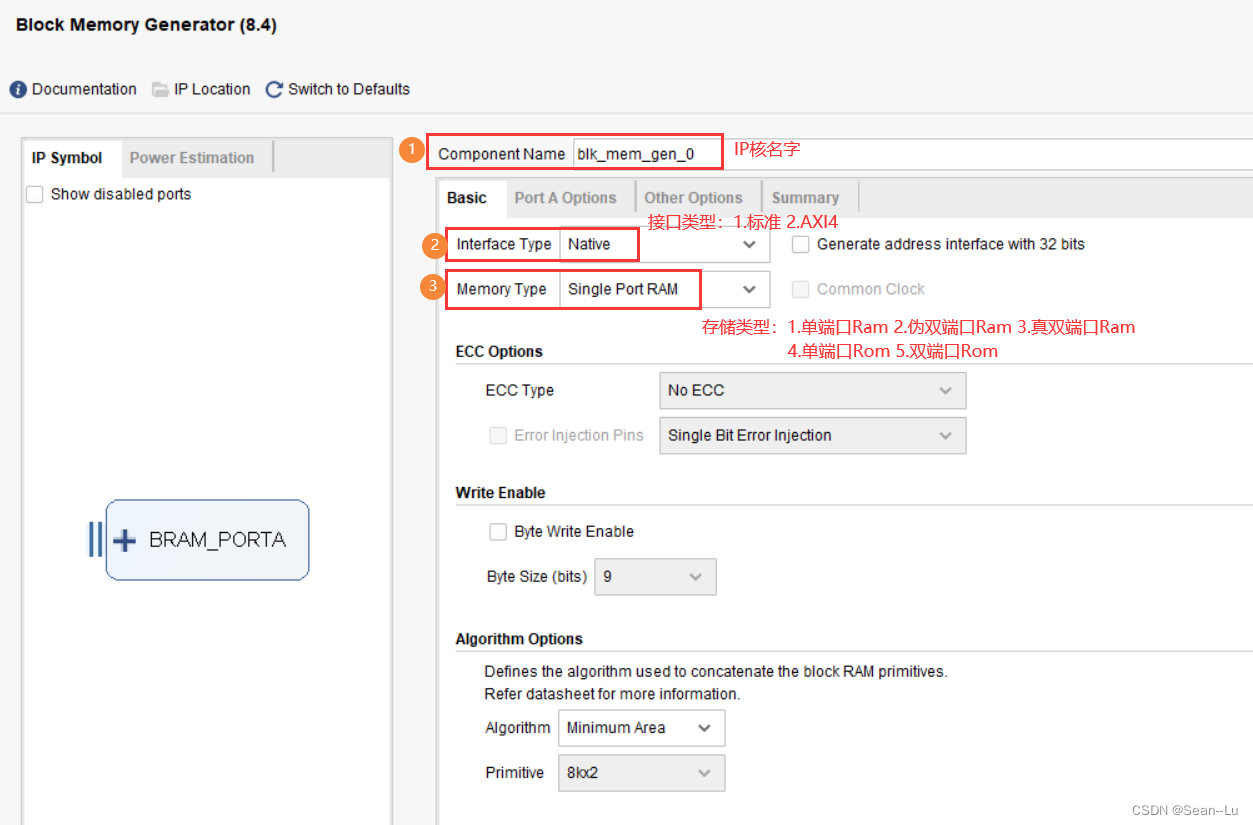

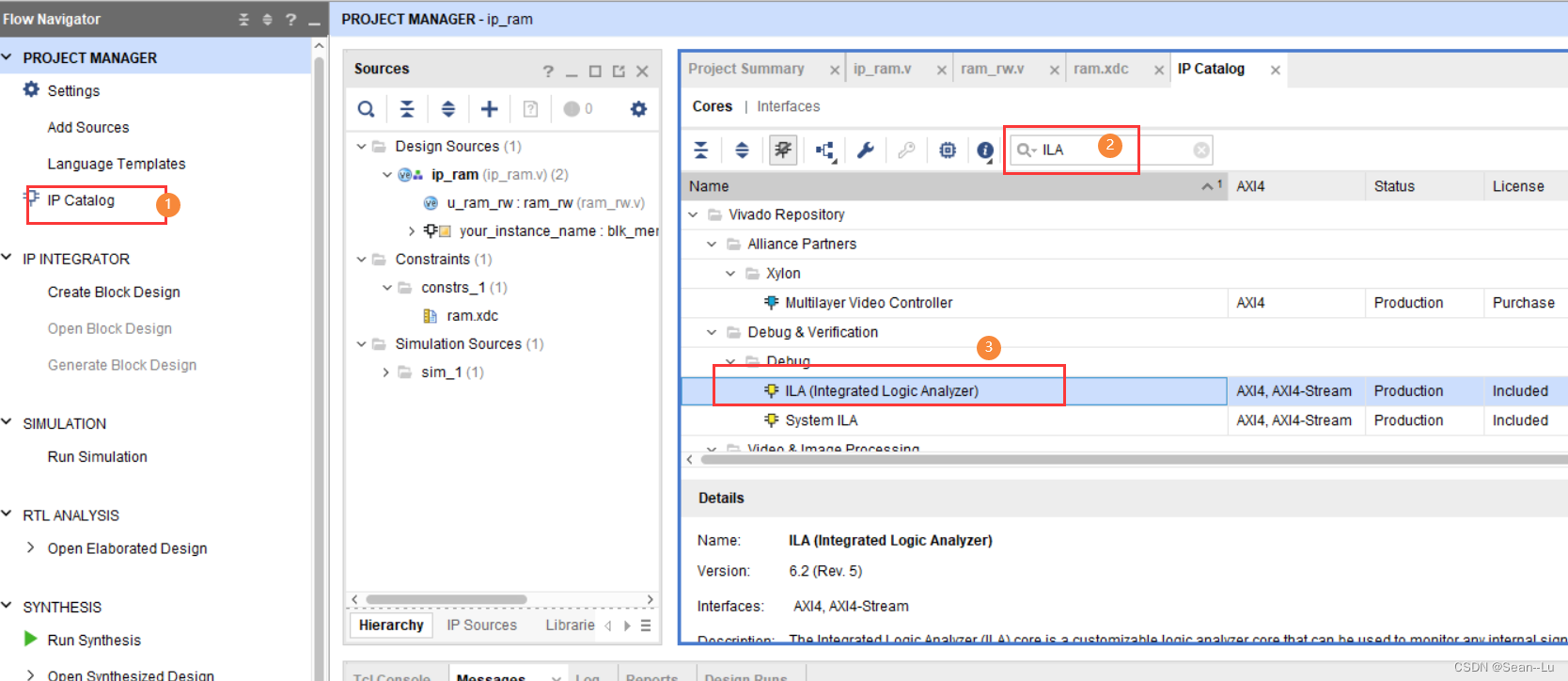

2.首先添加整体时钟和复位,然后打开IP Catalog,添加Ram IP核

3.Basic页面说明

1)FPGA没有真正的Rom,使用的DRam模拟Rom,只启用读操作。体现了FPGA的灵活性。

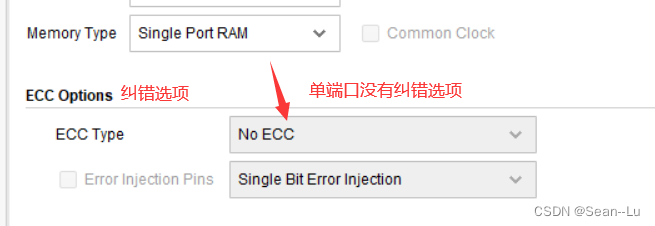

2)纠错选项

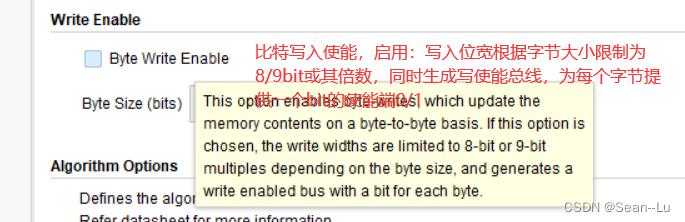

3)比特写

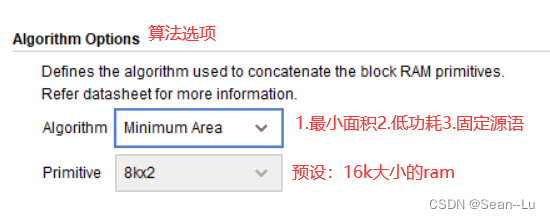

4)算法选项

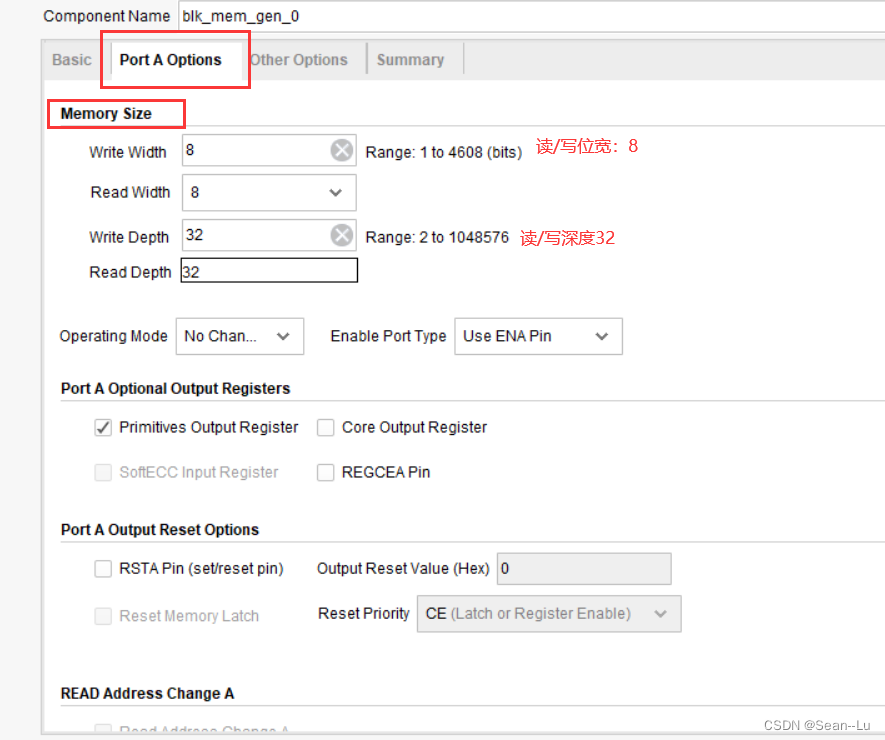

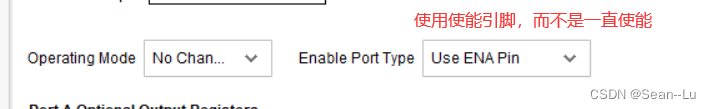

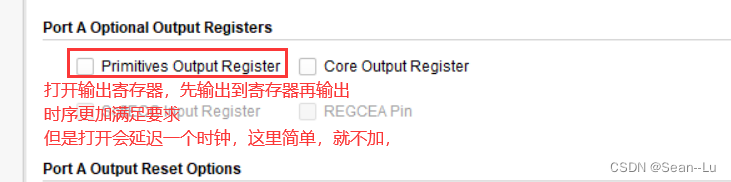

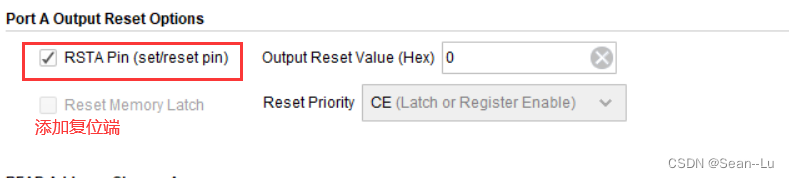

4. Port A Option页面

存储器的知识,建议补充哈工大刘宏伟老师的计算机组成原理课程,否则不够了解相关的知识

页面中的其他选项说明:

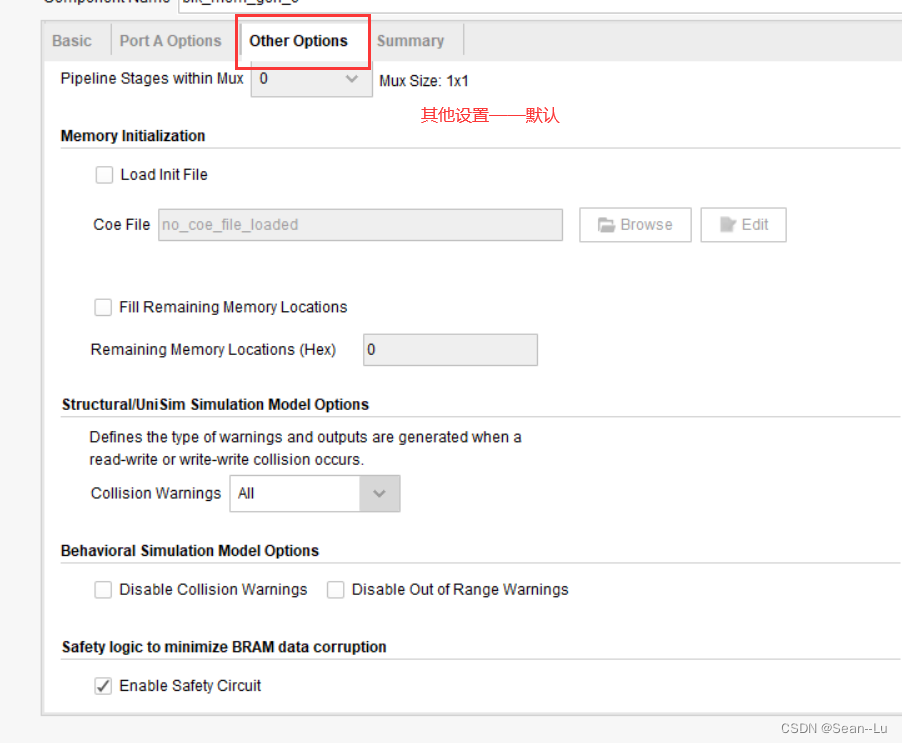

5.其他设置——默认

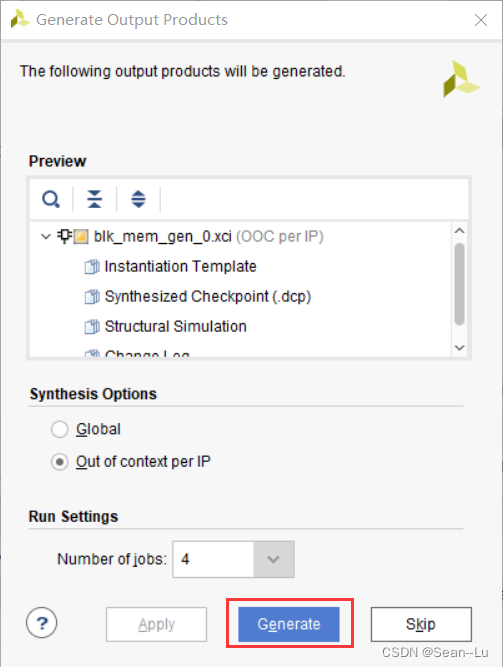

6. ok,生成ram ip核

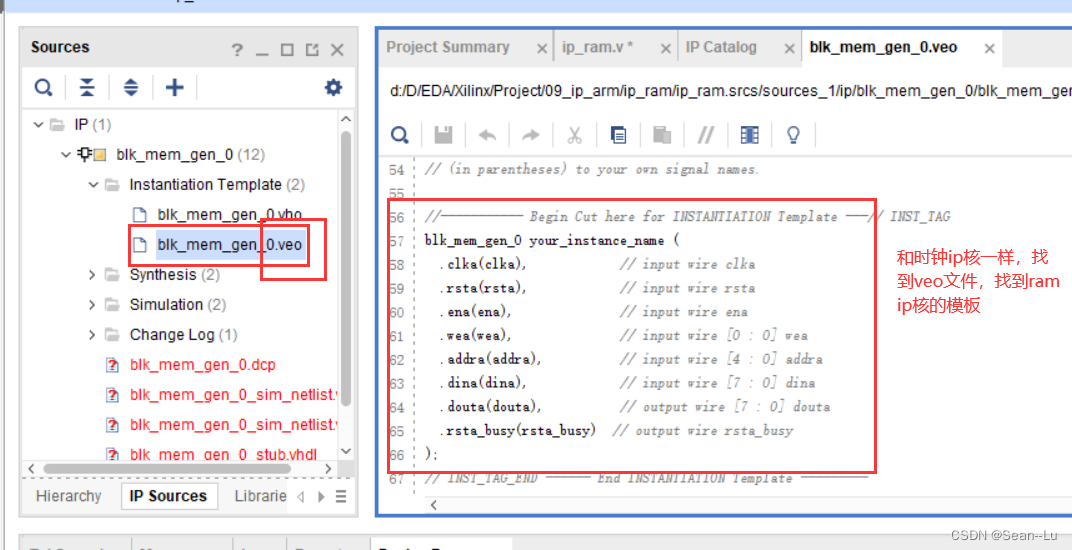

3. 找到生成的veo文件,复制到.v文件中,例化好,然后写激励文件

1.复制到.v文件中,例化需要等到激励文件写好后才能输入到这边例化

2. 编写激励文件

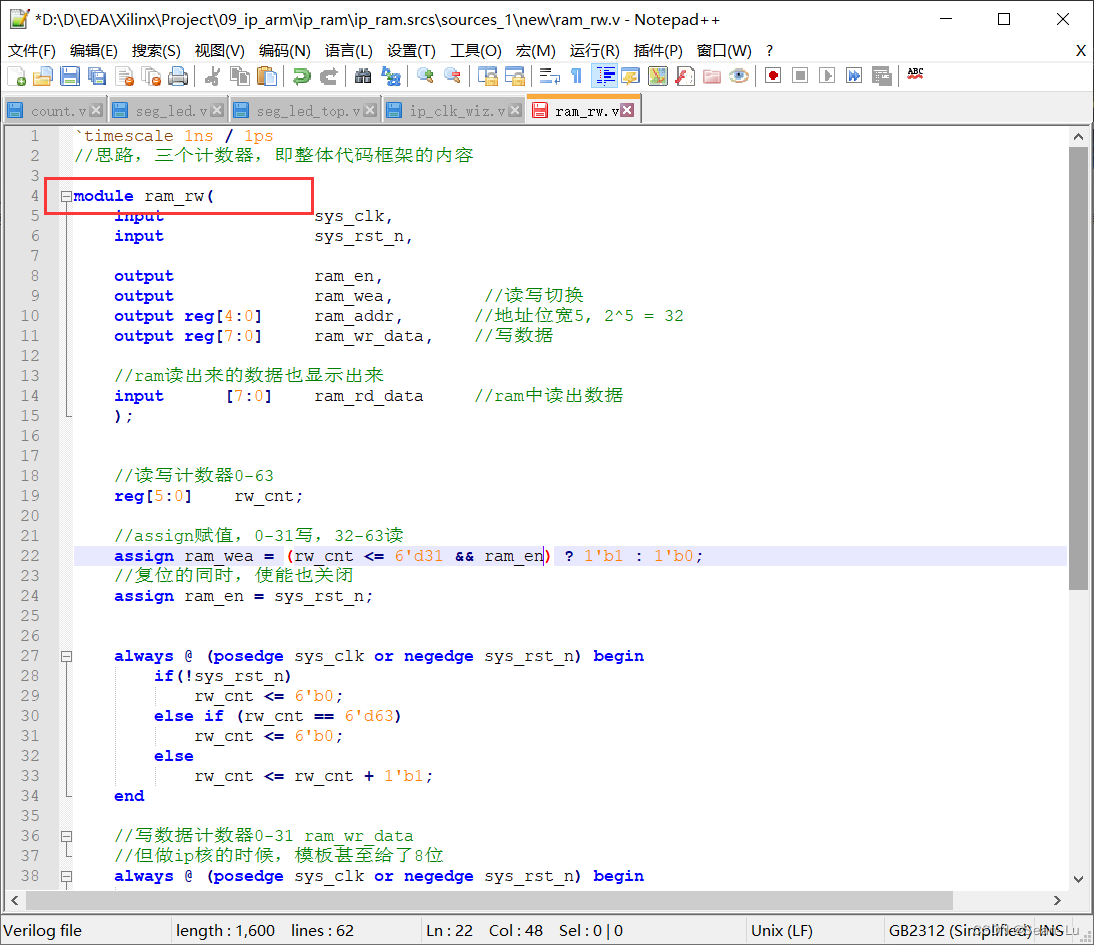

思路,三个计数器,即整体代码框架的内容(最开始)

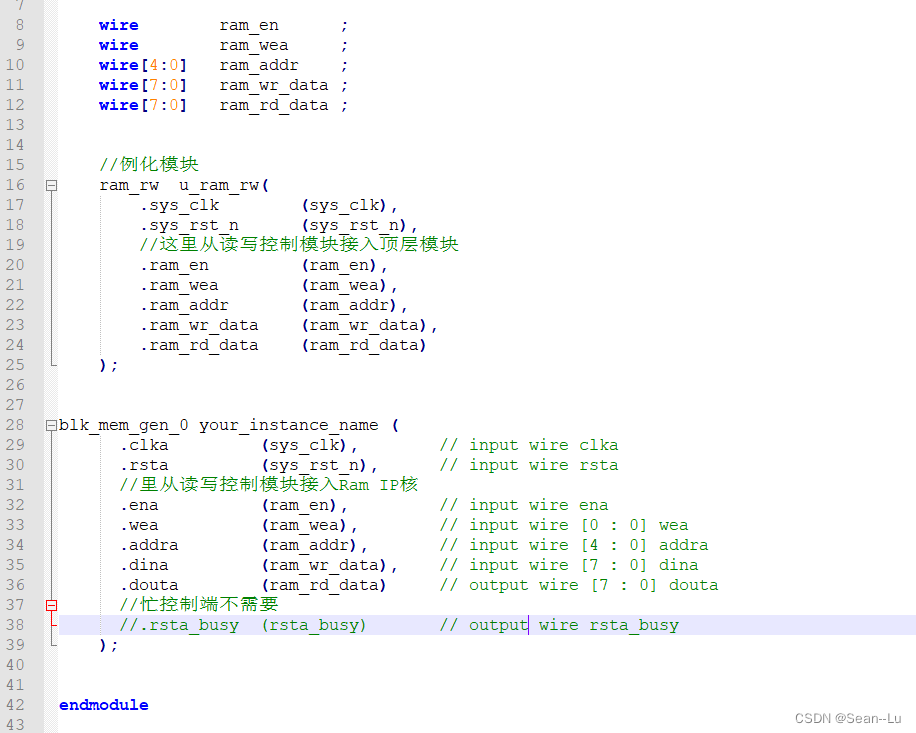

例化

3.先综合一下,还要做xdc约束,下载bit流到板子,再做ILA逻辑分析

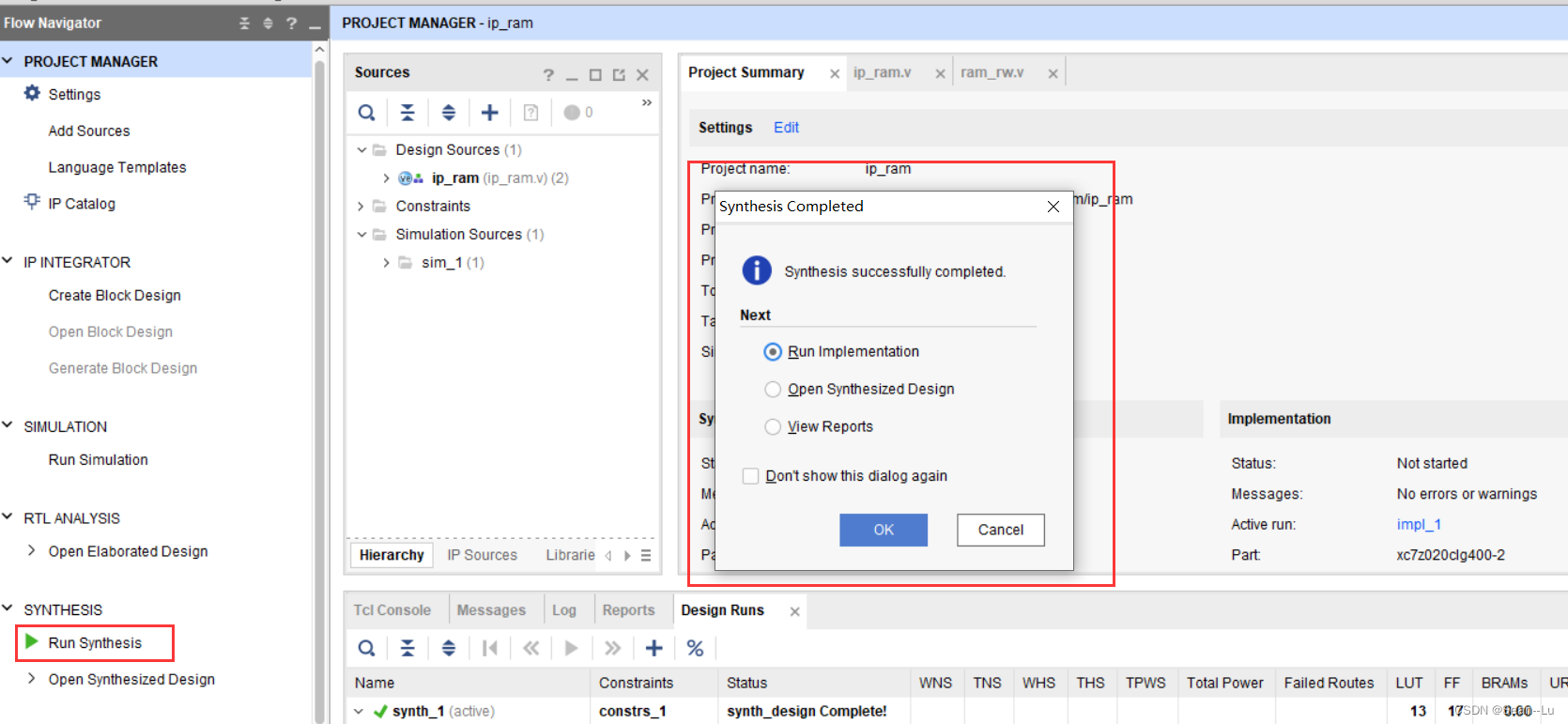

1.综合无误

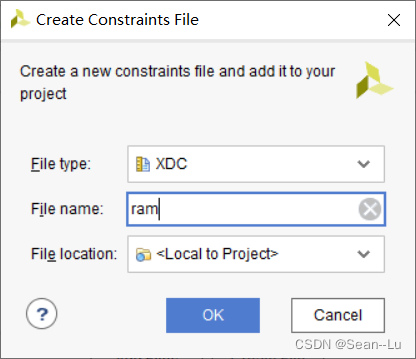

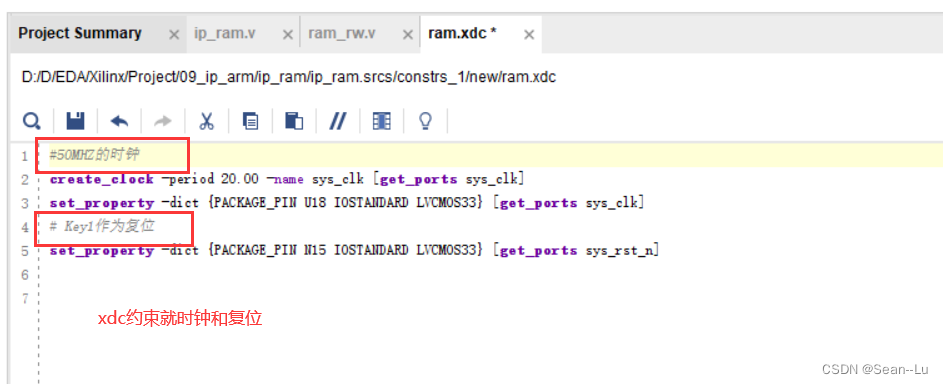

2.添加ram.xdc

我的板子是ZYNQ7020的板子:

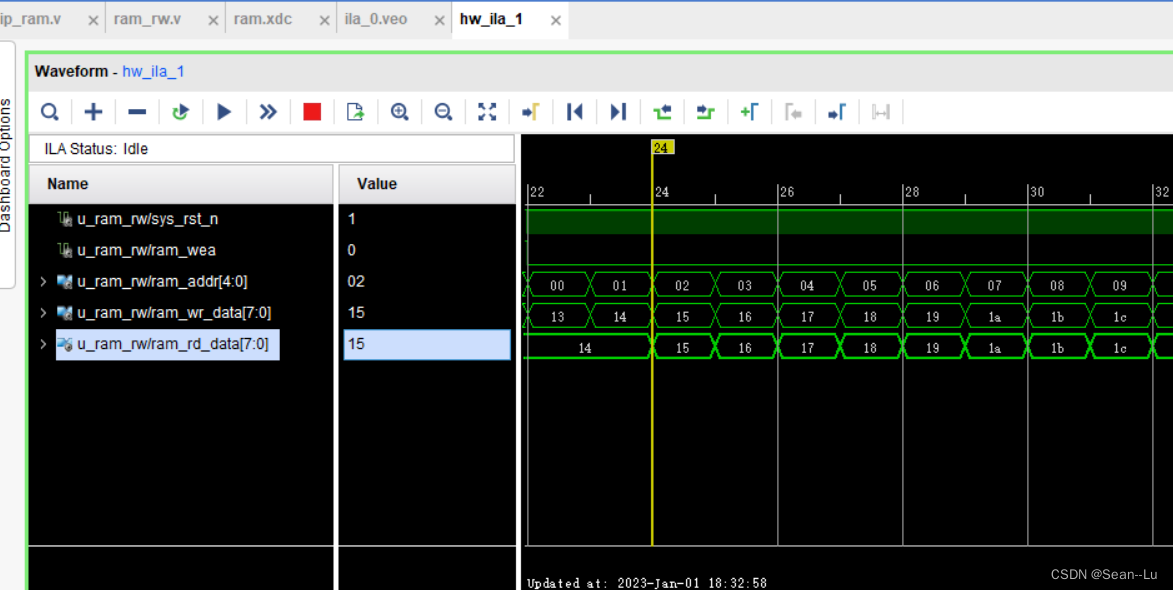

3.下载bit流到板子里,然后使用ILA逻辑分析仪即可——验证 读/写数据 是否一致!

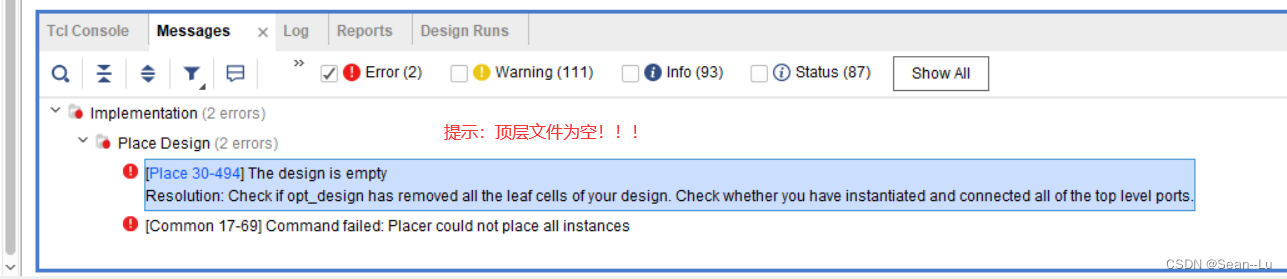

很不幸,代码先报错了,被Vivado优化了代码。整个代码对外界没有影响,唯一的输出没有输出。

因为顶层只有时钟、复位输入,而模块有输出,可以直接在顶层模块加一个输出。

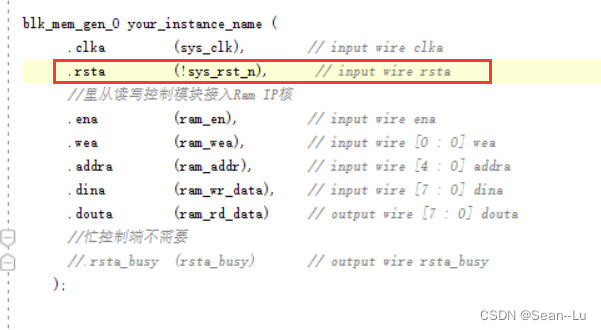

但我们这里用ILA,不想写成输出的ram_rd_data(读数据),换一种写法——直接添上ILA。

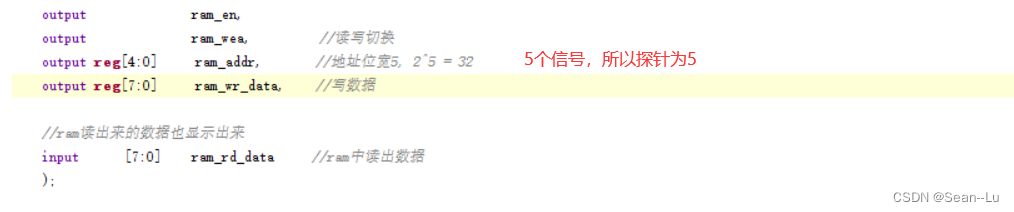

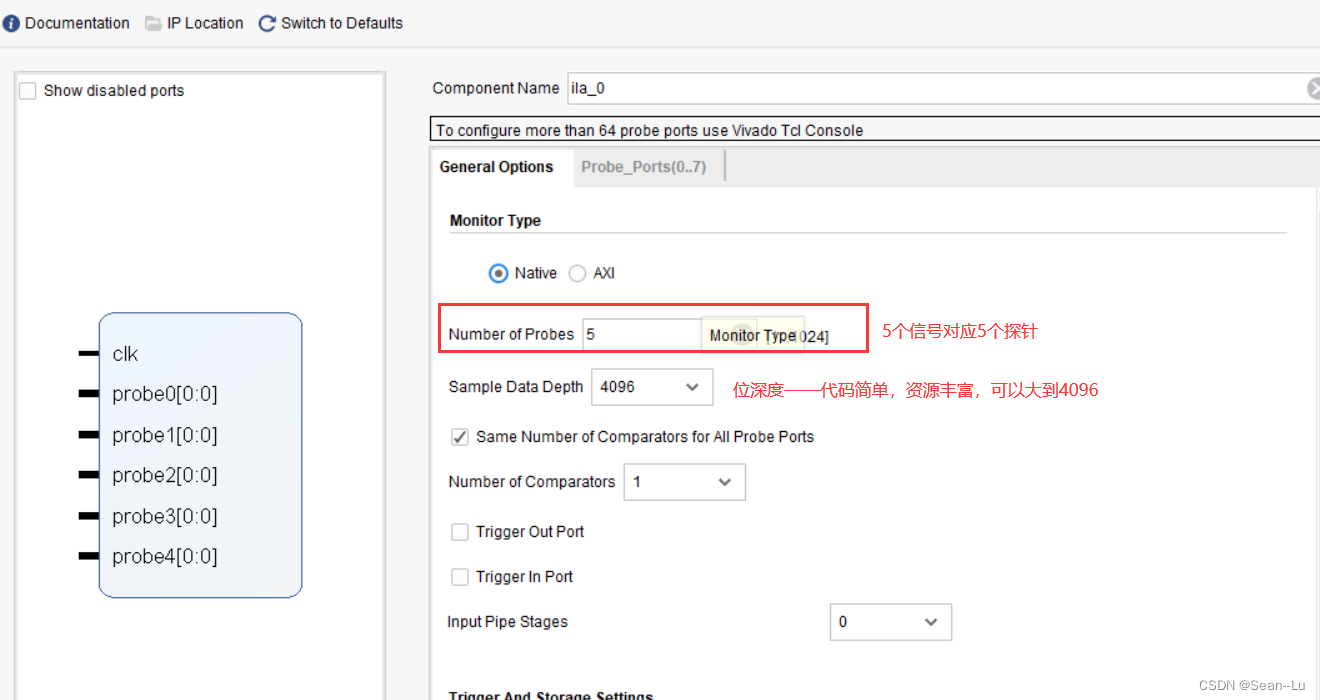

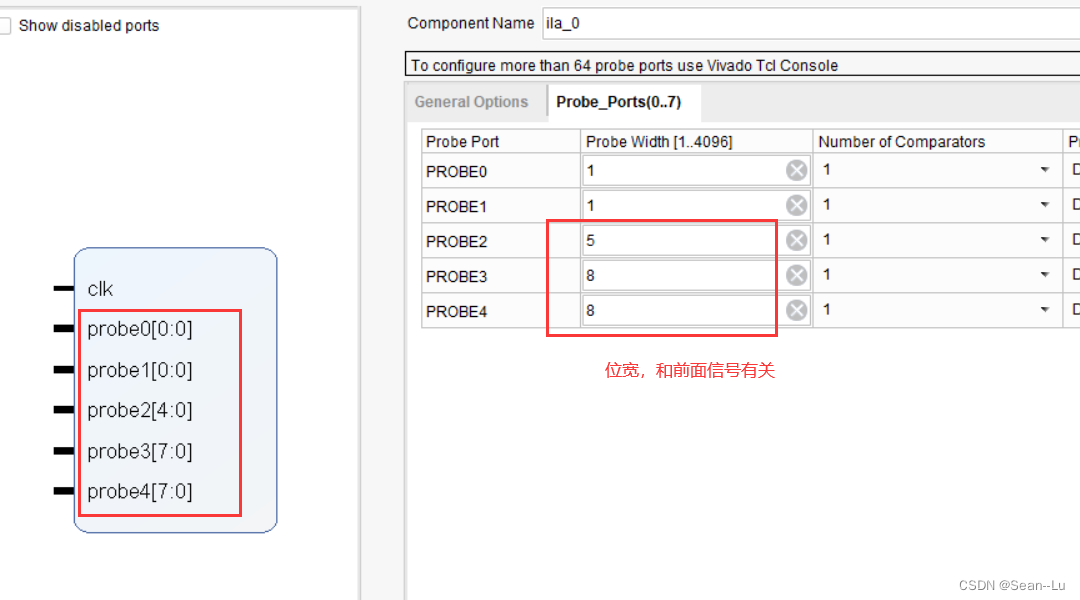

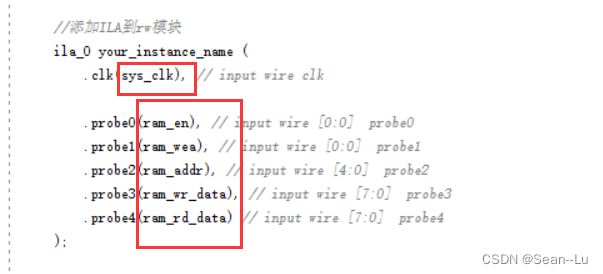

3.1ILA生成器

3.2添加ILA到rw模块,设置好引脚,保存——生成bit流文件!

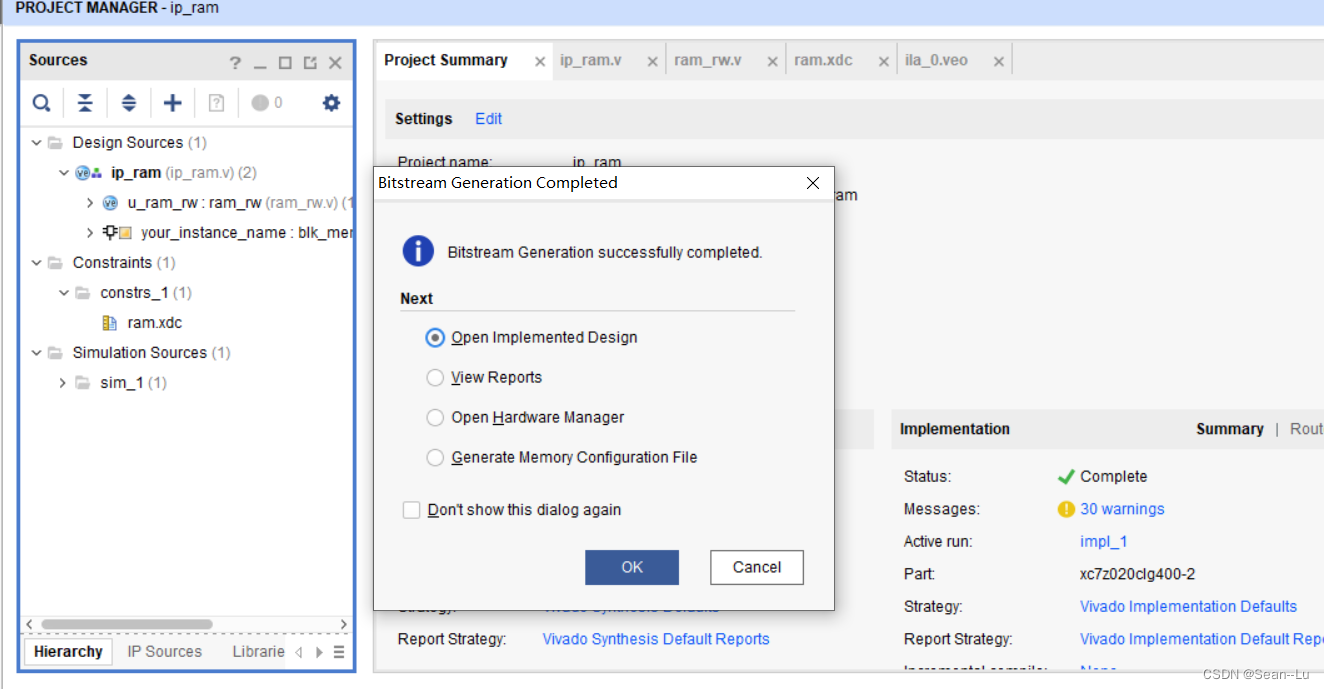

成功!

复位信号如果常高,这里要取个反

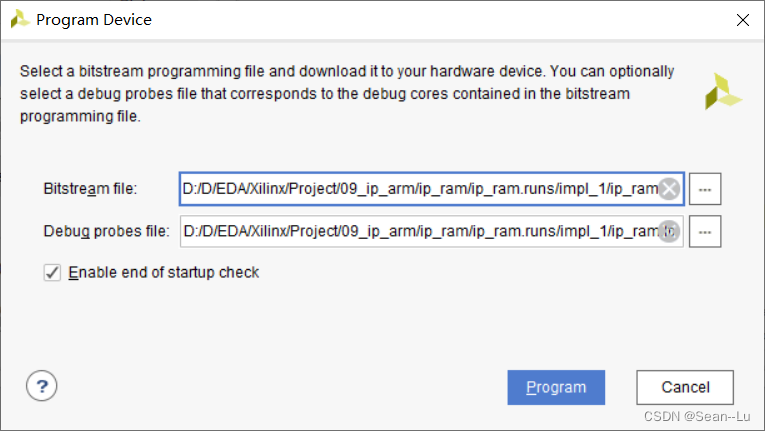

3.3连接硬件,烧录bit流

能够看到bit流文件和ILA文件都生成了!

结果——可能不对,因为我对自己的板子还不太熟!

结束!

3138

3138

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?