1.前言

过年放假在家,没有上班的压力,可以学点东西。只不过每天效率好低哦,乘着这个时间哦,学点在公司可能不太重视的基础的东西哦。想往通信这个方向进行发展,可是本科的时候是一个材料狗,那要补的东西实在是太多了,再加上大学根本没学,数学这些东西基本白给。补回来好累。

2. PLL的整体结构

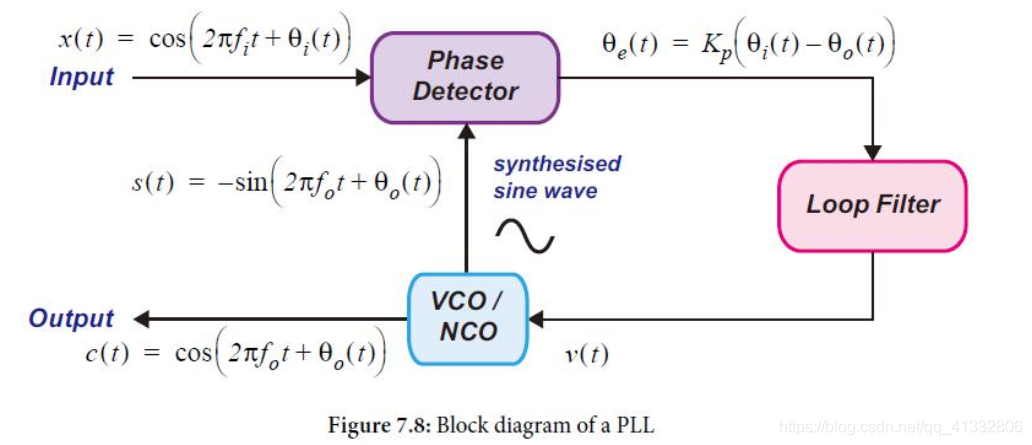

提到PLL,对于FPGA开发人员来说,想到的第一个东西,那肯定是FPGA里面会使用到的用于生成时钟的那个IP核了,PLL的作用就是能够生成一个稳定的时钟,在分频倍频的时候用的很多.在通信当中,PLL的作用其实和在FPGA里面的作用是一样的,PLL 是同步问题的重要组成模块, 它们能够重新生成一个正弦波, 跟踪它频率的变化, 抵抗噪声的影响。 这个简单的电路, 只需要 3 个组件就能实现, 可以是模拟的也可以是数字的。

一个PLL主要包括三个部分:

1. 鉴相器

2. 环路滤波器

3. 压控振荡器VCO/NCO

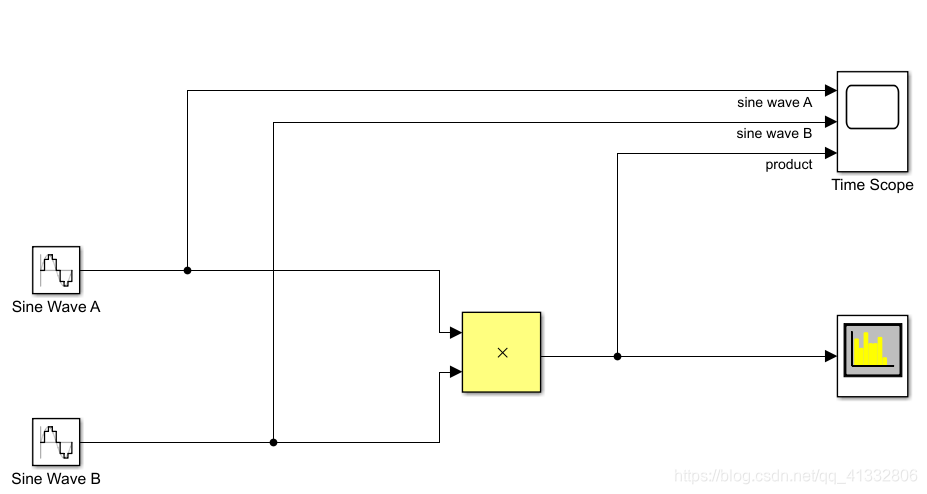

2.1 鉴相器

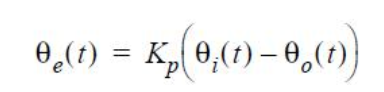

鉴相器的作用是用来比较生成的正余弦信号和参考信号之间的差值。然后把这个相位差按照比例生成另外一个信号。一般把这个相位误差叫做相位误差信号。

Θ

i

\Theta_{i}

Θi 和

Θ

o

\Theta_{o}

Θo 分别是输入的参考信号在 t 时刻的相位和本地振荡器NCO/VCO生成信号在 t时刻的相位。 Kp 是鉴相器的增益。

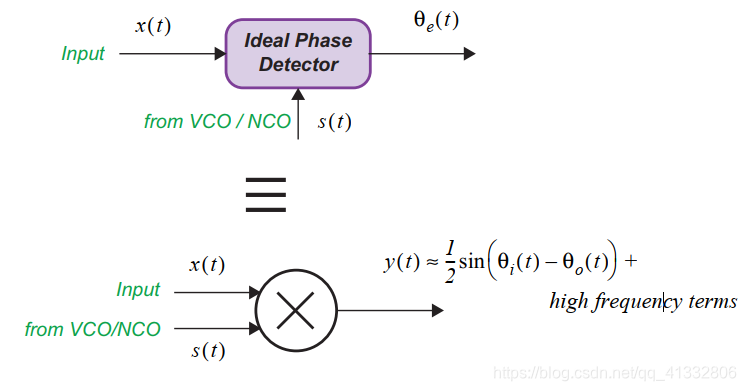

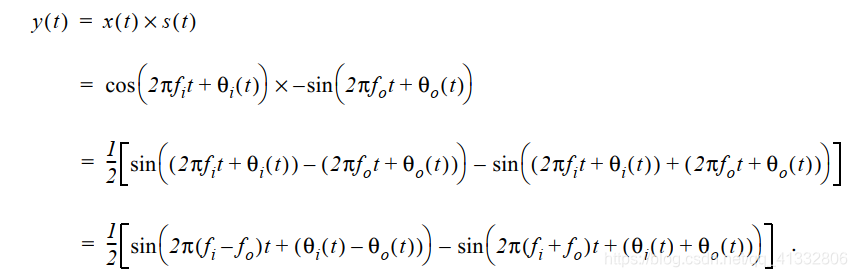

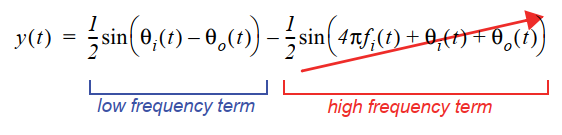

一般来说,鉴相器就是一个乘法器,使用一个乘法器就能够完成本地生成信号与输入参考信号之间的相位差值。使用乘法器,使用和差化积公式,会得到一个低频分量就是两者的相位差,一个高频分量,需要使用滤波器将高频分量滤除。

假设输入信号是:

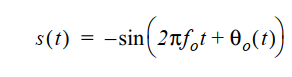

本地生成的参考信号是:

经过乘法器之后的结果是:

由于使用了PLL,那么最终生成的频率,

f

i

f_{i}

fi和

f

o

f_{o}

fo应该是相同的,所以最终可以得到

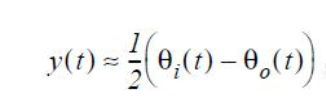

又由于使用到了PLL,最终的这个相位差不会太大,是一个很小的量,这个时候就可以做一个线性近似了。

鉴相器的直观感受

产生两个相位不同的信号,然后将这两个信号进行相乘,最后观察结果。这两个信号分别为

s

i

n

(

2

π

∗

5

t

)

sin(2\pi *5t)

sin(2π∗5t) ,

s

i

n

(

2

π

∗

5

t

+

π

/

3

)

sin(2\pi *5t + \pi/3)

sin(2π∗5t+π/3)

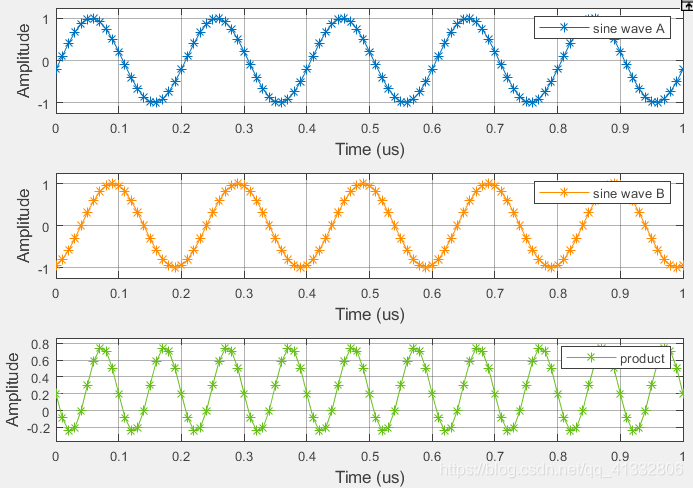

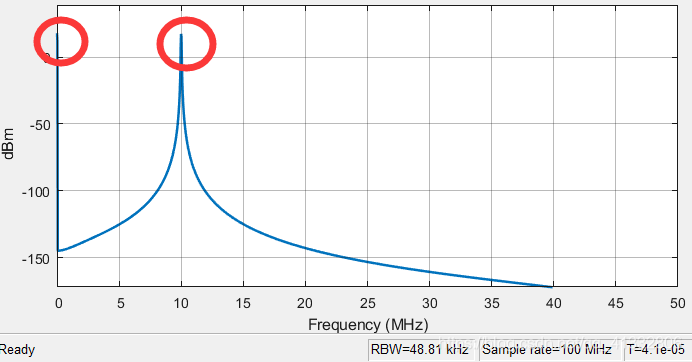

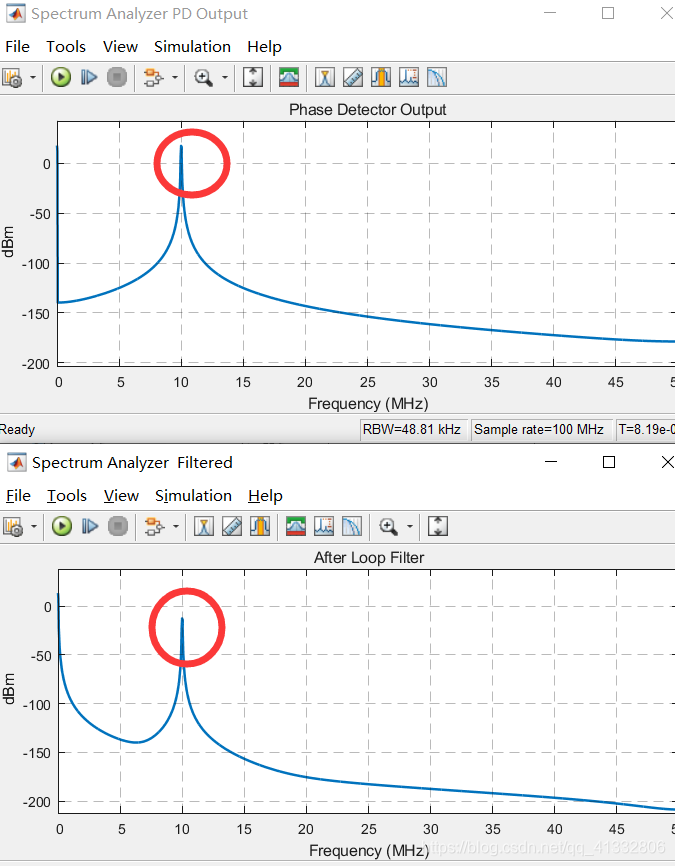

从结果中可以看到,得到了两个同频不同相的信号相乘之后,得到了一个高频信号,并且可以看到,信号被抬升了。根据三角公式,很快就能想过来了,生成了一个2倍频率的信号,于此同时,在零频率附近产生的是一个对应相位差的这个直流信号。

2.2 环路滤波器

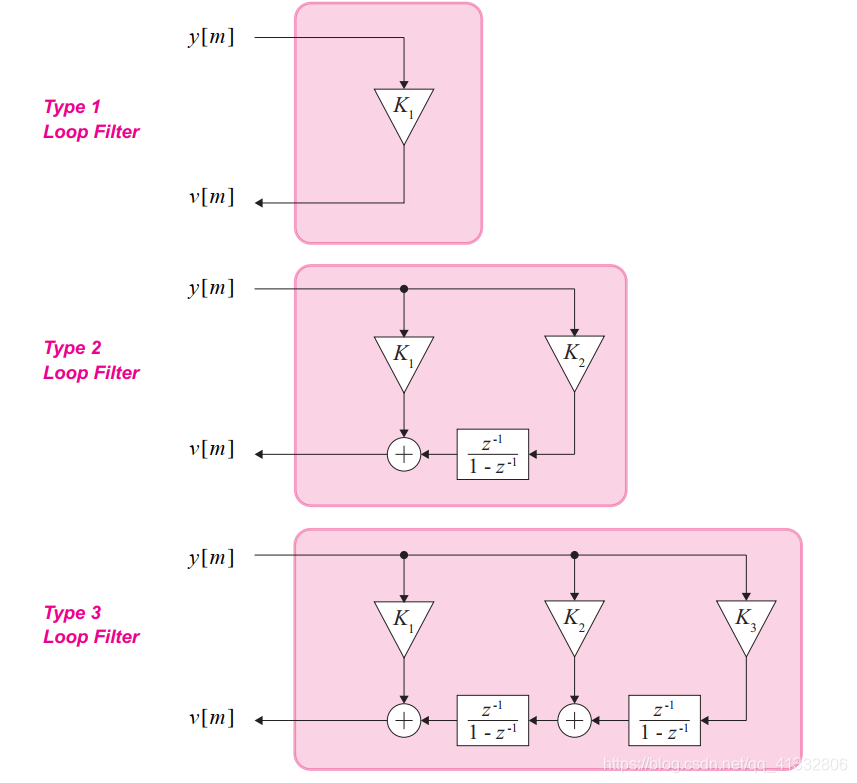

环路滤波器的任务是过滤鉴相器输出的错误的信号。 大多数情况下, 环路滤波器只是一个简单的低通滤波器, 由比例路径和积分路径组成。 设计环路滤波器对于 PLL 的整体特性影响很大。

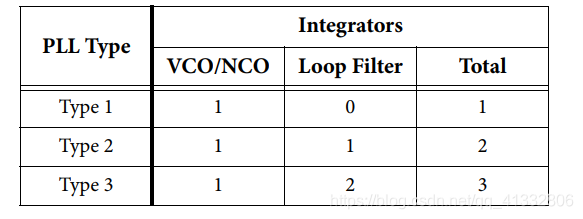

PLL的类型对应环路中的积分器的数量,大多是情况下,一个type2 类型的PLL能够胜任大多数PLL的工作.

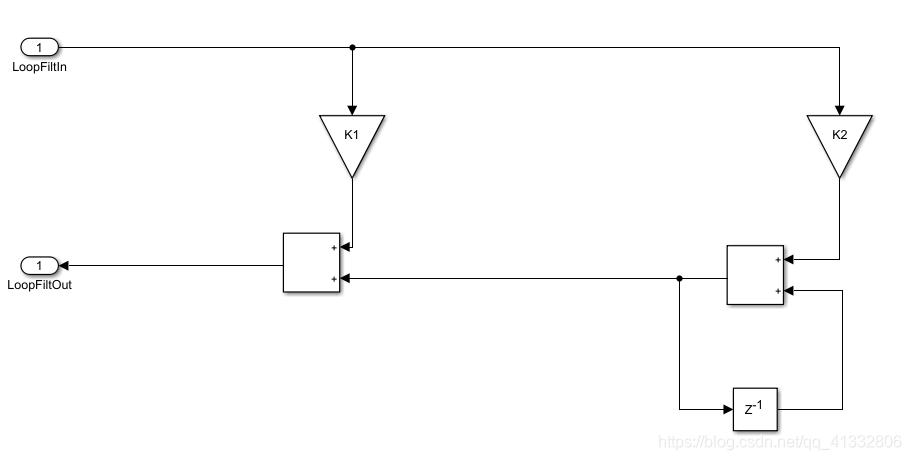

type2类型的PLL在环路滤波当中具有一个积分器,也就是具有一个反馈的结构.

环路滤波器的设计是整个PLL设计中最重要也是最复杂的部分,环路滤波器决定了PLL的性能.

一个type2 的滤波器的结构如下:

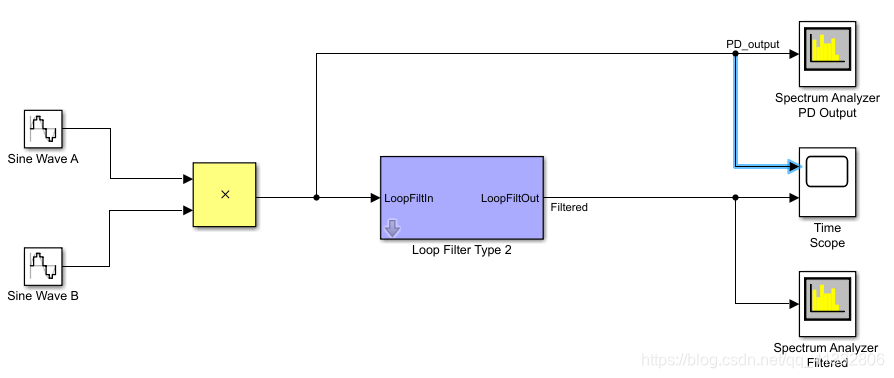

如果在前面的鉴相器中,加入这么一个环路滤波器那么就可以把高频分量滤除了。

经过滤除之后,就得到了期望的相位误差了。

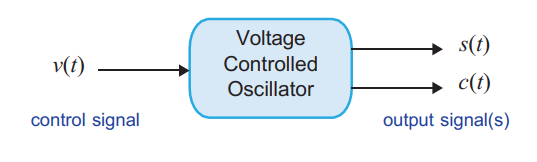

2.3 压控振荡器

2.3.1 压控振荡器 VCO

在滤波器结构当中,经过环路滤波之后的相位差,作为控制信号,提供给VCO/NCO用于修正产生信号的频率,

v

(

t

)

v(t)

v(t)越大,产生的修正也就越大.

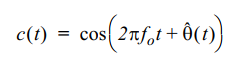

输出的余弦信号可以表示为以下形式:

Θ

(

t

)

\Theta(t)

Θ(t)是当前的相位,由误差信号积分得到.

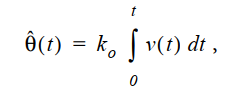

2.3.2 数控振荡器NCO

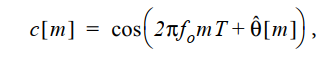

NCO的结构和工作方式和VCO基本一致,只是将在数字域中对信号进行处理。数控振荡器和压控振荡器类似,会产生一个余弦和正弦信号,由一个控制信号

Θ

[

m

]

\Theta[m]

Θ[m]来修正产生的频率。

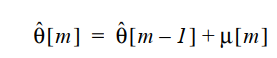

控制信号

Θ

[

m

]

\Theta[m]

Θ[m]和压控振荡器一样,也是由前面的环路滤波得到的结果进行积分。

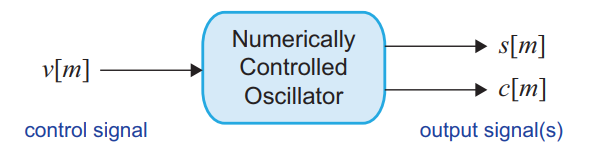

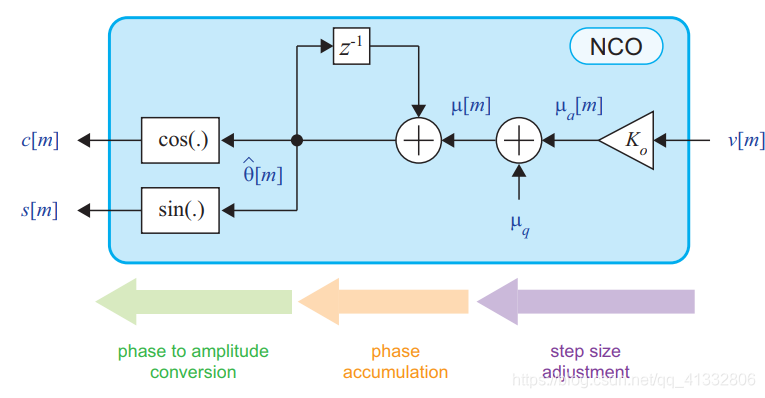

2.3.3 NCO的工作过程

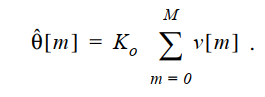

固定步长NCO

NCO内部的操作经常使用步长来描述,假设步长是固定的,那么NCO每次增加的相位为

u

[

m

]

u[m]

u[m]:

这个步长控制着相位的变化速率,也就控制着生成的余弦波信号的频率。步长越大,那么产生的余弦波的频率也更大。

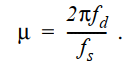

步长和采样率之间的关系如下:

其中

u

u

u是步长,

f

d

f_{d}

fd是目标频率,

f

s

f_{s}

fs是采样频率。

上面这种固定步长的形式,只能产生一个确定的信号,在NCO当中,输入的控制信号是一个在变化的量,所以在实际的应用中,是可变步长的形式。

可变步长NCO

u

[

m

]

u[m]

u[m]是NCO的步长,

u

q

u_{q}

uq是一个静态频率,

u

a

[

m

]

u_{a}[m]

ua[m]是一个变化的修正值,也就是和前面NCO输入的相位修正值相关的一个值,如下式所示:

NCO的示意图如下:

当本地生成的正弦波和参考输入的信号完全一致的时候,PLL鉴相器(前面介绍的乘法器)输出的结果是0,那么环路滤波输出的就是一个常量,当PLL锁定完成之后,NCO的步长就基本保持不变了。

3 小结一下

从上面的PLL的结构不难看出,PLL的设计主要就是这三部分。鉴相器得到当前输出的信号和参考信号之间相位差,以便能够在之后调整输出。环路滤波将会滤除鉴相器得到的高频分量,只保留低频分量。NCO会根据误差信号来动态地调整输出,最终能够达到跟踪输入信号的作用,完成锁相。

在设计PLL的时候,最重要的一个步骤就是来设计环路滤波器,只有正确地设计了环路滤波器的系数了,才能够完成最终的锁相。

2251

2251

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?