跨越鸿沟:从算法到硬件实现

2.1数字信号处理系统架构分析;

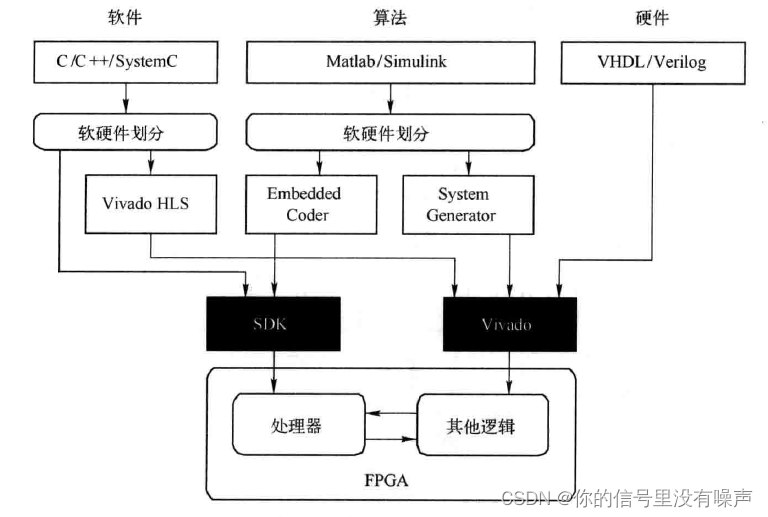

2.2数字信号处理系统设计方法;2.2.1传统的RTL设计方法2.2.2基于模型的设计方法·2.2.3高层次综合设计方法2.2.4三种设计方法的融合

2.3FPGA设计性能描述指标:

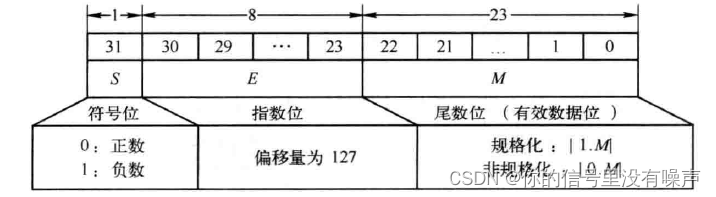

2.4FPGA设计中的数据格式;2.41 浮点数基础知识.;2.4.2 定点数基础知识;2.4.3浮点数与定点数的比较;2.4.4 浮点数到定点数的转换·。

2.5Xilinx开发工具对浮点数与定点数的支持: 2.5.1SystemGenerator对浮点数与定点数的支持;2.5.2VivadoHLS对浮点数与定点数的支持。

文章目录

前言

信号处理关注的是信号及其所包含信息的表示、变换和运算。例如,希望分开两个或多个混叠在一起的信号,或者增强某些信号分量或一个信号模型中的某些参量。

一、2.1数字信号处理系统架构分析

- 数字滤波和傅里叶变换(DFT)是数字信号处理领域最为常见的的两种处理方式。数字信号处理系练的性能取决于三个因素:采样频率(Sample Frequencu)、架构(Architecture)和字长(Word length,也称位宽)。这三个因素对系统性能如系统速度、系统带宽、系统功耗以及系统资源等起着决定性的作用。

- 数字信号处理单元是数字信号处理系统的核心部件。目前,主流的处理单元可分为三类:指令集处理单元、硬连线结构处理单元和可重构处理单元。

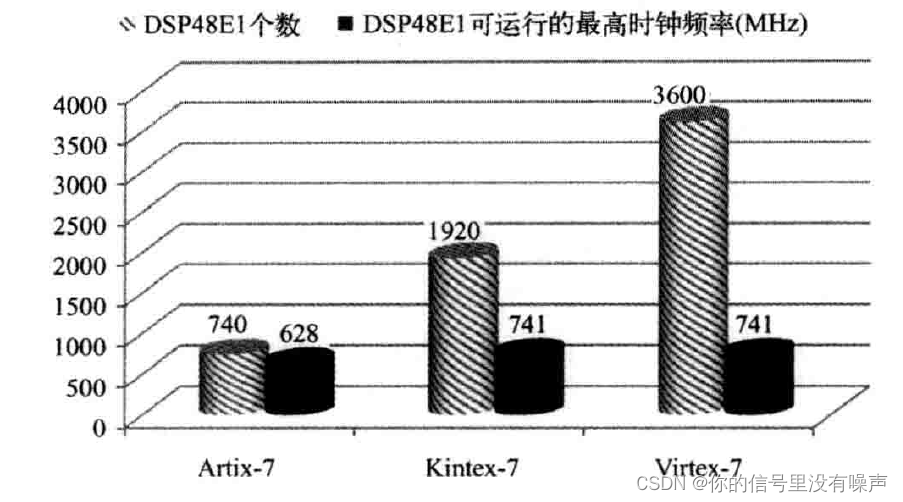

- ZYNQ有大量的MAC(Multiply-Accumulator硬线,可以在全流水模式下高速运行)和BLock_RAM可提供2622GMACS的算力 (GMACS表征了DSP48每秒执行的乘加次数)。

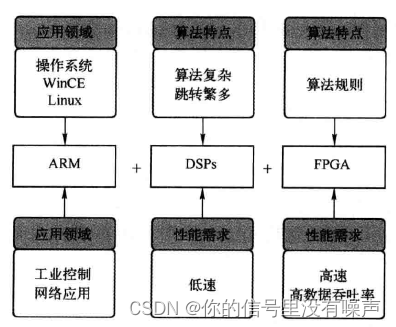

- 综上所述,对于性能要求极高的应用,可将复杂算法划分为底层部分和顶层部分,结合DSP 处理器和

FPGA各自的结构和功能特点,将算法的各部分映射到不同的硬件模块上,在系统功能上实现互补。底层部分用于数据处理量大、速度要求高、但是算法结构相对比较简单的算法,适宜于用 FPGA 硬件的高度并行性实现,可同时兼顾速度及灵活性,如一定长度的 FFT/IFFT、FIR 滤波等算法。顶层部分处理的特点是所处理的数据量较底层部分少,但算法的控制结构复杂,适宜于运算速度高、寻址方式灵活、通信机制强大的 DSP 处理器或ARM处理器。FPGA+DSPs 处理器、FPGA+ARM处理器以及 SOC FPGA 的架构是目前高性能数字信号处理系统的主流方式。这种结构非常灵活,有较强的通用性,适于模块化设计,有利于提高算法效率,缩短开发周期,并易于维护和扩展。

二、2.2数字信号处理系统设计方法

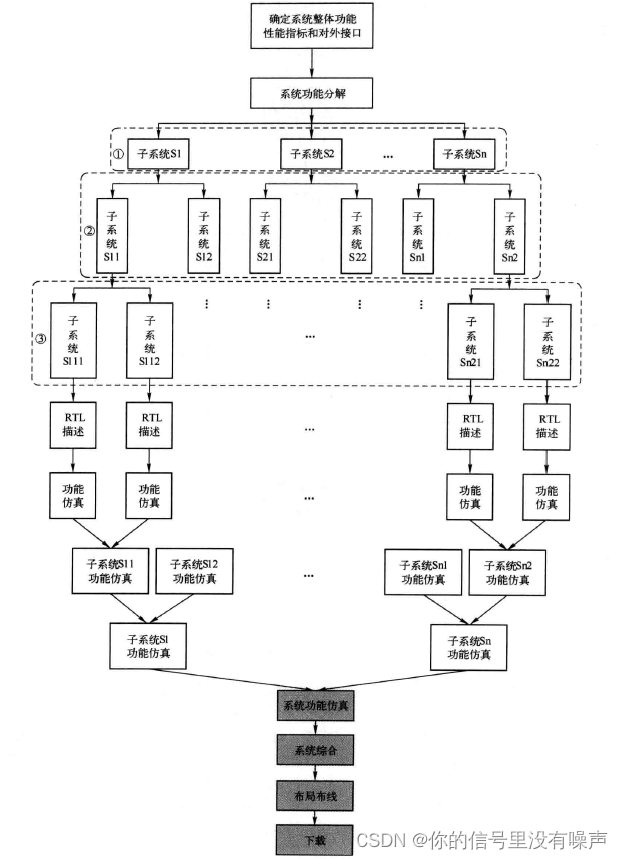

2.2.1 传统方法

- 需求分析;

- 算法仿真;

- 算法分解到软硬件的实施(FPGA适合高速数据处理的算法);

- 算法实现;

- 系统集成,验证和联调;

2.2.1 基于模型的设计方法&高层次综合设计方法

1、基于模型的设计方法

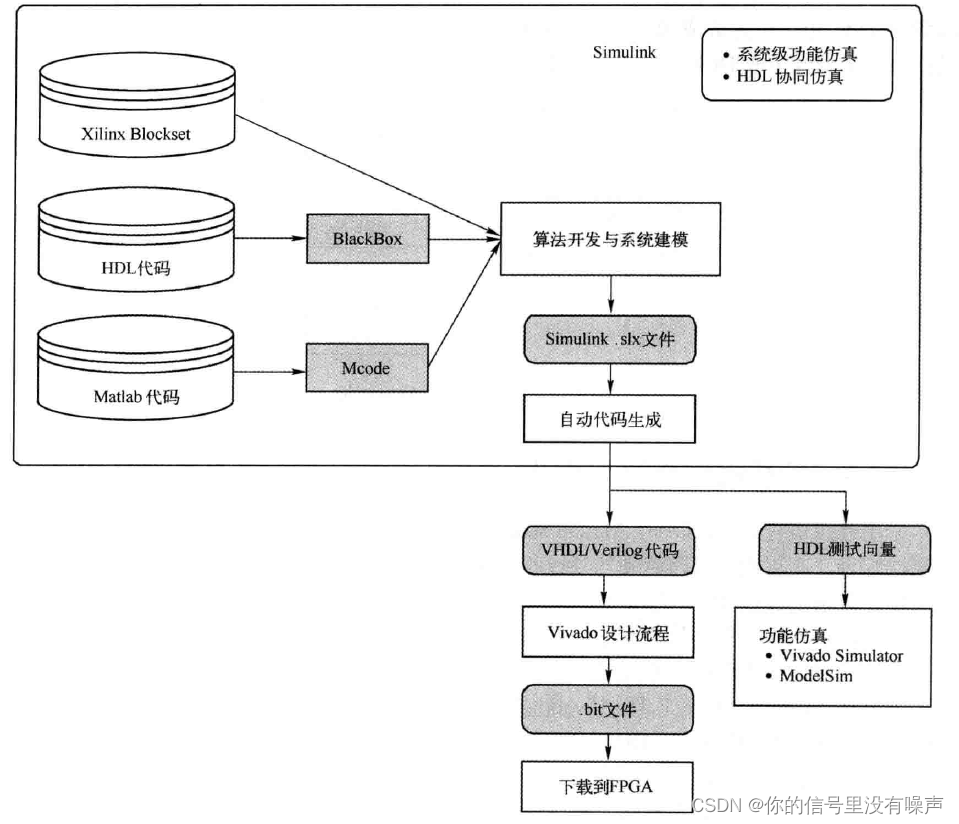

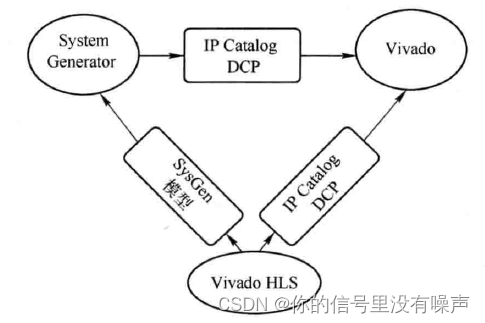

众所周知,Matlab 是业内广泛使用的反映较好的算法开发和验证软件,过去长时间主要应用于系统级的算法仿真和建模。SysGen 实现了 FPGA 与 Matlab的无缝链接,使 Matlab 这一系统设计工具与 FPGA 设计融为一体直接变为 FPGA 设计中的顶层设计工具。SysGen 不但接受设计师们习惯的 Matlab、Simulink、Verilog 或 VHDL语言,还支持混合使用这些语言或工具进行设计工作,这一点对团队开发尤为重要。

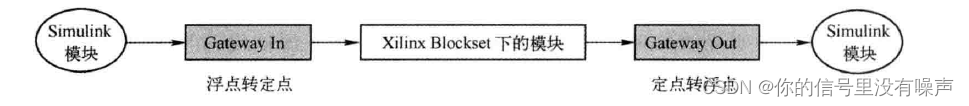

1)高效而丰富的IP模块:模块之间用gateway_in和gateway_out来过渡。

2)按位对齐和按周期对齐:FPGA 实现的硬件系统则是通过各模型的时钟周期建立的,两者实质是一致的,只是硬件系统工作在绝对的时钟频率下,Simulink 系统则工作在相对的时钟关系下。SysGen是按位对齐建模的,SysGen使在Simulink中搭建的模型与硬件实现之间保持按周期对齐。

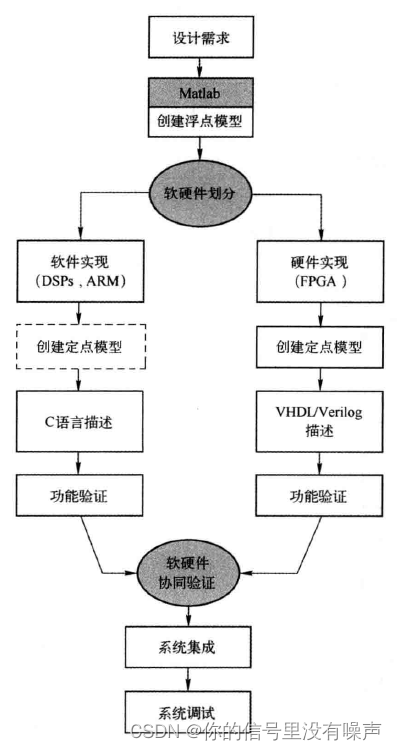

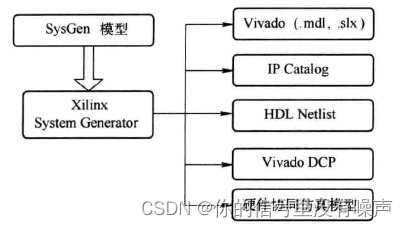

利用SysGen 进行数字信号处理系统开发的流程如图所示。系统建模、系统级功能仿真和HDL协同仿真都可在 Simulink 下完成。在系统建模阶段,可以利用 Xilinx Blockset下的模块,也可以利用已有的HDL代码通过 BlackBox模块导入到Simulink 工程文件slx中(HDL代码要符合 BlackBox 模块的要求),还可以利用已有的 Matlab 代码通过 MCode 模块导入到Simulink 工程文件slx中(Matlab 代码要符合MCode模块的要求)。

2、高层次综合设计方法

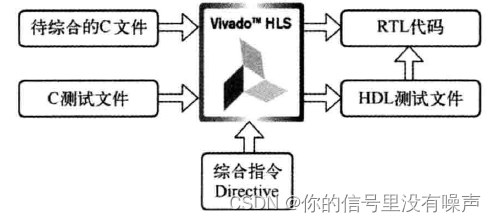

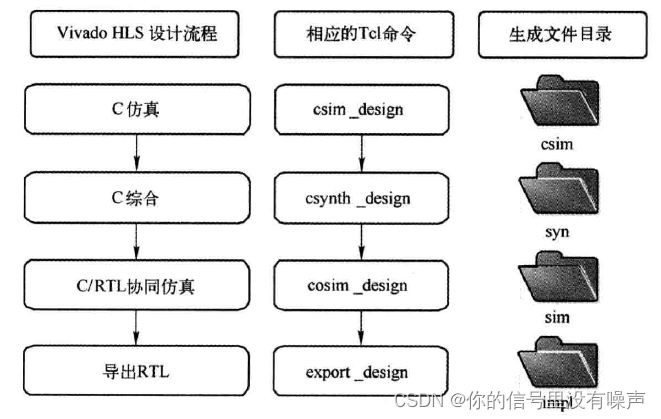

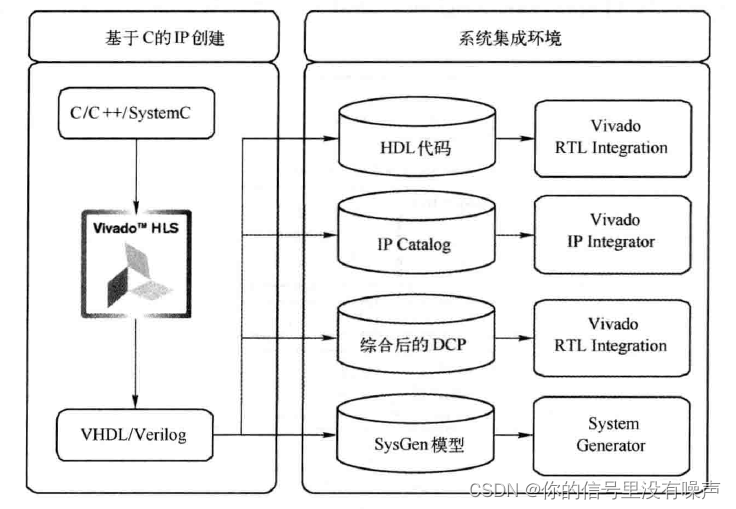

- VivadoHLS对C代码的转换过程可分为时序安排(Scheduling)、资源规划(Binding和控制逻辑提取(Control Logic Extraction)三个阶段。控制逻辑提取用于产生有限状态机 (Finite State Machine,FSM),以控制数据路径的操作顺序。

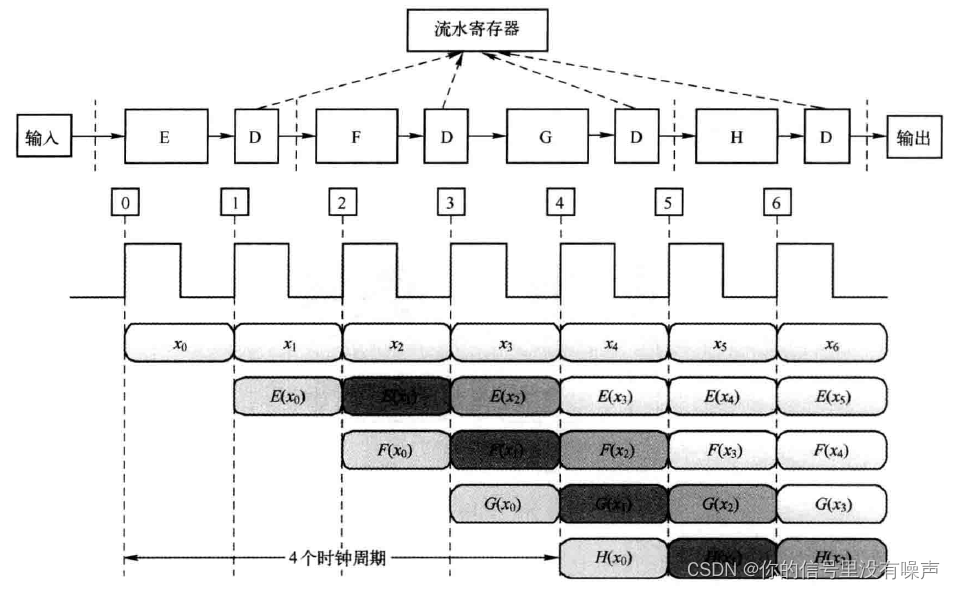

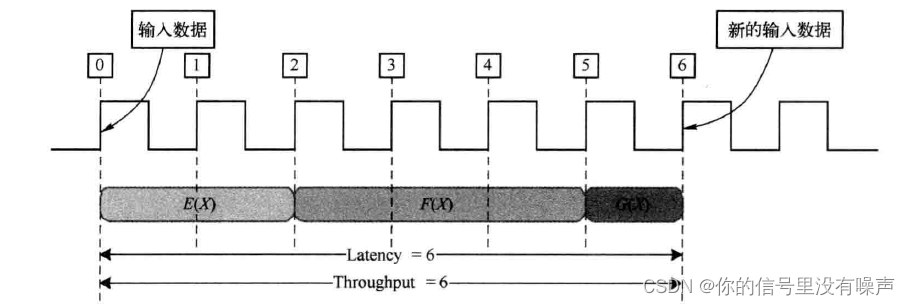

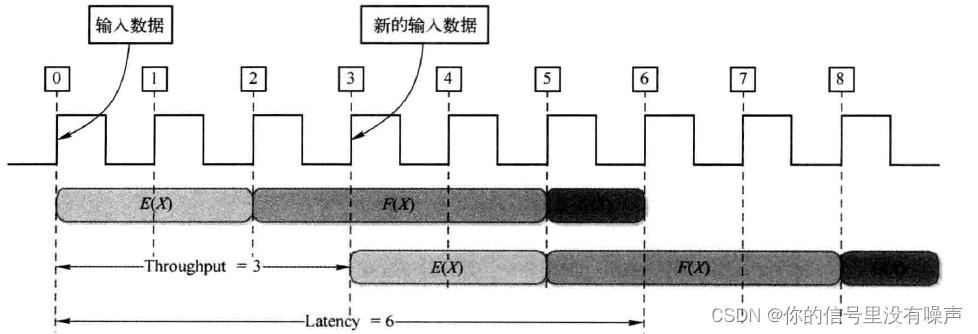

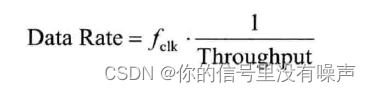

三、2.3FPGA设计性能描述指标

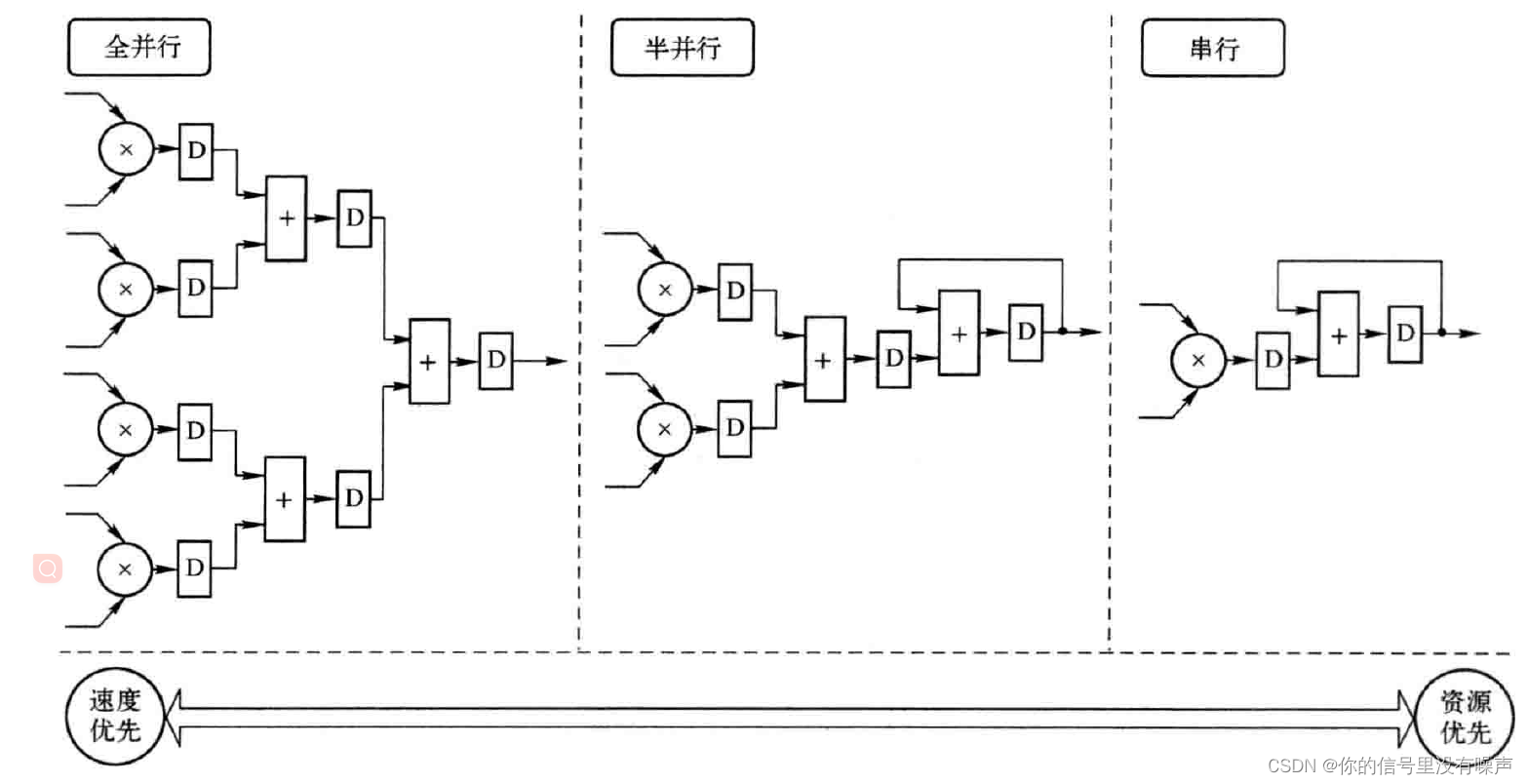

流水线是 FPGA设计中很常用的一种提高系统时钟频率的方法:流水寄存器(本质为 D触发器)

2.4 FPGA设计中的数据格式

一般S位的0表示正数,“1”表示负数。

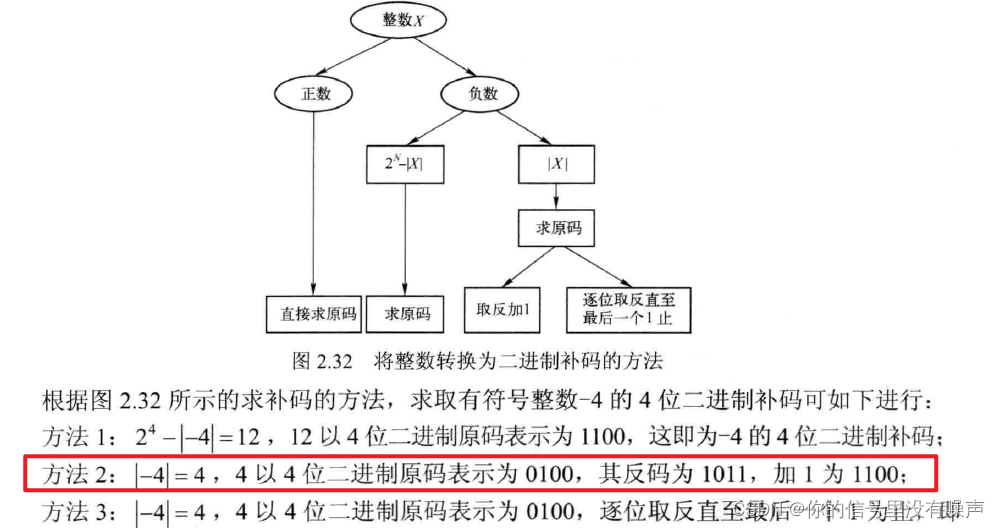

1.第一类定点数:整数

N 位二进制数所能表示的无符号整数范围是[0,2"-1],所能表示的有符号整数范围是[-2N-1,2N-1 -1]。

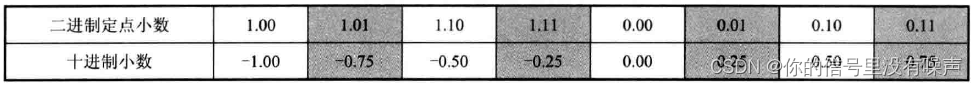

2、定点数:

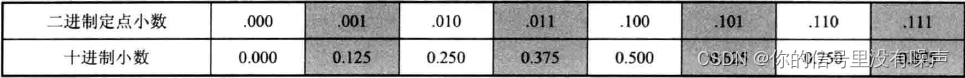

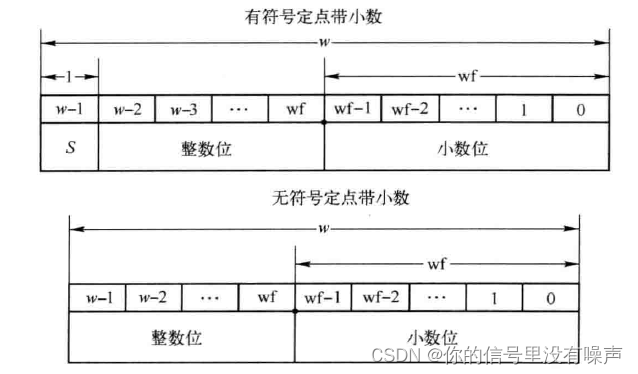

3.定点带小数:

2.5xilinx开发工具对浮点数与定点数的支持

- 该IP 既可在 Vivado IP Catalog 中调用,也可在SysGen中以模块化的方式调用。

- 在 SysGen 中,有符号定点数以 Fix_w_wf 来显示,无符号定点数以 UFix_w_wf 来显示。其中 w为字长,wf 为小数部分字长。

总结

system generator相当于IP核一样帮助开发者实现算法验证和开发。

5320

5320

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?