一、Flash ADC

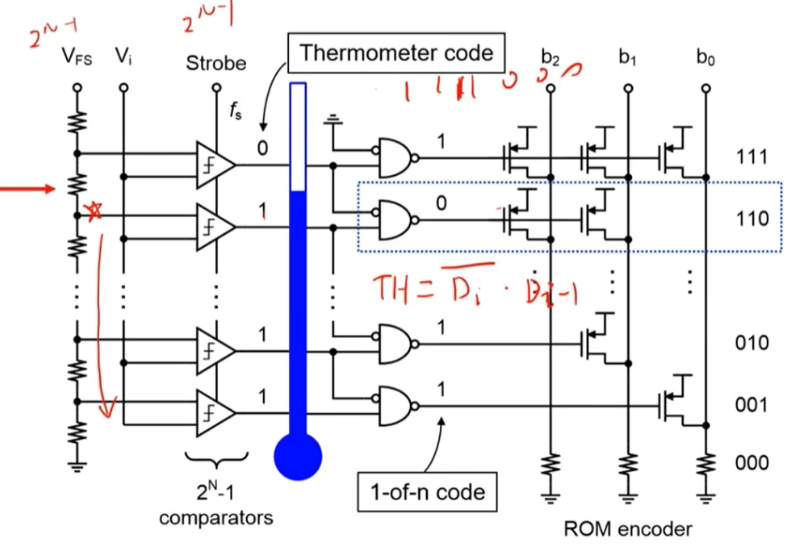

Flash ADC 一般包括,Reference、Resistor、Input_SHA、Comparators、Encoder。

特点:简单、高速 || 复杂

注意:做高精度应用的时候,去偶电容一定要加够,因为对于一般的bonding wire,有寄生引线电感,电感的特性:△V = L* di / dt 。电感上电压的变化是和电流的slew rate 成正比,即使电流很小,只要斜率够大,就很容易在电感上产生一个较大的电压。因此decouple电容一定要加够。

Flash ADC Challenges:

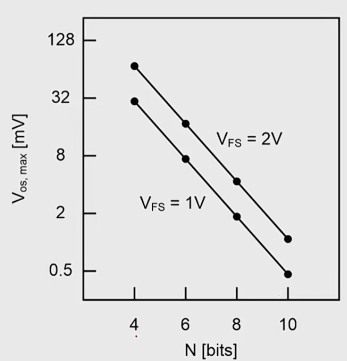

在对于高精度的Flsh,例如10-bit-flsh-adc,下图计算可以看出来,Vos < 0.5*LSB,至少保证3σ的良率,要求这就要求 Vos 的 σ 值在0.1~0.2mV之间,这基本是不可能实现的。一般一个比较器的Vos 1σ在2~3mV量级,对应的 3σ 都在10mV左右了,远远超过需要的 0.5LSB。(除非加Auto zero & chopping)。同时还要求比较器非常多,功耗非常大。

右下图,表示的是:既然Vos <0.5LSB,那么吧 V_FS放大一点,对比较器的要求就低了。

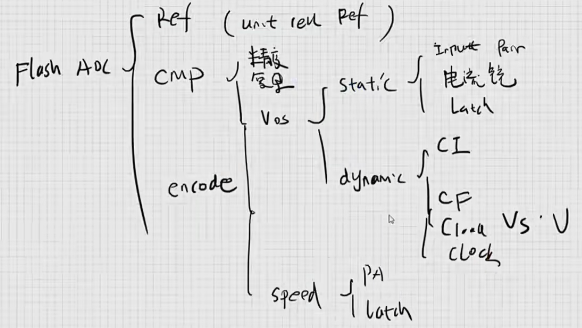

比较器 V_offset 的来源:

静态:①输入对管的失配;②Pmos负载和电流镜的失配;③Latch管的失配

动态:①M9对两边 CF&CI 的不匹配;②C_load的不匹配(eg:MOS的寄生电容随电压而变化的);

解决:静态 -- 做好match;动态 -- 全差分,dummy等。

比较器的offset:对于sar、pipline、redundant cyclic等ADC来说,Vos并不影响ADC动态性能,当然对于像仪器仪表中要求绝对精度高的应用也需要关注。相对来说,flash ADC 对于比较器的Vos更加敏感。Flash做不了高精度的其中一个原因就是受限于 Comp_Vos 。(另一方面受限于复杂度)。

Latch Regeneration

reset 阶段:M9将Vo-&+ 拉倒中间电平,此时pre-amp在工作,输入信号经pre-amp放大后track到Vo-&+ 并进行 track-hold ,所以说flash的比较器自带一个T/H电路,不用另做采样保持电路。

regeneration 阶段:Latch M7&8通过正反馈将Vo+&-拉倒rail-to-rail logic level。

Regeneration Speed

亚稳态问题(所有comp都要考虑亚稳态):主要和比较器的速度有关,和信号的大小有关。

解决:加pre-amp。

PS:亚稳态问题是在有限的比较时间之内,比较器输出信号没有建立完成(到需要的精度)。

为什么说加了pre-amp能提高比较器速度呢?

上上张图中,Latch的放大能力和输入信号的幅值有关,虽然说无论输入的信号是多大,最终都能将其放大至rail-to-rail,但是Vin越小,其放大速度越慢。而pre-amp的增益和输入幅值无关,在有效的带宽内,能够将小信号迅速放大(放大倍数有限,到不了rail-to-rail),然后latch接收到的是放大后的信号,就能大大加快速度,(想想时域响应那张图)。

上图展示了亚稳态和哪些因素有关,前面的文章也有讲过,这里不赘述了,翻阅前文。

在Flash中,亚稳态尤其需要注意。因为:Flash是通过 过零检测 来将 温度计码 转成 二进制编码,出现亚稳态之后,有多个过零点,导致后面的编码出现重大错误。可能会跳好多个LSB,导致DNL&INL非常差。

CF & CI in Latch

通过M9_CF&CI 引入一个Vos,在这个电路里面,Vos是叠加在Vin上面的,当Vin特别小,Vos超过Vin时,latch会将这个错误的信号PFB-rail-to-rail,尤其是如果Vos和Vin是反相的,很严重。 所以做的过程一定要关注 CF&CI 。

右上图:Dynamic offset 来源:就剩一个Clock routing没讲,说一下什么是clock routing。

Flash需要一堆latch,需要clock驱动,clock到每个latch的时间不同,导致每个latch开始比较的时间不同(M9断开的时间不同),导致offset & 非线性。

比较器中总的Offset。

理论上来讲,只要pre-amp的增益(Av1)足够高,就可以将Vos消除大部分。

提高pre-amp的方法:①负载加 I_load,改变电流分配。②加交叉耦合管cross-couple。

对于电流镜来说,希望过驱动电压越高越好。因为:失配的主要来源是阈值电压Vth,过驱动电压越高,Vth的失配带来的影响占比就越小。

快速估算Offset、mismatch的表格:

电流镜的匹配仅靠改变W是改善不了的,主要取决于L。

为什么大尺寸器件匹配更好?(用面积换取精度)误差是开平方相加,阻值是线性相加。

但是为什么Flash不能用面积换取精度,因为需要的面积太大了,输入寄生电容太大了。

右上图,6-bit-flash,一系列计算可以看出来 Cin = 3.9pF,还可以接受。但是8-bit-250pF就很难接受了。

Flash中其他的Offset:

主要来源:比较器、时钟、输入信号。

没有SHA的,SH功能在比较器里面实现,自然对Clock敏感,如果Clock有误差,每个比较器采样的输入信号都不是一个,后面就更不用看了。还有就是输入信号线的分布式RC延迟,输入信号到达每个比较器的时间不一样。

后面对Clock造成的误差讲一下。

Pre-amp的带宽(速度)不一样可能会导致误差。主要是由于共模电平的不一样导致的误差。(由于flash 的reference是一级一级递减的,每个比较器的CM自然是不一样的)。

解决共模电平问题的方法:①全差分;②用隔离电容,隔离直流信号。(还可以auto-zero)

上图一个是输入电容随输入信号变化的非线性。一个是输入信号大的跳变会通过M1&2耦合到干净的Reference上,同时Input是个低阻节点,能够很快跟随上下次信号,而Reference是个高阻节点,其电压改变需要一定的时间,可能导致下一次比较时,reference还没回到理想的情况。

解决方法:全差分;AC-Coupled Pre-amp;

encoding:Bobbles

(Flash到此结束,后续整理。思维导图需重新整理)

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?