版图设计目标:

面积小,性能好(少恶化),成本低

设计规则规定了同层与不同层之间的最小距离,因此限制了最小面积

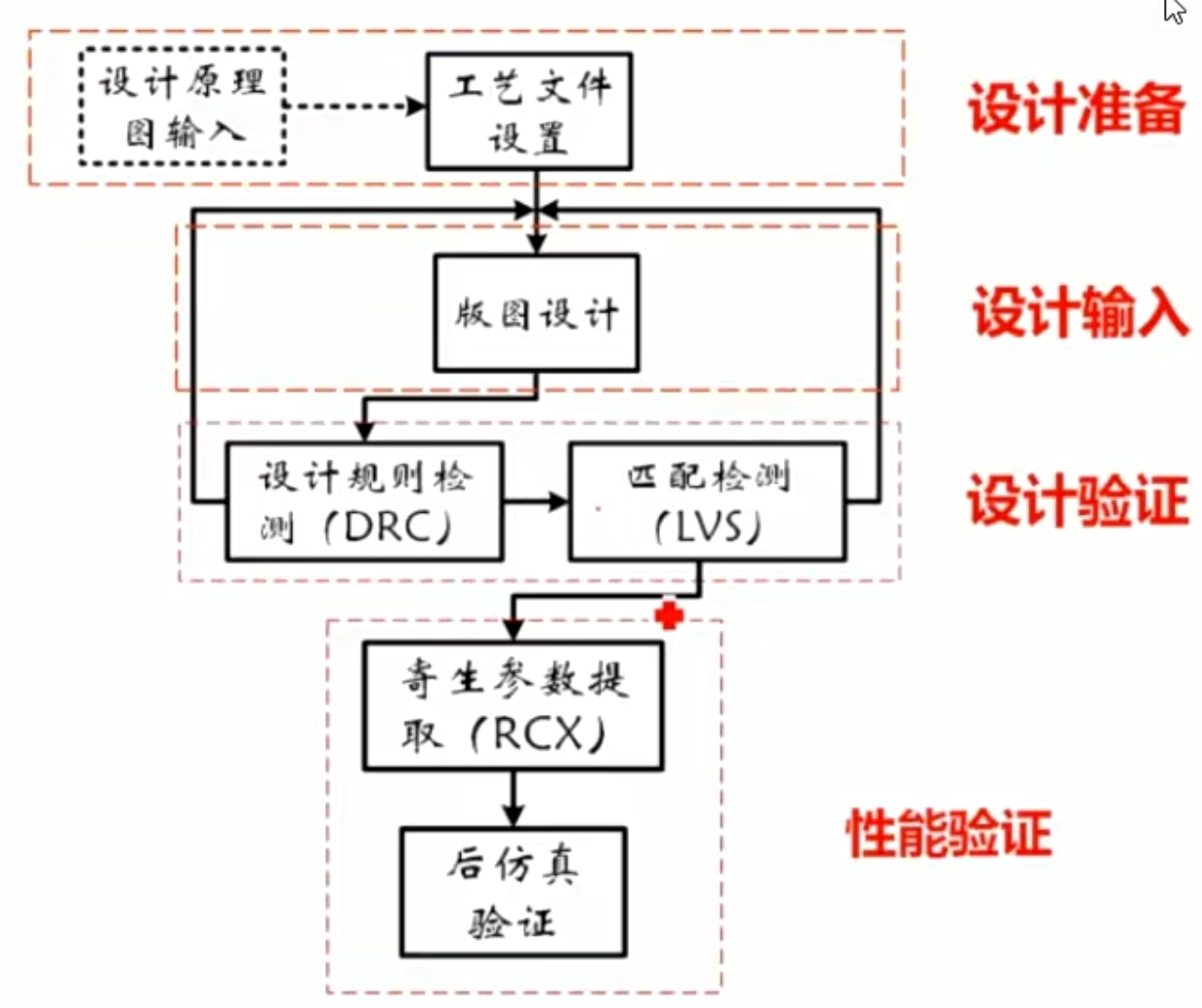

模拟版图设计流程

第一步:设计原理图输入

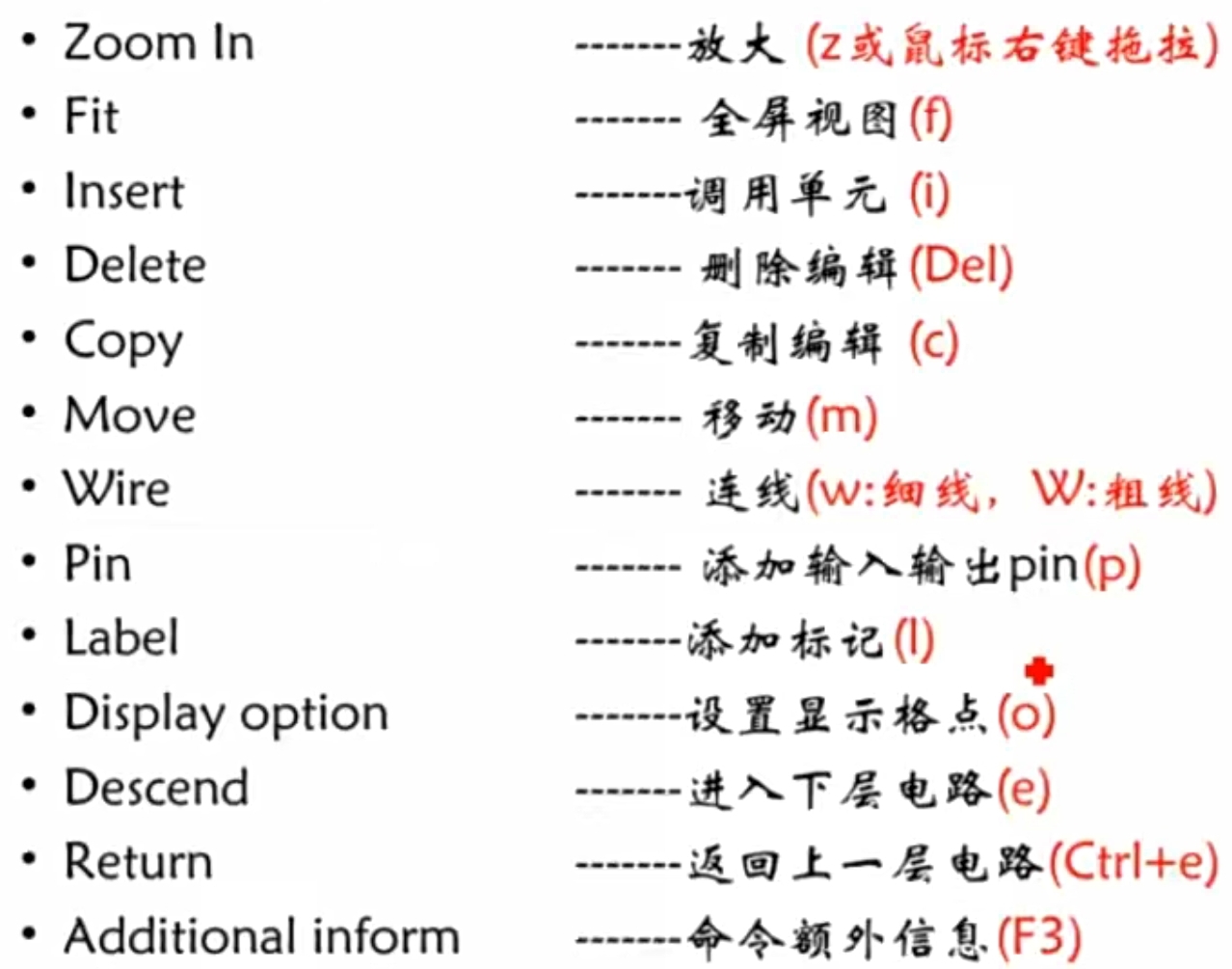

常用快捷键如下:

介绍一下pin:input & output & inputoutput,起到只是标识作用,像如果后面生成symbol后input和output接错了软件会报错,方便设计作用。为什么电源和地用inputoutput,因为可能是流入电流也可能是抽取电流。全局pin:gnd! , vdd! 。

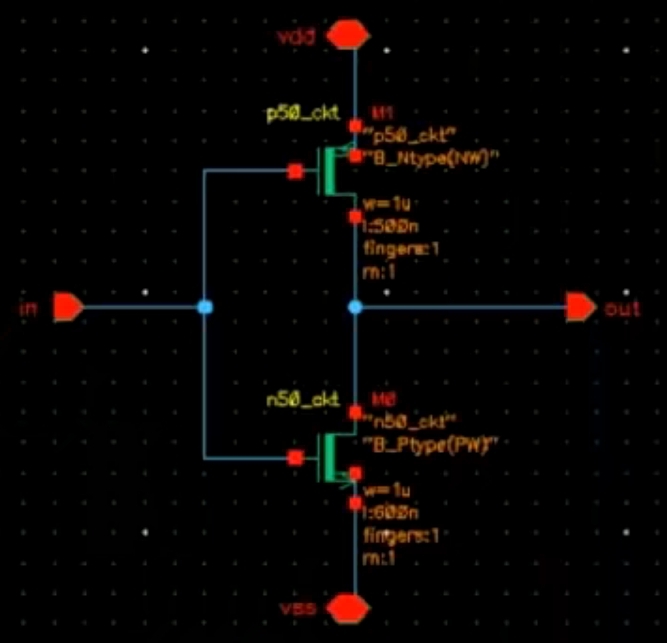

原理图输入不赘述了,不会的也没必要看这文章了。

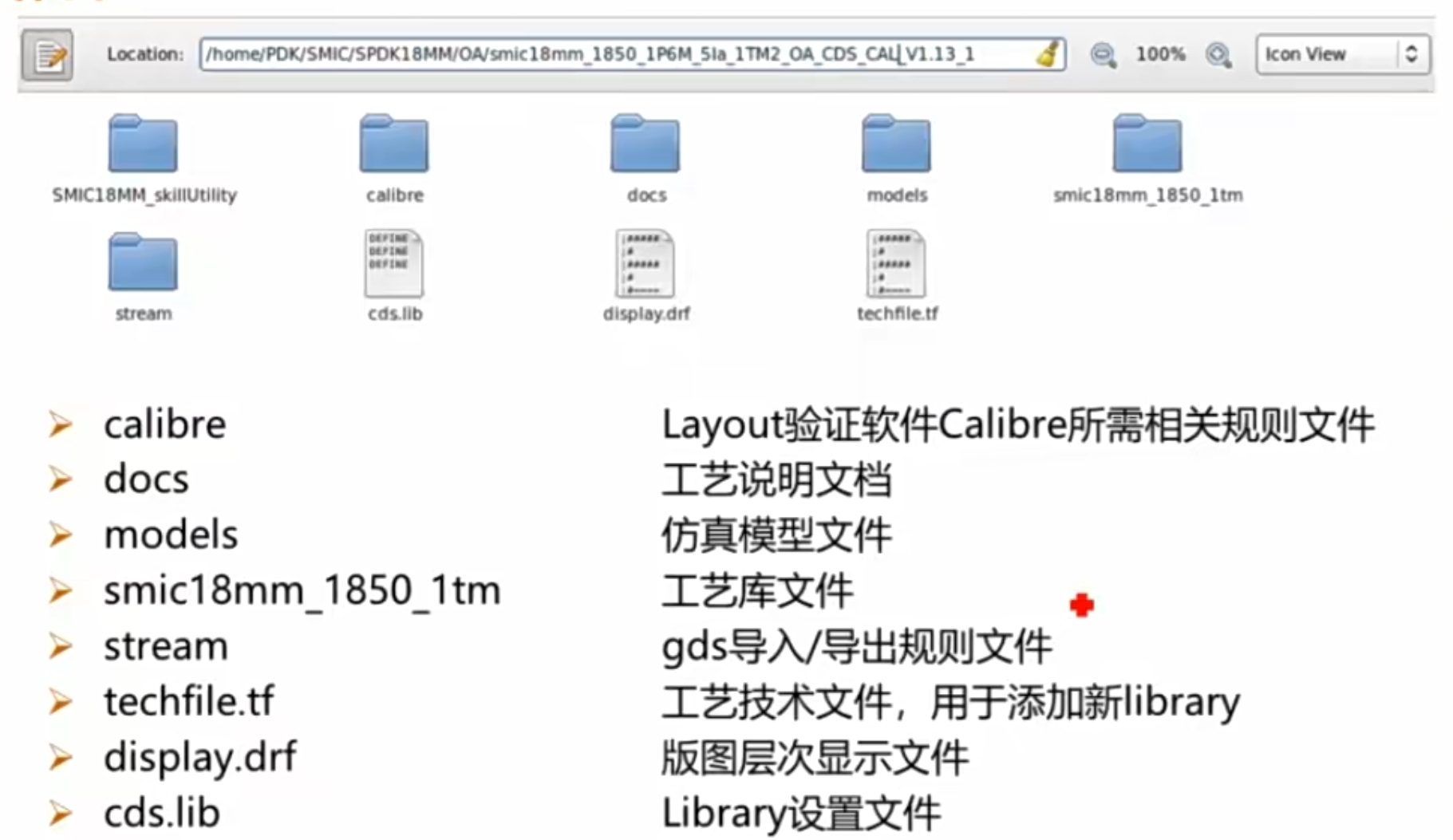

第二步:工艺文件设置

工艺文件不赘述了,都应该懂的。尤其是cds.lib , display.drf , techfil.tf 这些文件,还有models里面的各种文件。docs里的内容有用的(都是英文的)。

第三步:版图设计

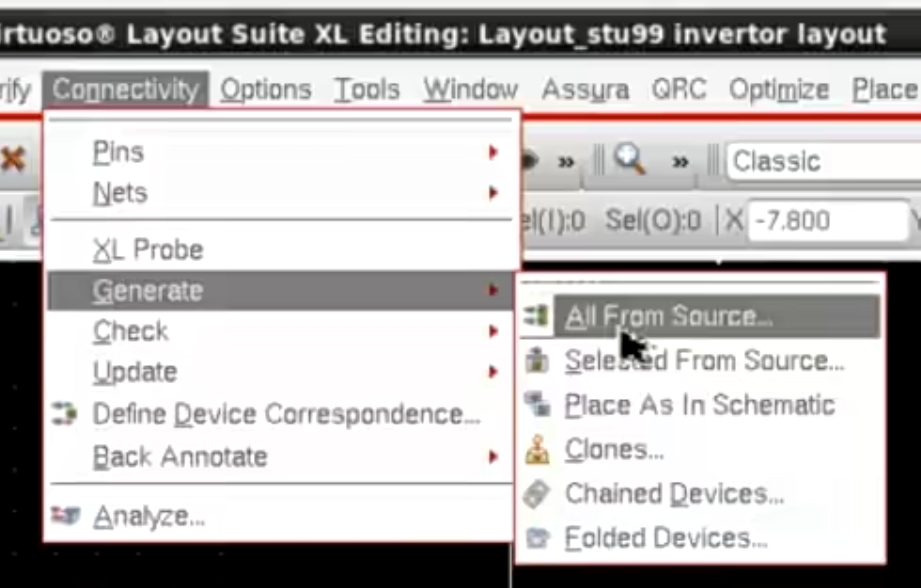

新手进入版图一定在Schematic窗口--Launch--Layout XL ,这样layout和schematic对应起来!切记!切记!从Schematic中创建版图,一定要如图操作:Connectivity--Generate--All & Selected From Source 。

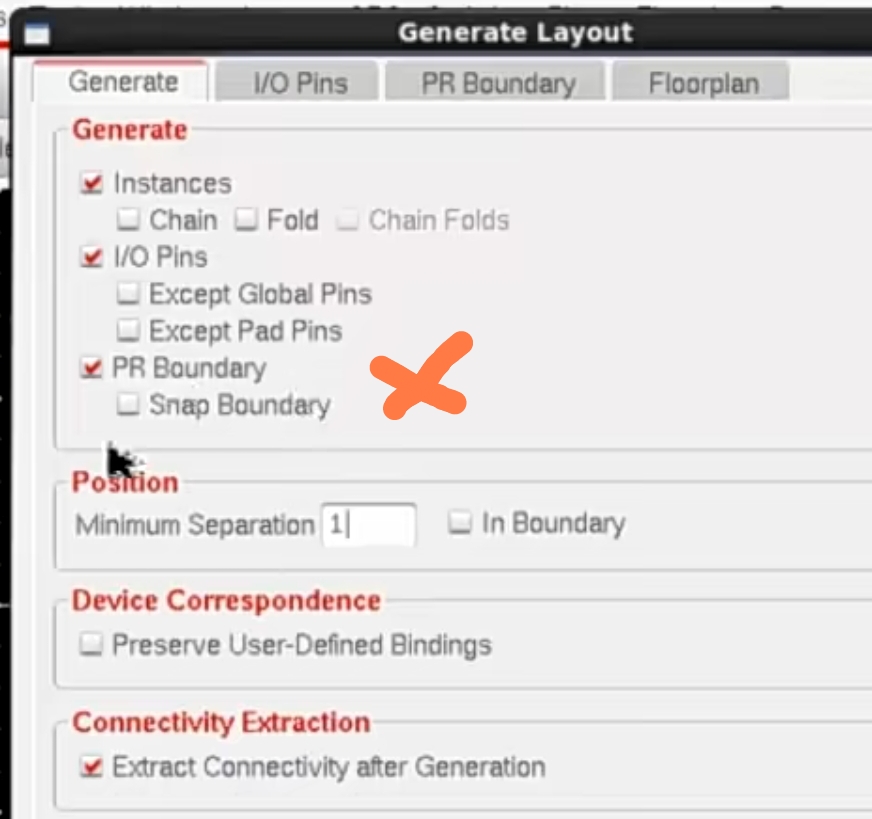

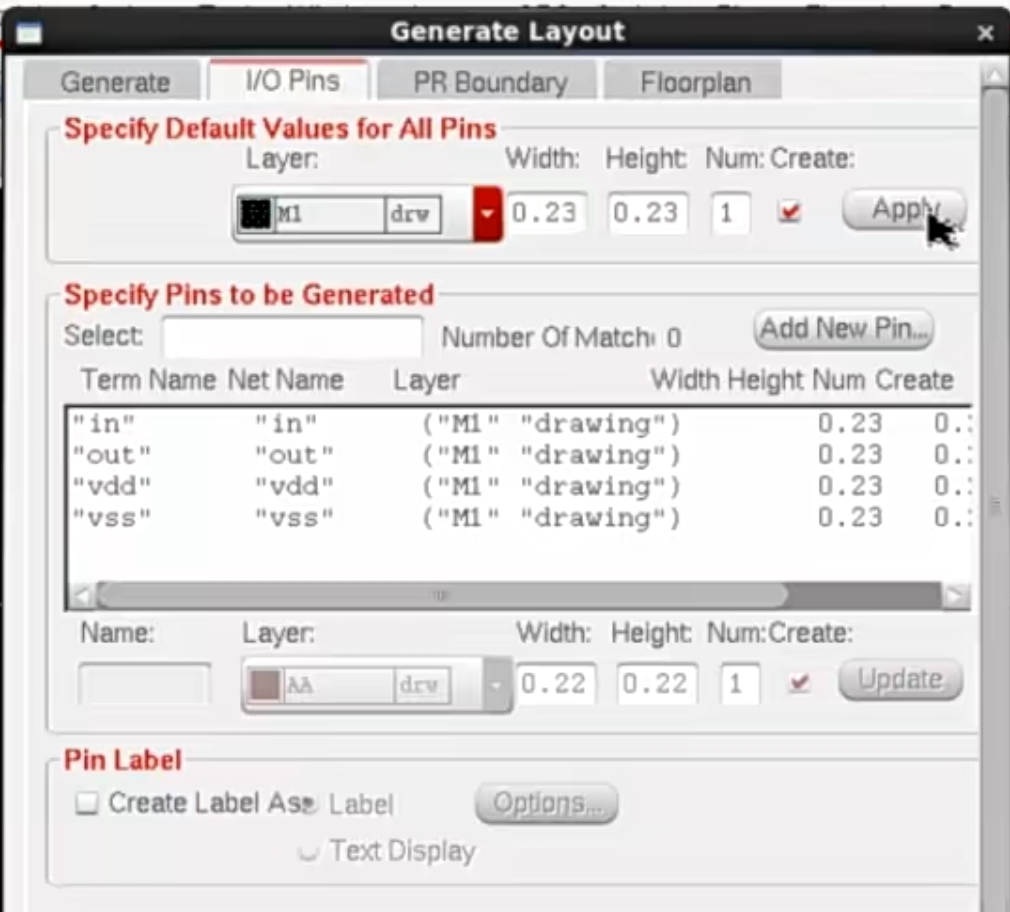

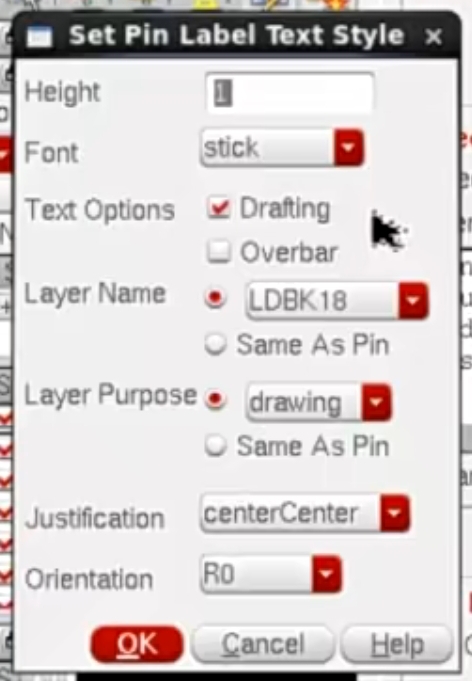

点击后出现Generate Layout设置,一般I/O Pins点上,PR Boundary取消勾选。然后IO Pins界面选好IO layer,勾上Pin Label,点击option,设置IO Pins Label,包括大小啥的,其他就选Same As Pin即可。PR Boundary和Floorplan用不到。

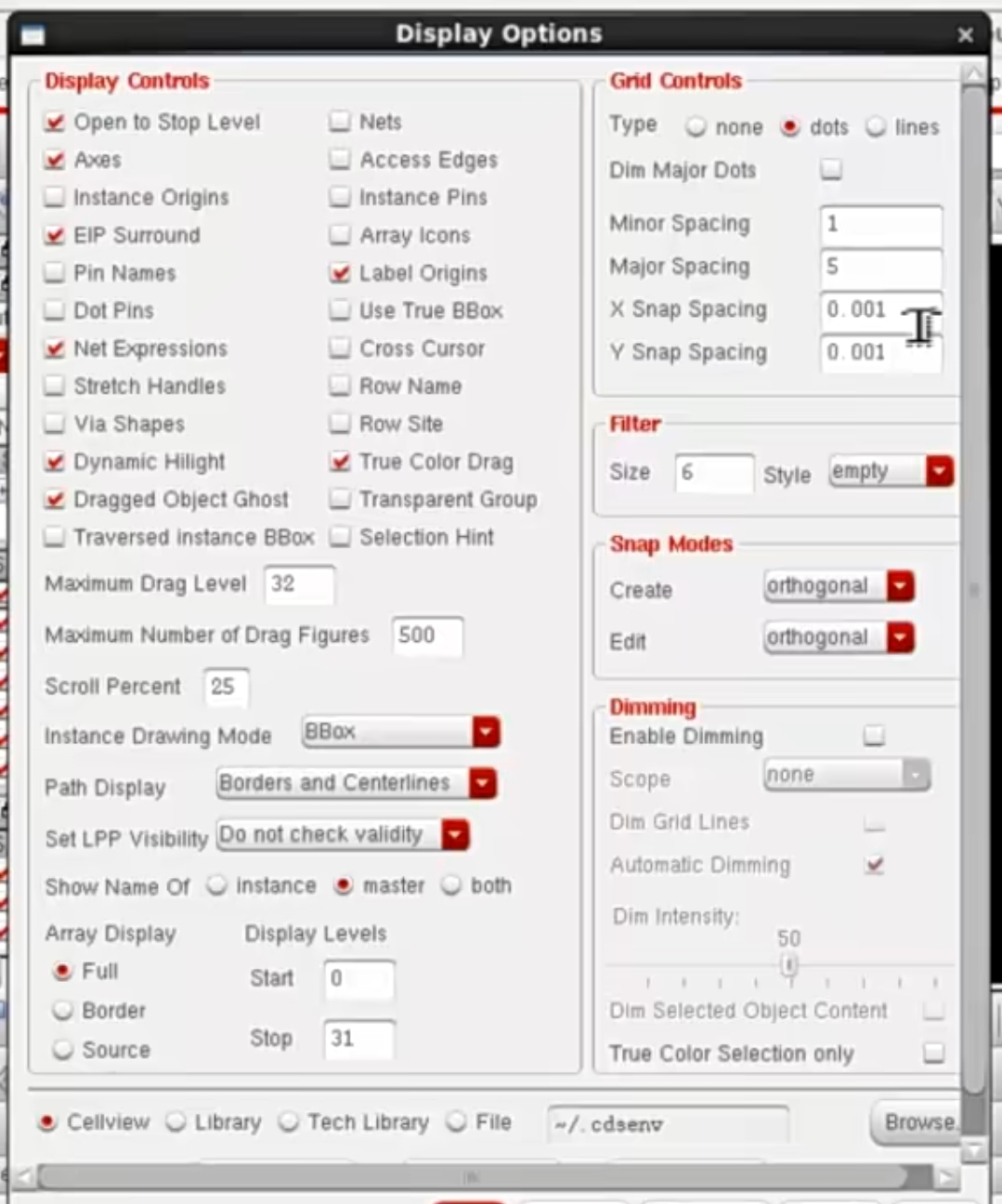

创建完成版图之后,要设置格点大小(这个每个pdk可能要求不一样)快捷键e。180nm工艺一般0.001或者0.0005就好。

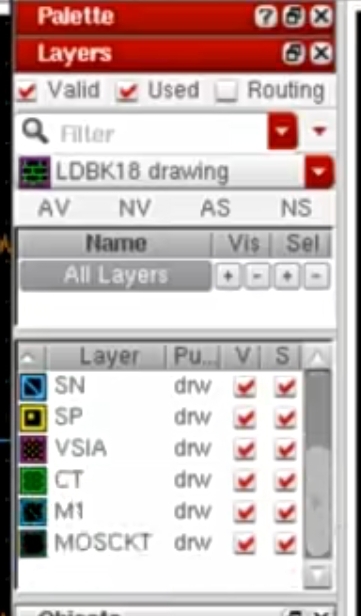

Layers开启Used这样能够更方便的画图,V(View) , S(Select),AV:All Viewed,NV:None Viewed,AS:All Selected,NS:None Selected。

小技巧:

快速选择要画的layers,鼠标放在需要连接的的地方,按快捷键t,会自动调到所在layer。

切断path快捷键:shift+s;部分移动path快捷键:ctrl+s,然后上划或者下划。

一般不会改变单位via的大小,想扩大通孔就行列多设置几个。

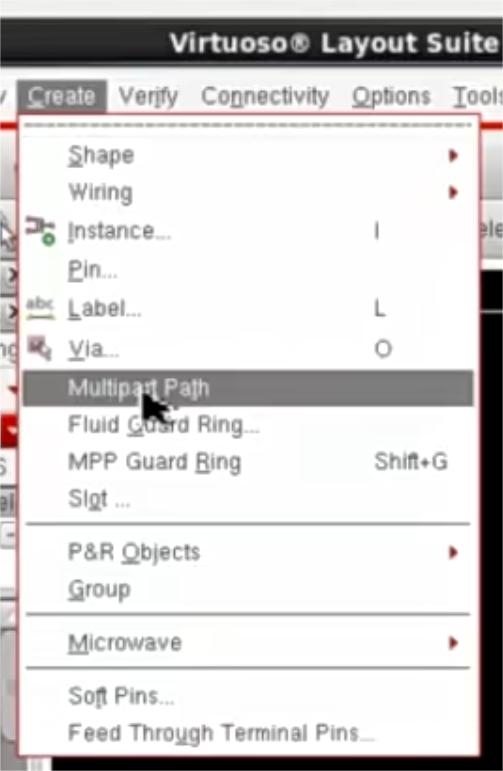

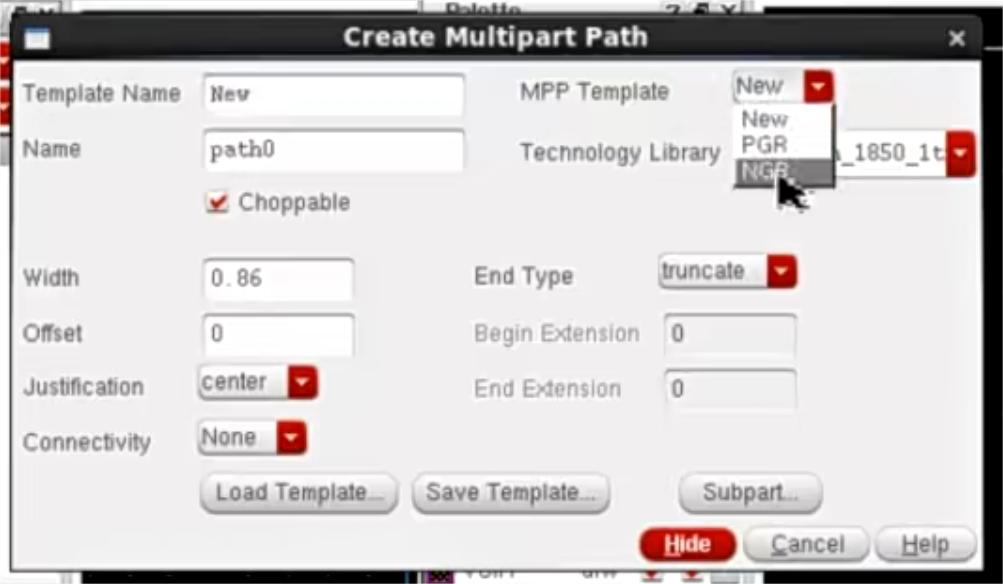

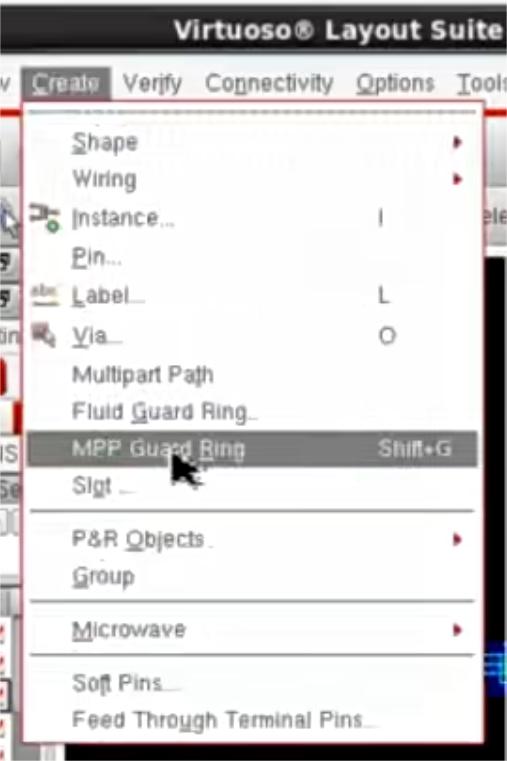

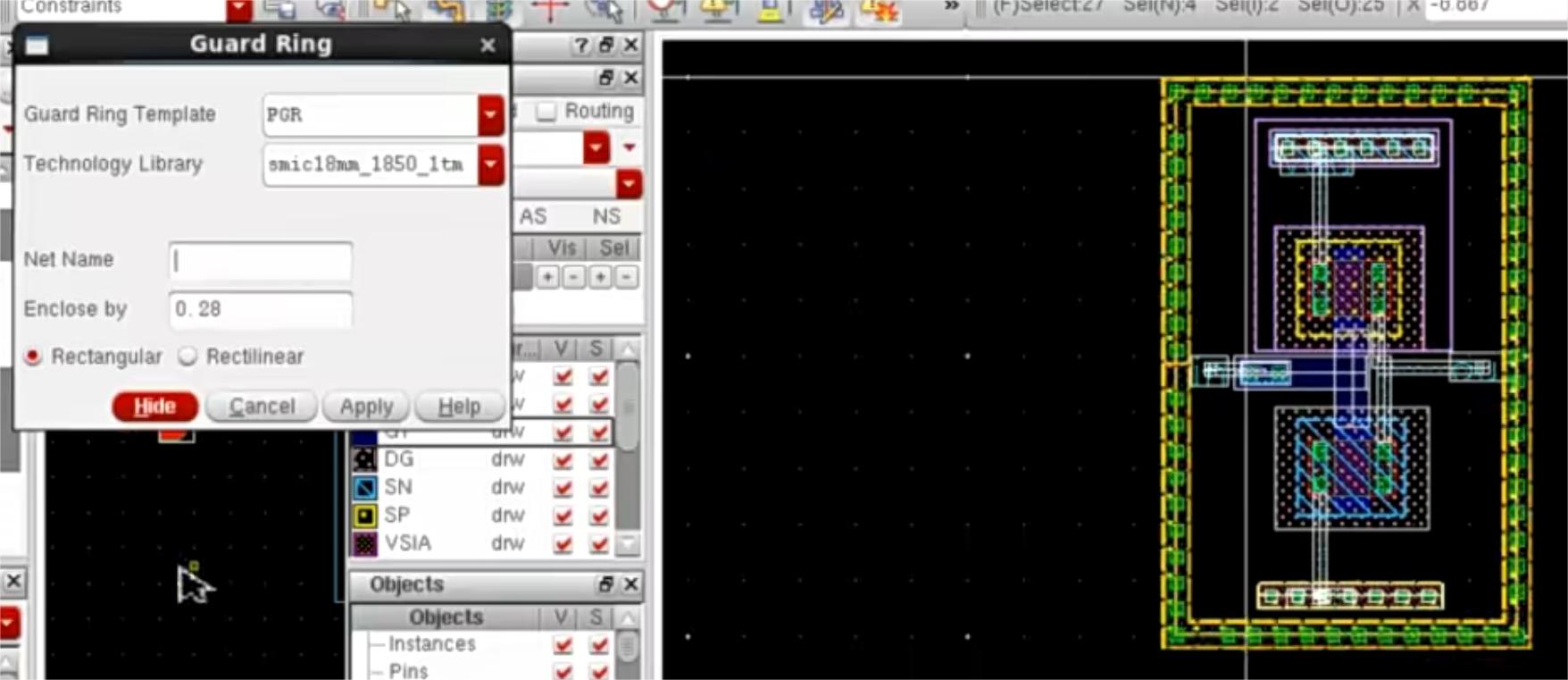

Guard Ring的画法——Multipart Path用法

点击选中Multipart Path之后按F3,这里有做好的单排NGR和PGR。直接画就可以,点Subpart可以具体设置。能设置好之后Save和Load。如图Guard Ring画法,快捷键shift+g。这里面的enclose by是可以设置GR和器件的距离的。

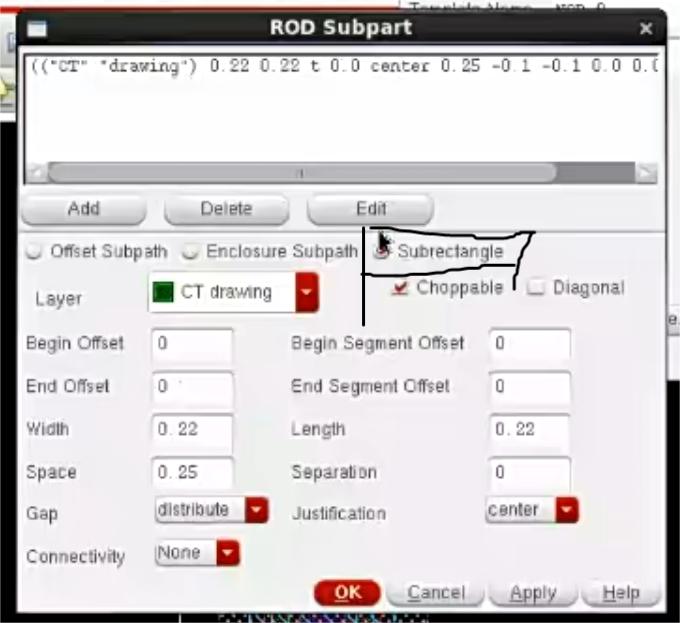

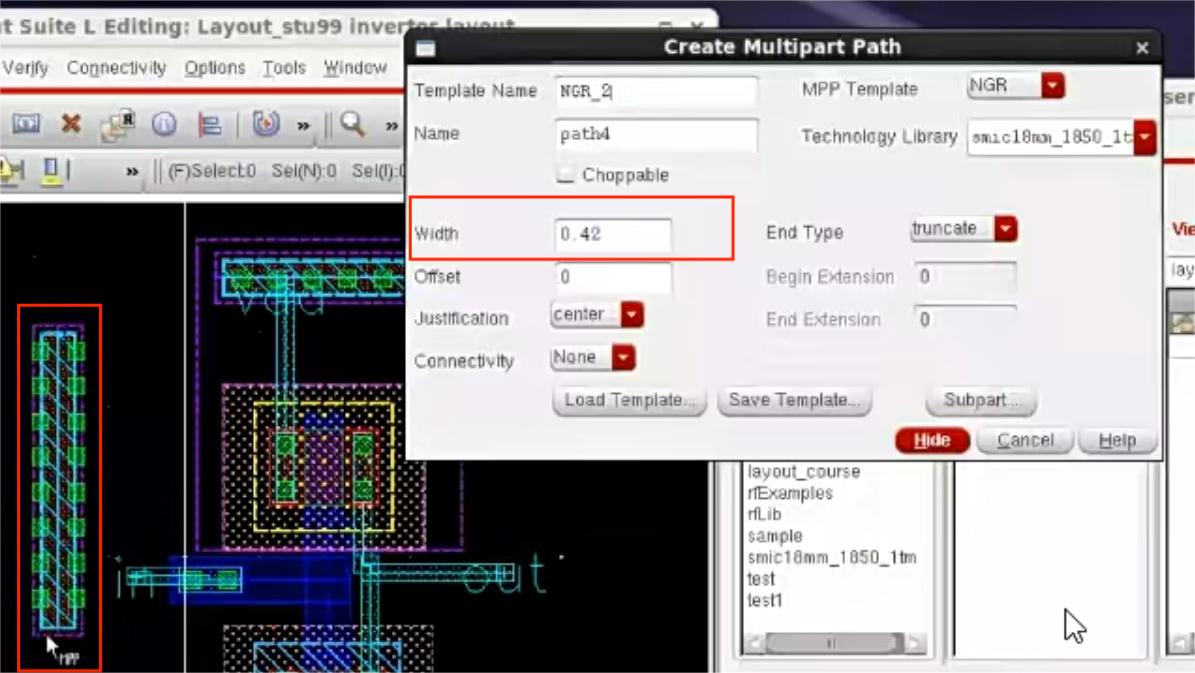

画多排Guard Ring的方法:选中Multipart Path之后按F3,起个名字如NGR_2,点Subpart。然后设置Separation(间距可以+ -)--Add,就可以设置多行了,然后还要改一下GuardRing的Width。Save以后还可以Load。

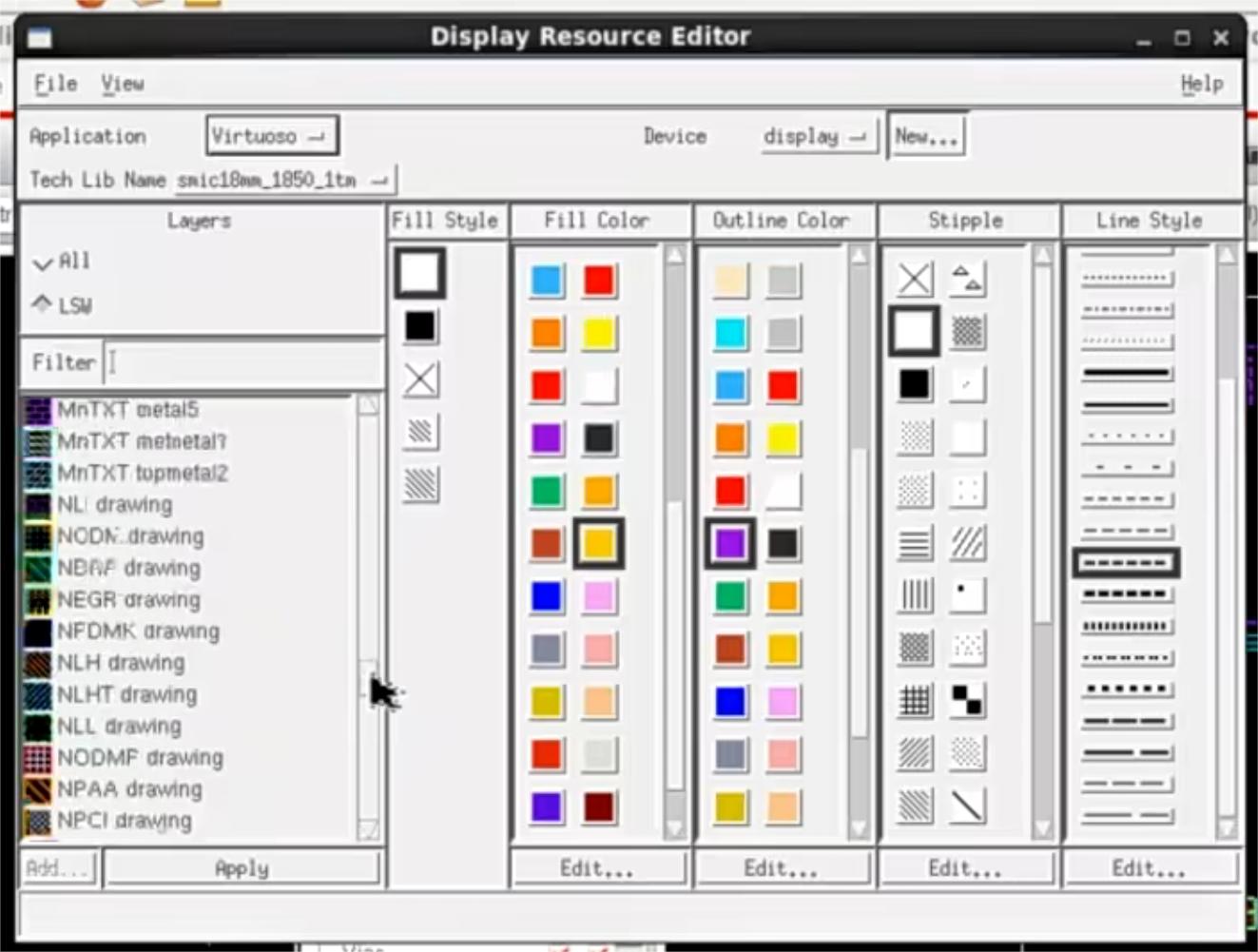

更改Display:shift+右键点击要更改的layer,可以File--Save和Load,就是display.drf 文件。

第四步:DRC验证

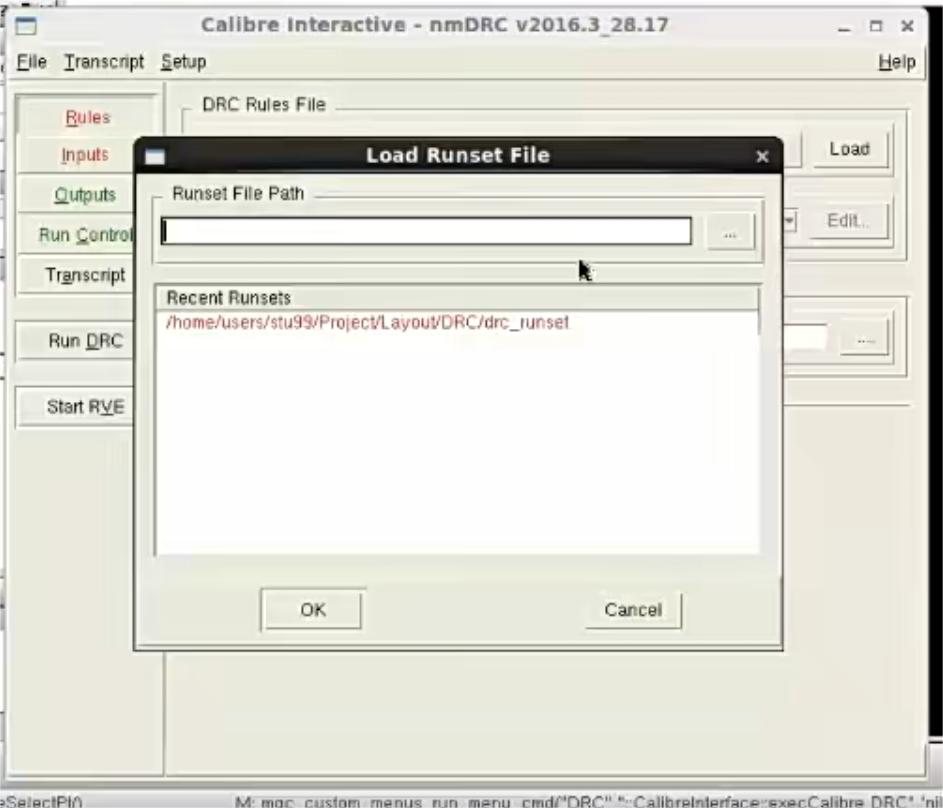

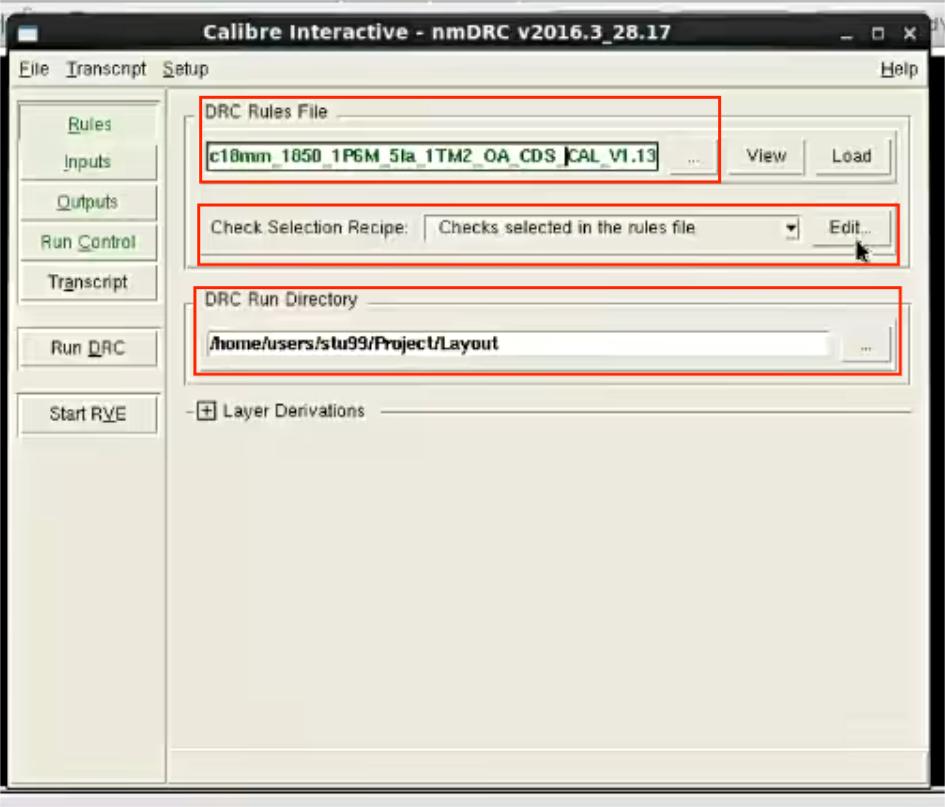

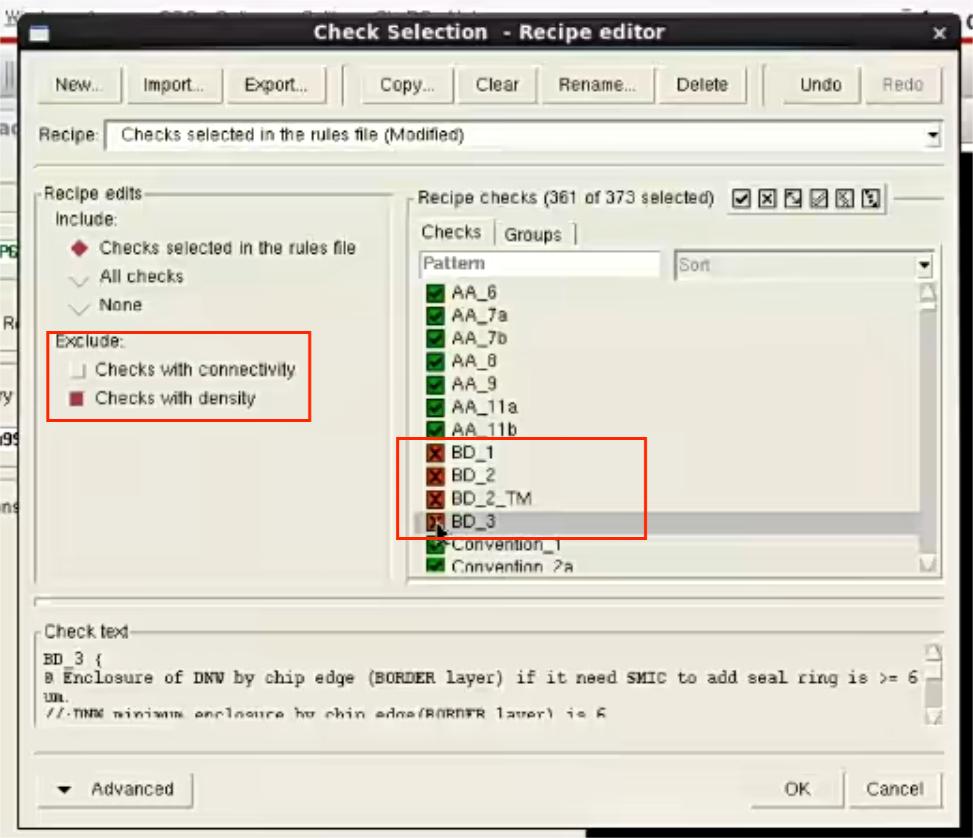

Layout界面上方,Calibre--Run DRC。一开始并没有Runset File,点取消就行。首先导入DRC Rules Files,这在pdk里面有。DRC中有些option要修改的,这check那边点击Edit。不check density,也不check BD(Boundary)。还有DRC的Run Directory最好新建一个文件夹放,DRC过程中会生成很多杂七杂八文件。

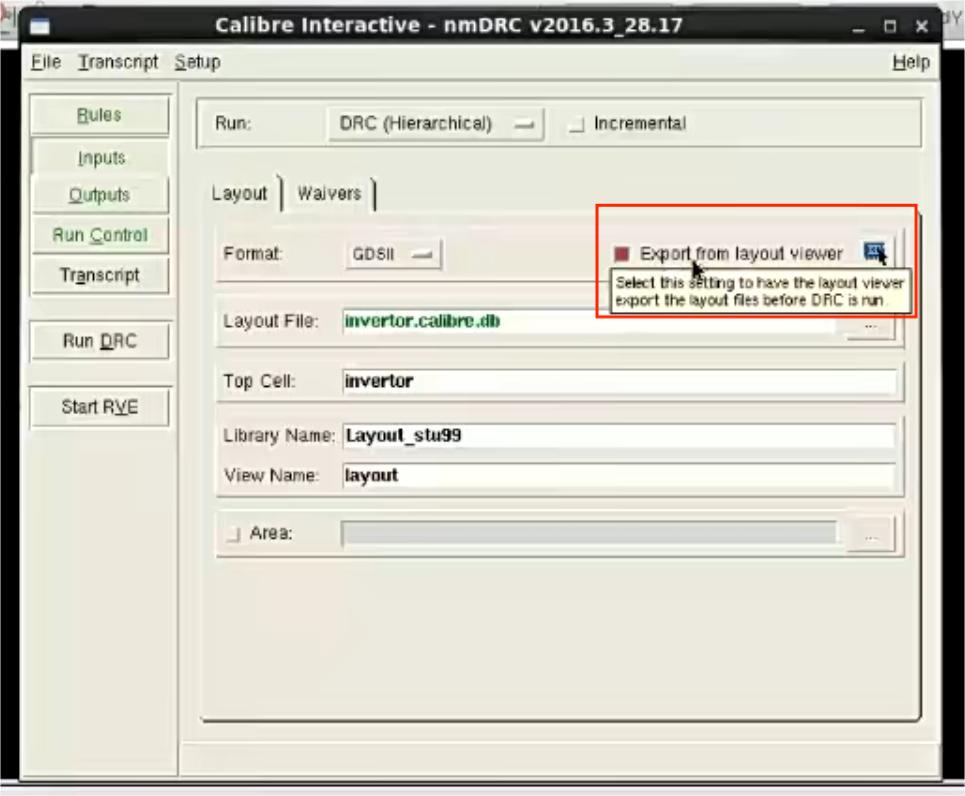

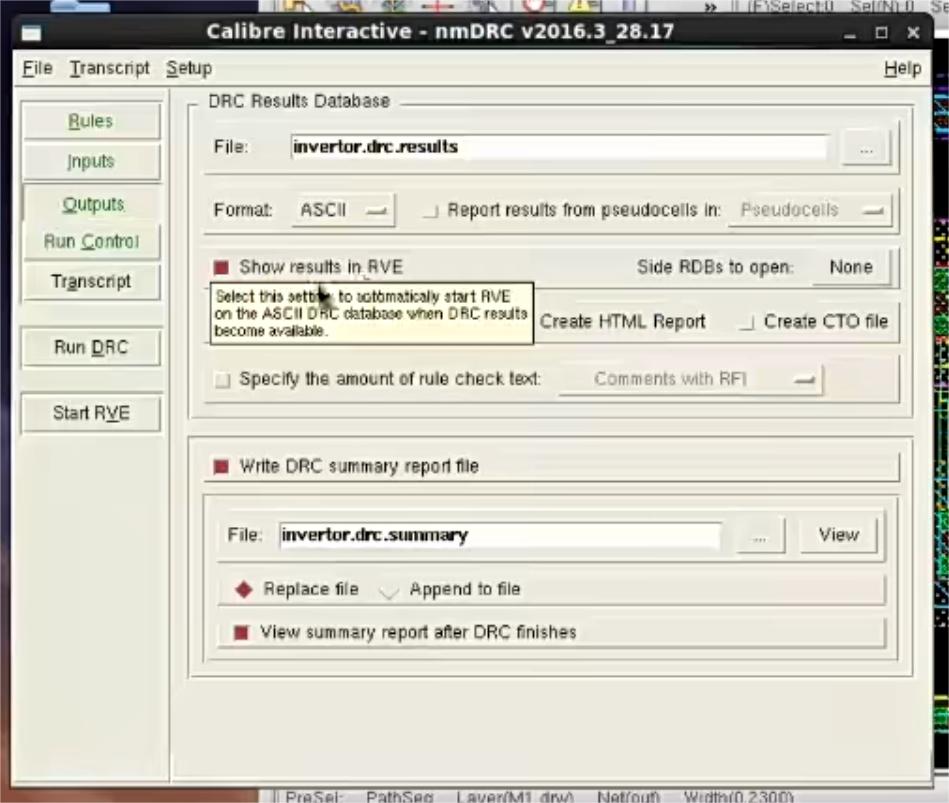

介绍一个几个选项:Inputs中:勾选Export from layout viewer即可,特殊情况才从别的地方load layout file。Outputs中:就是Show results in RVE(图形化界面)。没有其他的了,直接Run!

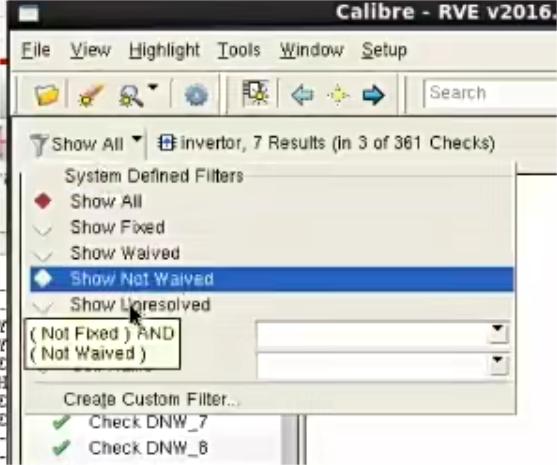

RVE界面Show Not Walved,然后改错即可,没什么好说的。金属密度不用改,Top Level再改。

1625

1625

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?