FIFO 的英文全称是

First In First Out,即先进先出。FPGA 使用的 FIFO 一般指的是对数据的存储具有先进先出特性的一个缓存器,常被用于数据的缓存,或者高速异步数据的交互也即所谓的跨时钟域信号传递。 它与 FPGA 内部的 RAM 和 ROM 的区别是没有外部读写地址线,采取顺序写入数据,顺序读出数据的方式, 使用起来简单方便,由此带来的缺点就是不能像 RAM 和 ROM 那样可以由地址线决定读取或写入某个指定 的地址。本章我们将对 Vivado 软件生成的 FIFO IP 核进行读写测试,来向大家介绍 Xilinx FIFO IP 核的使用方法。

1.ip核简介

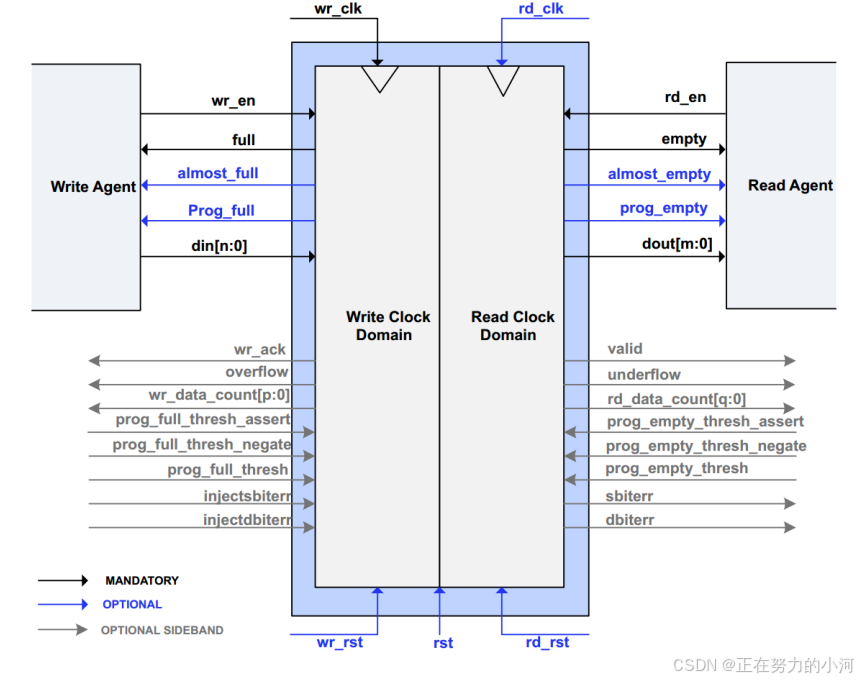

根据 FIFO

工作的时钟域,可以将

FIFO

分为同步

FIFO

和异步

FIFO

。同步

FIFO

是指读时钟和写时钟为同一个时钟,在时钟沿来临时同时发生读写操作。异步 FIFO

是指读写时钟不一致,读写时钟是互相独立的。Xilinx

的

FIFO IP

核可以被配置为同步

FIFO

或异步

FIFO

,其信号框图如下图所示。从图中可以了解到,当被配置为同步 FIFO

时,只使用

wr_clk,

所有的输入输出信号都同步于

wr_clk

信号。而当被配置为异步

FIFO 时,写端口和读端口分别有独立的时钟,所有与写相关的信号都是同步于写时钟 wr_clk

,所有与读相关的 信号都是同步于读时钟 rd_clk

。

对于 FIFO

需要了解一些常见参数:

FIFO 的宽度:

FIFO

一次读写操作的数据位

N

。

FIFO 的深度:

FIFO

可以存储多少个宽度为

N

位的数据。

将空标志:almost_empty

。

FIFO

即将被读空。

空标志:empty

。

FIFO

已空时由

FIFO

的状态电路送出的一个信号,以阻止

FIFO

的读操作继续从

FIFO中读出数据而造成无效数据的读出。

将满标志:almost_full

。

FIFO

即将被写满。

满标志:full

。

FIFO

已满或将要写满时由

FIFO

的状态电路送出的一个信号,以阻止

FIFO

的写操作继续向 FIFO

中写数据而造成溢出。

读时钟:读 FIFO

时所遵循的时钟,在每个时钟的上升沿触发。

写时钟:写 FIFO

时所遵循的时钟,在每个时钟的上升沿触发。

这里请注意,“almost_empty”

和

“almost_full”

这两个信号分别被看作

“empty”

和

“full”

的警告信号,他们相 对于真正的空(empty

)和满(

full

)都会提前一个时钟周期拉高。

对于 FIFO

的基本知识先了解这些就足够了,可能有人会好奇为什么会有同步

FIFO

和异步

FIFO

,它们各自的用途是什么。之所以有同步 FIFO

和异步

FIFO

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9402

9402

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?