前言

跨时钟域的内容很多,这一篇先学习一下基础概念,建立时间和保持时间

一、建立时间和保持时间?

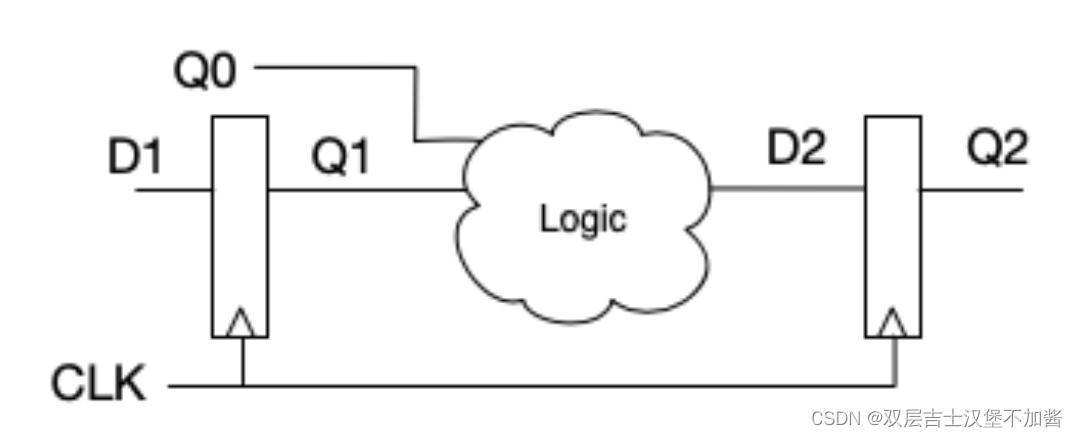

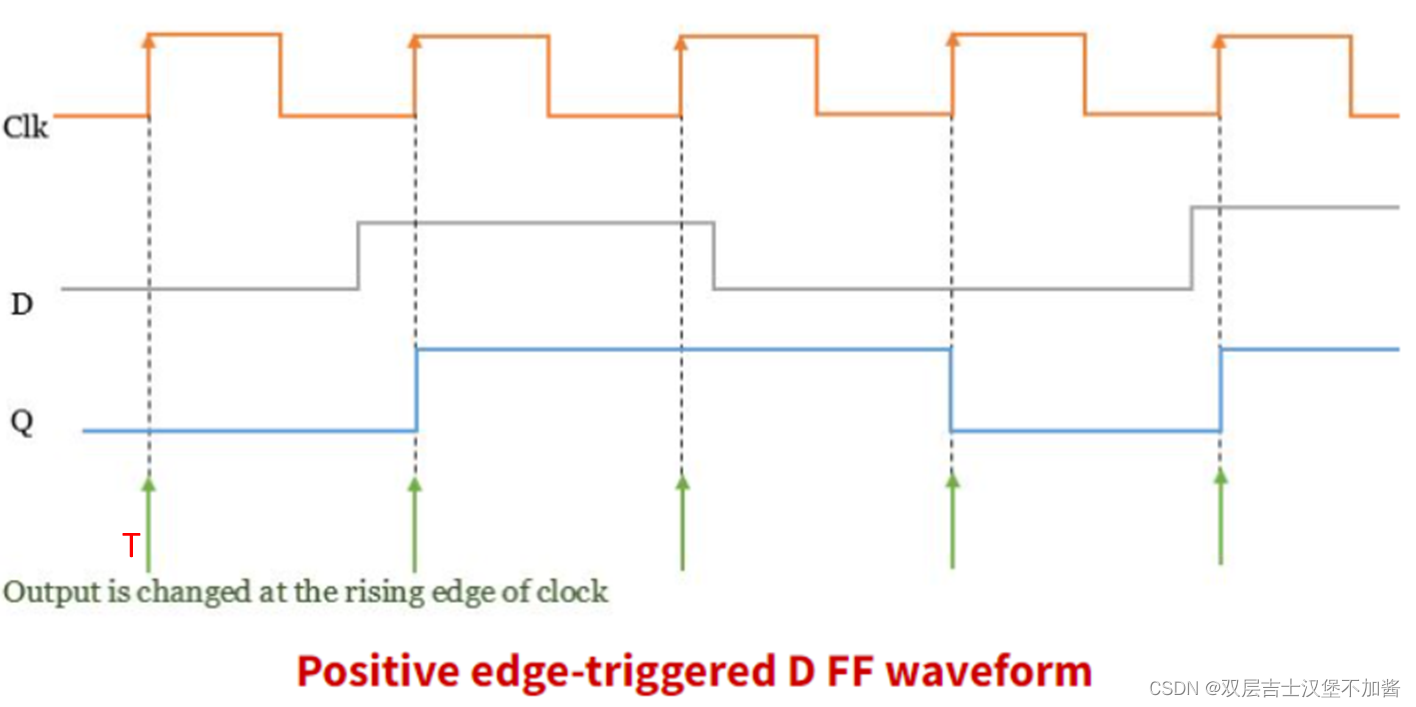

建立时间和保持时间都是对于一个触发器来讲的,

建立时间(setup time) :时钟沿到来前输入信号D1必须保持的最小时间

保持时间(hold time):时钟沿到来之后输入信号D1必须保持稳定的最小时间

clk to q time :建立时间和保持时间满足要求之后,从时钟沿到来时刻到输出Q1变化至稳定的时间。

如果建立时间或者保持时间不满足要求,或者是Q1输出端的信号在 ck to q的时间之后才保持稳定的话,我们就说这个触发器发生了亚稳态(meta stability)

重点来了:

建立时间和保持时间,还有亚稳态的定义都很直白,但是为什么需要建立时间还有保持时间呢?

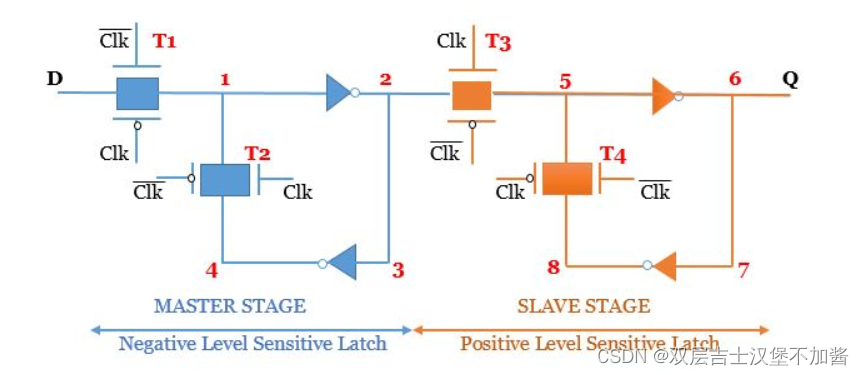

触发器原理图如下:

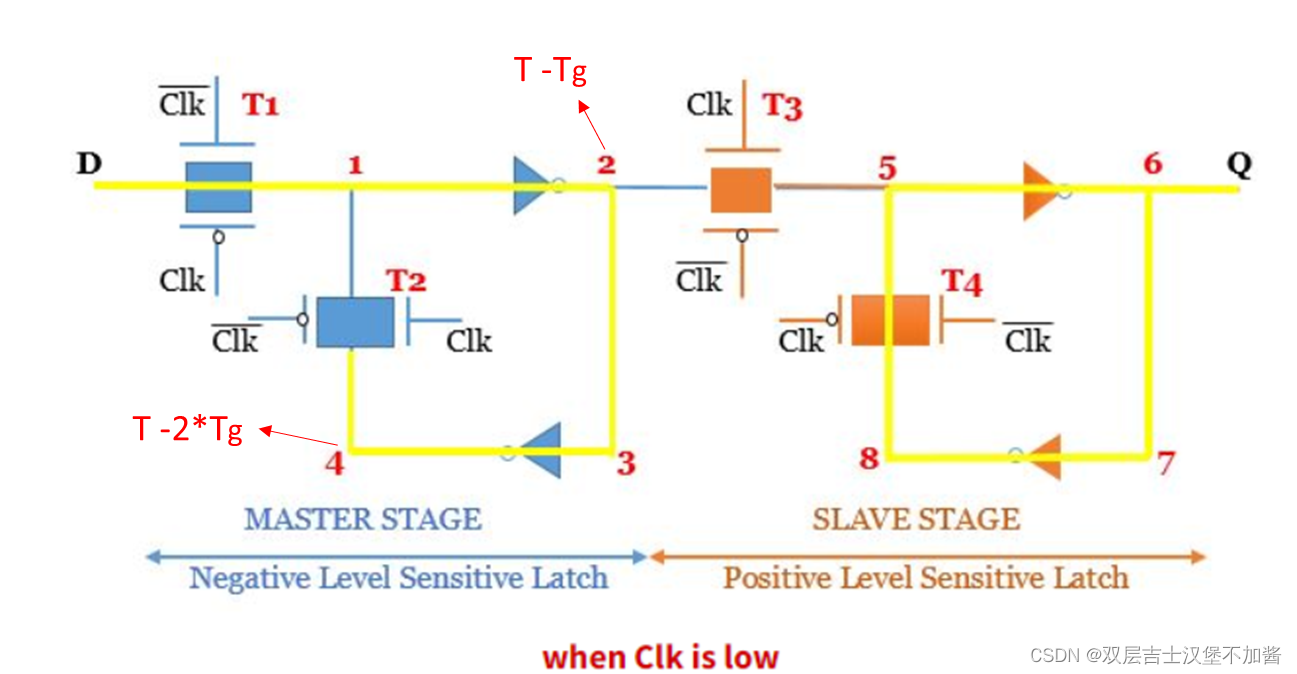

触发器由主从两个锁存器构成,在时钟为低的时候,T1传输门打开,主锁存器工作,可以看出来,D输入信号经过了两个门电路的延时才到达4,如下图所示

为什么会存在这个建立时间的要求呢,问题就出在这两个门电路的延时上面,我们把门电路延时定义为Tg

假设此时正好处在时钟上升沿的那个时刻T,那么此时2点处的数据是T-Tg时刻的数据,4点处的数据是T-2*Tg处的,如果这两处数据不同,锁存器无法正确锁存,因此setup时间要求在采样前一段时间就保持稳定。

那么为什么会有锁存时间要求呢,因为T1这个传输门,假设传输门在T时刻就立刻关断,那么没有问题,保持时间可以是0,但是传输门关断需要时间,如果在关断这段时间数据发生了变化,同样的主锁存器也没锁存数据。

总结一下:

如果数据不满足建立时间或者保持时间的要求,锁存器可能无法锁存住数据,因此可能发生

1、Q的值不是D的值,数据错误

2、Q变稳定的时间超过了ck to q的shijian

3、Q稳定的值可能是随机的

二、亚稳态

当系统内只有一个时钟的时候,只要保证建立时间和保持时间满足要求,亚稳态就不会发生。

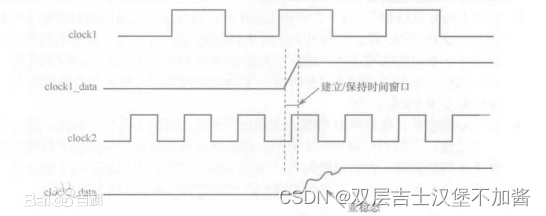

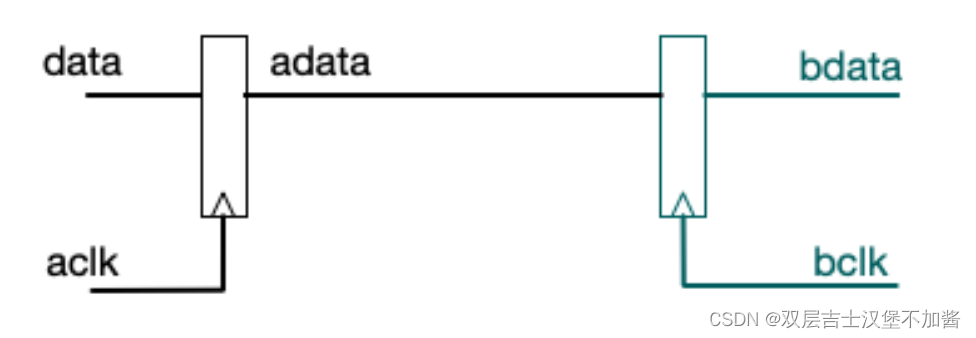

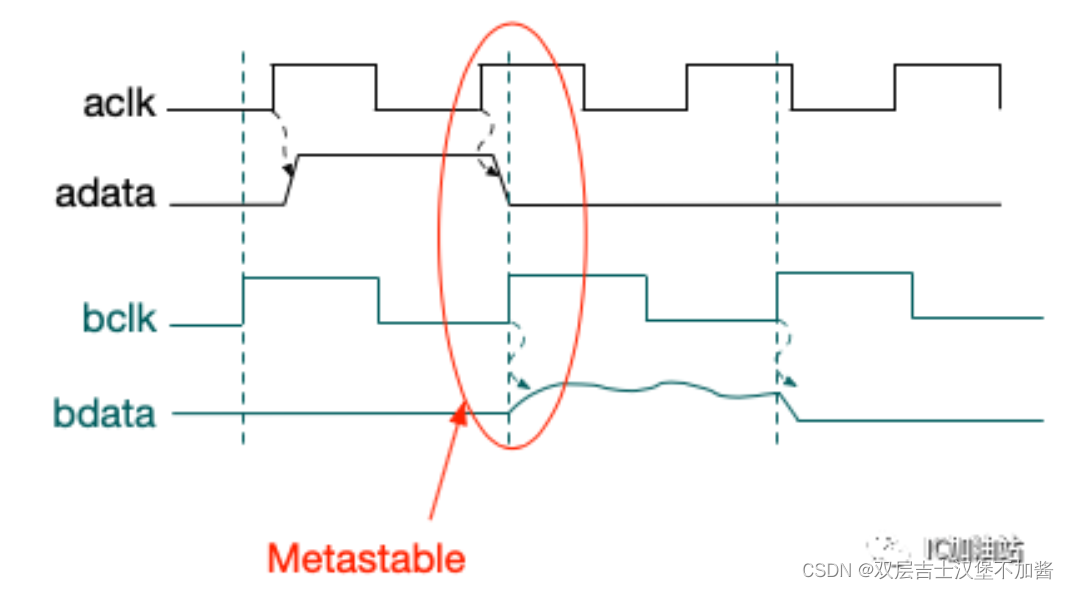

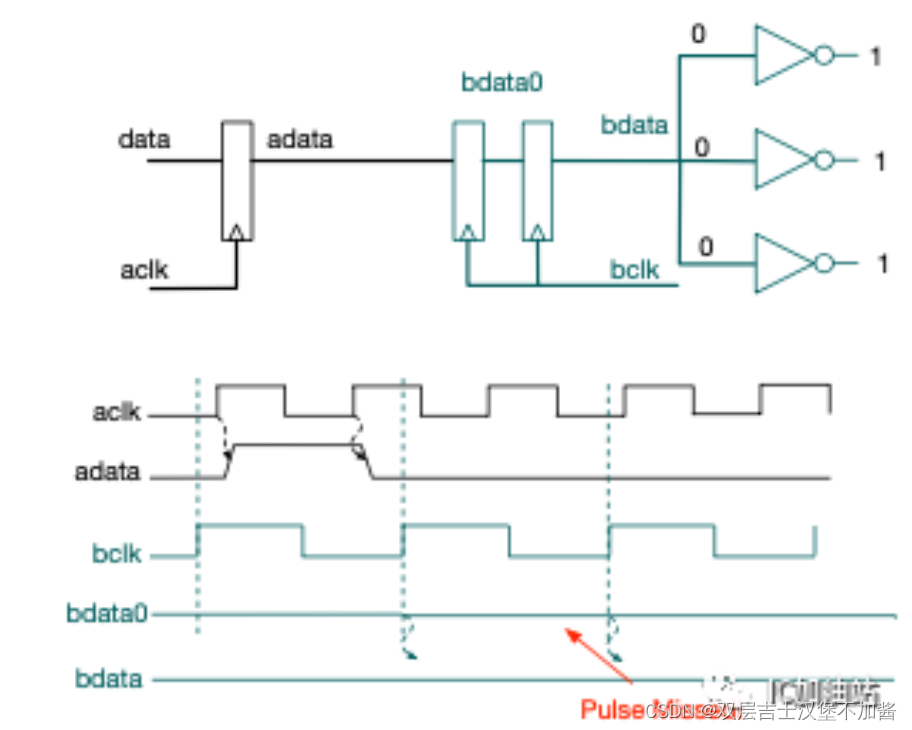

但是如果系统内存在两个时钟,彼此之间没有任何关系

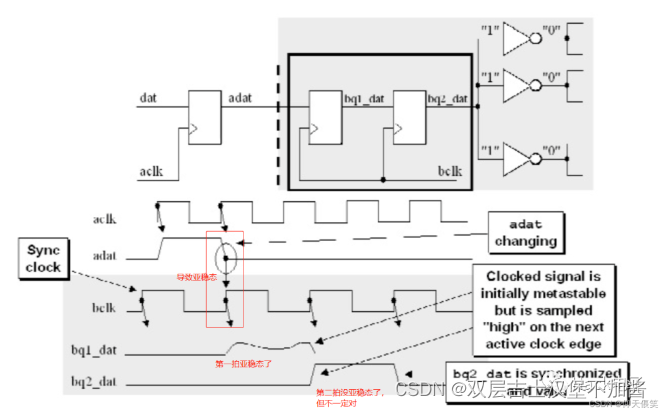

adata的数据相对aclk是有可能在任意时间发生变化的。这个时候b触发器,就很有可能发生亚稳态。那么如何解决亚稳态的传递呢?

在后级电路接上两个触发器,这样的话,就算第一个触发器发生了亚稳态,由于亚稳态最终会稳定,因此第二级的触发器最终能采样到稳定的信号,这样就确保了亚稳态不会向后传递,这里声明一个点,这种方法只能确保数据不发生亚稳态,但是不可以保证数据是正确的!

单比特信号同步要求

之前讲过打两拍保证亚稳态不传递下去,那么想让一个脉冲信号同步到另一个时钟域该怎么办呢?

1个fail test

这是一个单比特信号在进行跨时钟域的同步,但是这个信号有点短,没有碰见目标时钟域的沿,导致信号完全无法被同步。

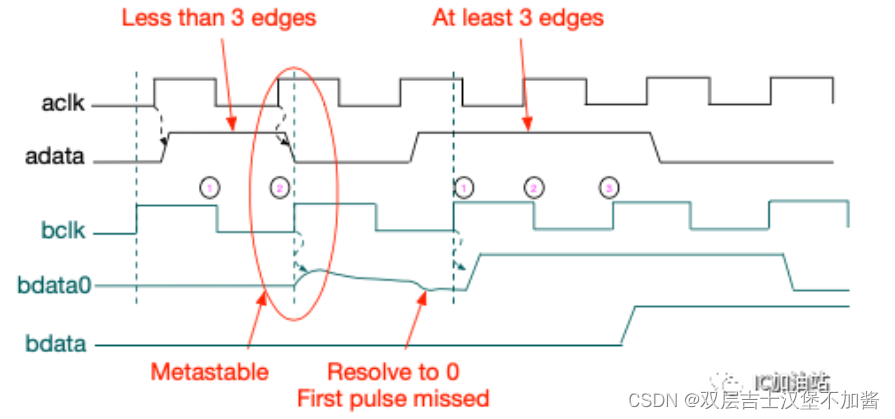

2 单比特信号同步要求

要求就是,信号必须稳定不变连续碰见目标时钟域的三个沿(上升或者下降)。

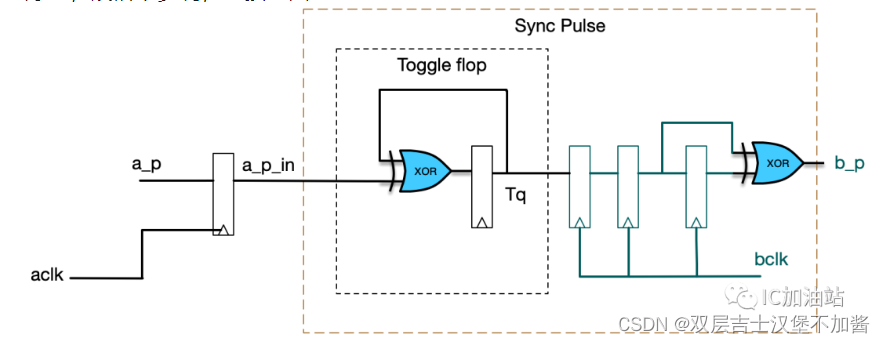

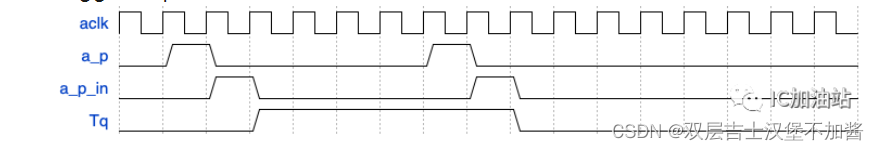

讲到这里,其实还是有问题,如果两个时钟域时钟频率不同,那么在a时钟域拉高1T的信号,到了b时钟域可能会拉高好几T,我们希望是是在a始终域一个单周期的脉冲到了b时钟域也还是单周期的一个脉冲。那么如何做呢,这里借用一种方案,把a时钟域的脉冲信号转换为level信号,使用打两拍同步这个level信号,在b时钟域将这个level信号转换为脉冲信号。

关键就是 toggle flop,当输入是一个单周期的脉冲时,toggle flop只会翻转一下。

这里就实现了plus信号向level信号的转换。由于这个level信号要做时钟域的同步,因此要求这个level信号至少持续3个沿,也就是两个plus之间的间隔要求持续三个沿。

总结

到这里,单笔特信号的跨时钟域同步就讲完了。总结一下:

1、使用打两拍的方法进行时钟域的同步,无法保证数据传递的正确性,只能保证亚稳态不继续传递下去

2、使用打两拍的方法进行时钟域的同步,被同步的信号至少要碰见目标时钟域的三个边沿,否则可能信号会被漏掉

3、如果想实现a时钟域产生一个脉冲,b时钟域也产生一个脉冲,可以使用将脉冲信号转换为level信号的办法,并在b时钟域将level信号反变为脉冲信号。

1817

1817

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?