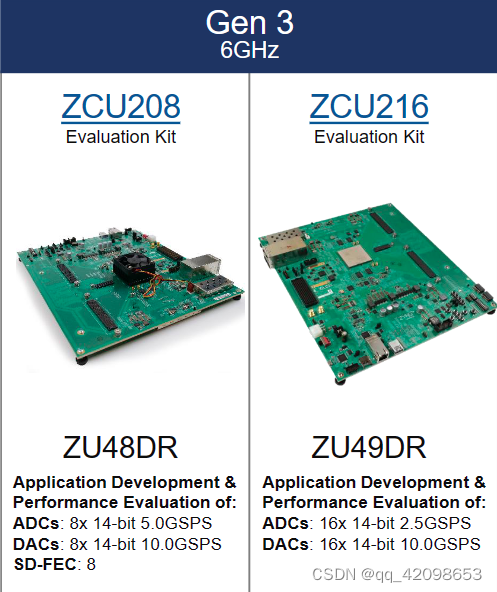

RFSoC——ZCU208 DAC部分

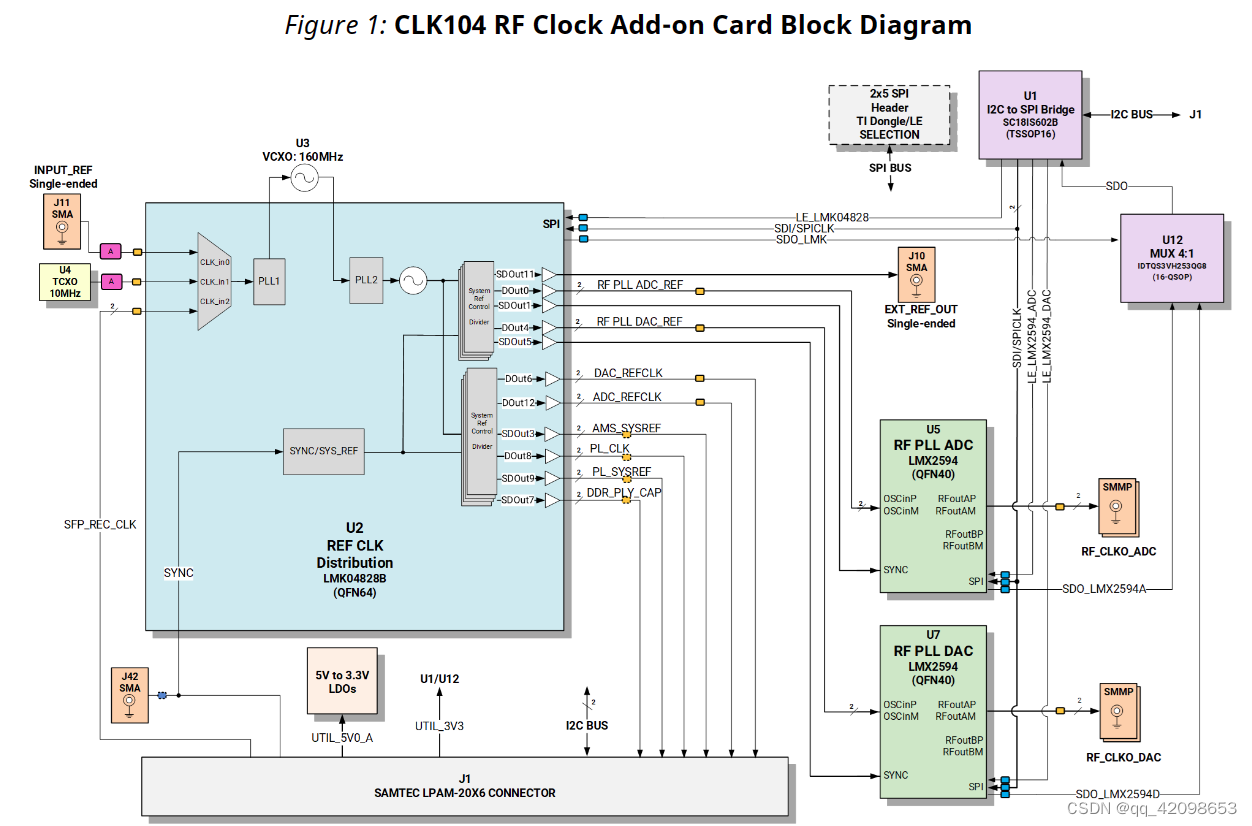

开发板结构

开发板分为主板:ZYNQ + 各种外设

时钟板(CLK104):通过主板一个单片机 MSP430 配置时钟频率,实际仅需要操作AMD 的 SCUI软件,SCUI使用时,windows系统必须设置为英文,软件安装参考:

射频板(XM655):将SAM线转成双端口,连接ADC/DAC的Tile,信号最高频率6G

DAC

ZCU208 ADC/DAC 均有8路输出通道,DAC采样率高达9个多G(10G不稳定),

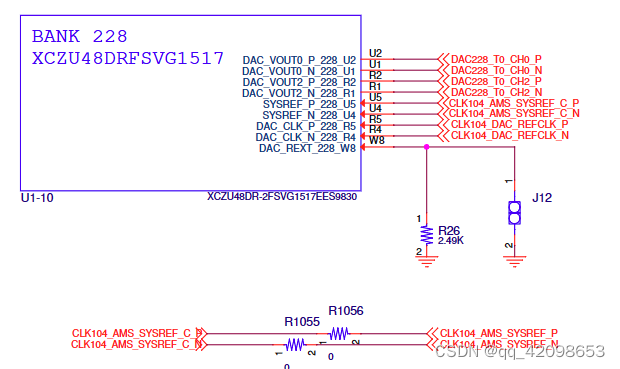

主板内DAC结构原理图

类似于GTY高速收发器BANK,ZCU208内部DAC有4个Tile ,每个Tile内有两个输出Channel

DAC_CLK:输入参考时钟,来自时钟板(CLK104)DAC_REFCLK【DOut6口】

SYSREF:参考同步时钟,来自时钟板(CLK104)AMS_SYSREF【SDOut3口】

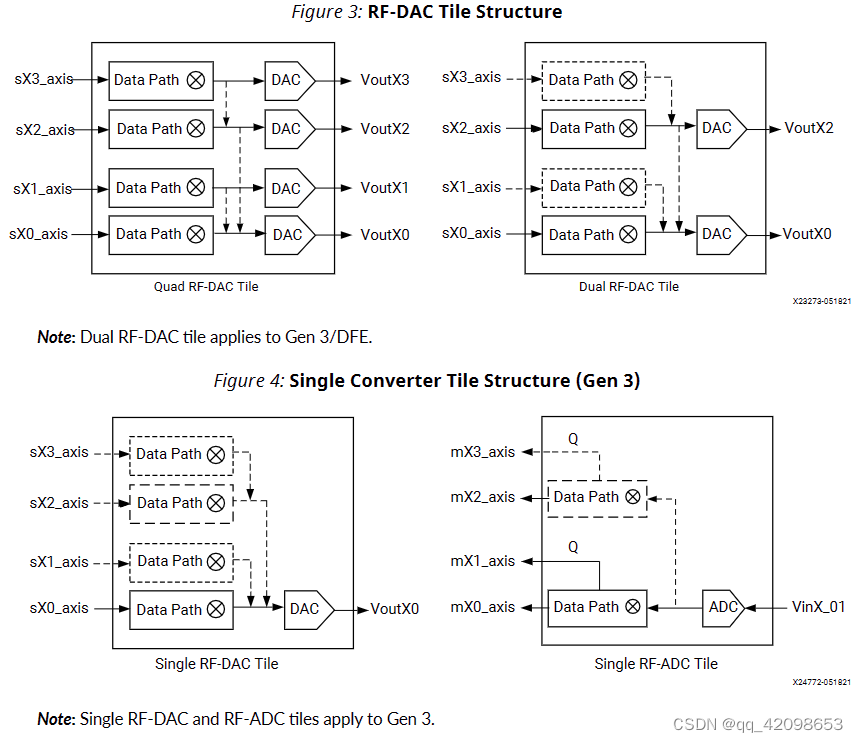

DAC IP 示意图

对应IP内部示意图:

ZCU208属于GEN3,因此通过IP可以配置为:

Dual RF-DAC Tile 即两通道输出

Single RF-DAC Tile 即单通道输出

DAC IP Tile时钟

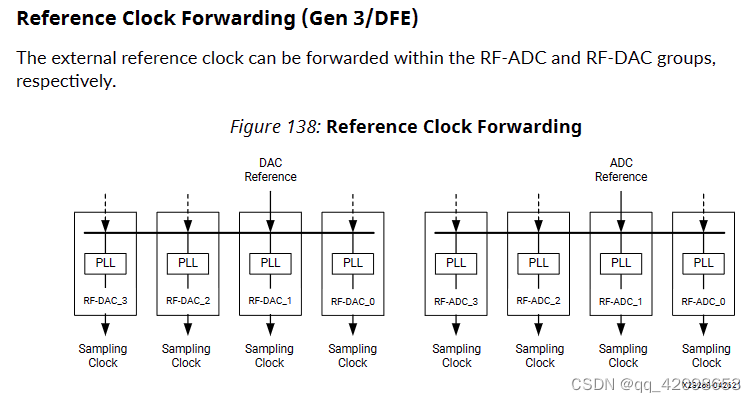

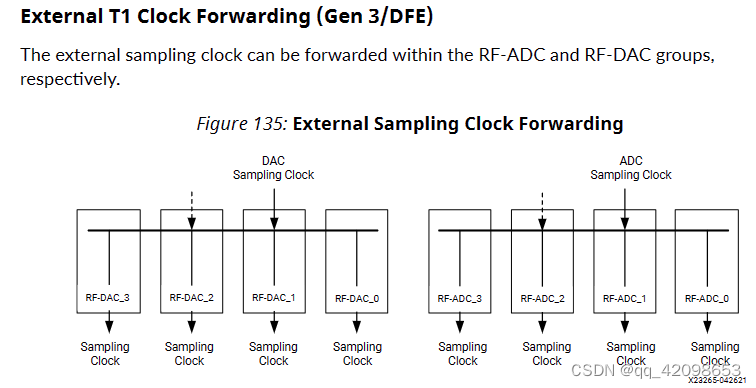

原理图中BANK228 与 BANK230具有来自时钟板提供的源时钟,

Tile内PLL启用时,源时钟作为参考时钟

Tile内PLL不启用时,源时钟作为采样时钟

同时,作为有源时钟的BANK228 与 BANK230,可以将时钟提供给其他Tile(通过IP中 Distribute Clock选项设置)

Distribute Clock (第3代): 设置片是否将分配时钟到设备上的其他片。

off : 不进行分配时钟。

Input Refclk: 当 PLL 启用时,输入参考时钟从 tile 转发。如果 PLL 未启用,则分配输入采样时钟。

PLL Output: 当PLL 被启用时,来自 PLL 的时钟输出从tile转发。

以下为常见时钟结构,此外AMD在PG269提供了更多cases。

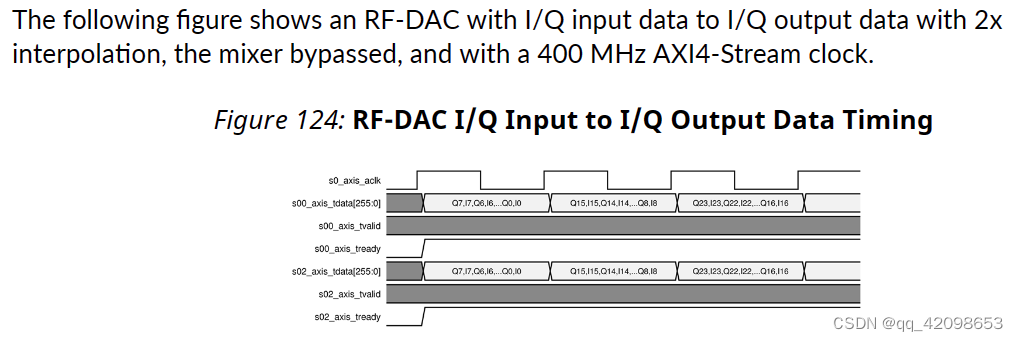

DAC IP AXI_stream 结构

具体见PG269中 RF-DAC IP Configuration部分

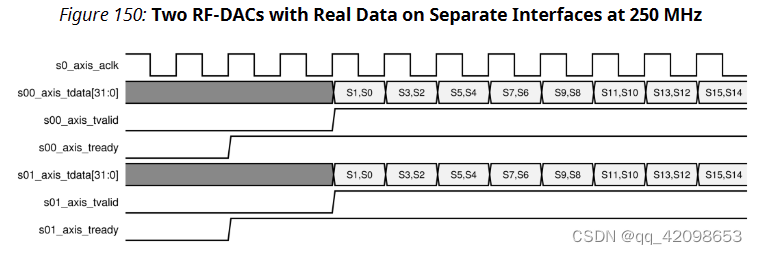

REAL DATA:

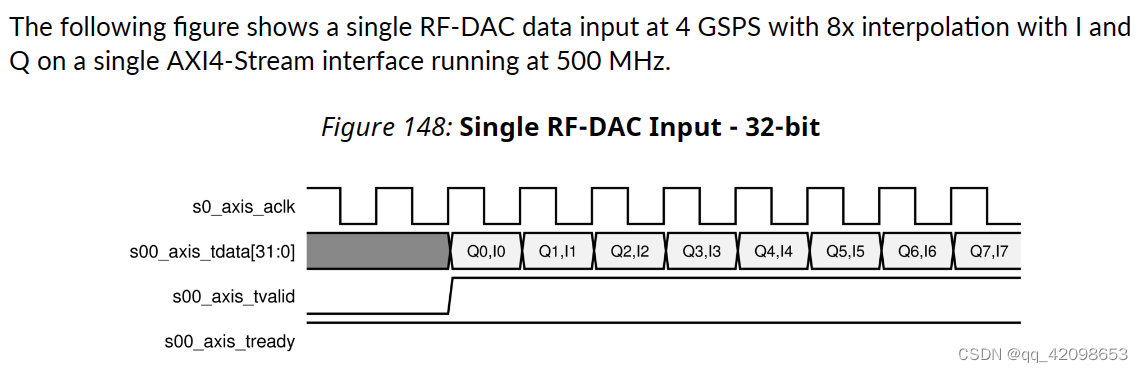

IQ DATA:

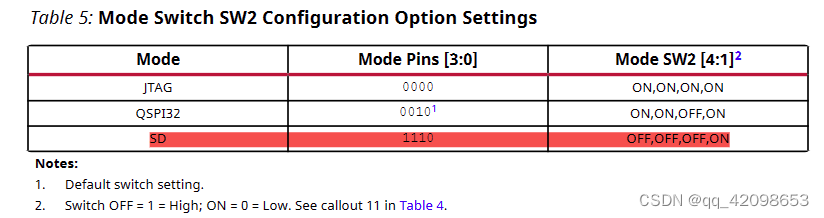

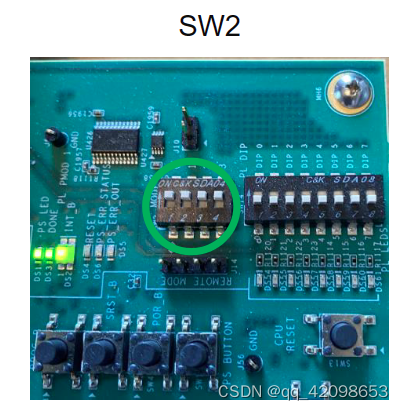

开发板启动

开发板有三种启动方式,由SW2控制:

1.JTAG:

2.SD卡

官方参考示例教程:link

快速上手示例,不具备开发灵活性

3.QSPI

DAC调试

官方建议配置DAC后,通过对应的Example Design基础上进行开发。

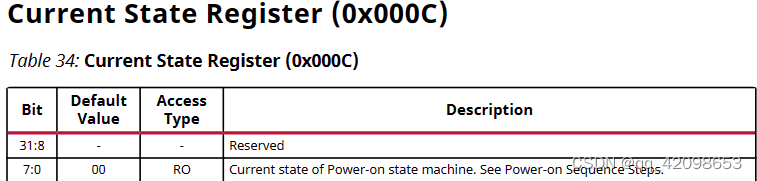

DAC IP内部通过AXI4_Lite总线,可以操作内部寄存器,由于没有PS开发,可以通过JTAG to AXI Master IP访问DAC内部寄存器。

JTAG to AXI Master: link

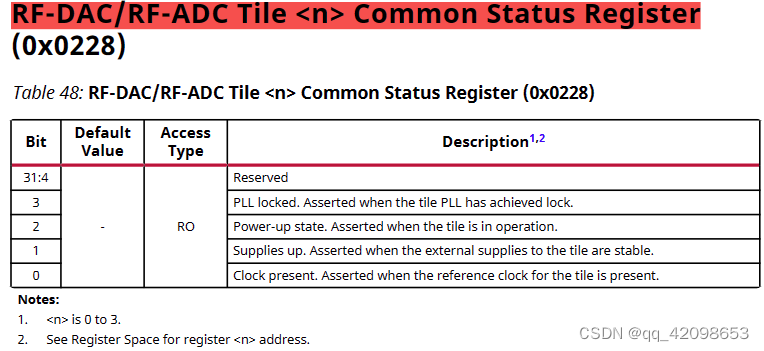

主要寄存器

TCL文件:

#-----------------------------------

# Command for AXI-Lite Write & Read

# create_hw_axi_txn <name> <hw_axi> [-address <arg>] [-data <arg>] [-size <arg>] -type <arg>

# [-len <arg>] [-burst <arg>] [-cache <arg>] [-id <arg>] [-quiet] [-verbose]

# - fixed : burst length(len) = 1

# data width(size) = 32

#-----------------------------------

set data_list ""

set num 1

# command data format : no. op address data

append data_list [format %4s no.]

append data_list [format %3s op]

append data_list [format %10s address]

append data_list [format "%8s\n" data]

#-----------------------------------

# Read CONTROL

#-----------------------------------

proc ReadReg { address } {

global data_list

global num

# axi read channel command

create_hw_axi_txn read_txn [get_hw_axis hw_axi_1] -address $address -type read

run_hw_axi read_txn

set read_value [lindex [report_hw_axi_txn read_txn] 1];

# return read data format : num r address read_value

append data_list [format %3i $num]

append data_list [format %4s r]

append data_list [format %10s $address]

append data_list [format "%10s\n" $read_value]

# complete one read transaction

delete_hw_axi_txn read_txn

incr num

}

#-----------------------------------

# Write CONTROL

#-----------------------------------

proc WriteReg { address data } {

global data_list

global num

# axi write channel command

create_hw_axi_txn write_txn [get_hw_axis hw_axi_1] -address $address -data $data -type write

run_hw_axi write_txn

set write_value [lindex [report_hw_axi_txn write_txn] 1];

# return write data format : num w address write_value

append data_list [format %3i $num]

append data_list [format %4s w]

append data_list [format %10s $address]

append data_list [format "%10s\n" $write_value]

# complete one write transaction

delete_hw_axi_txn write_txn

incr num

}

#-----------------------------------

# How to use the command

#-----------------------------------

# WriteReg 00000008 00000003

# ReadReg 00000008

DAC调试问题

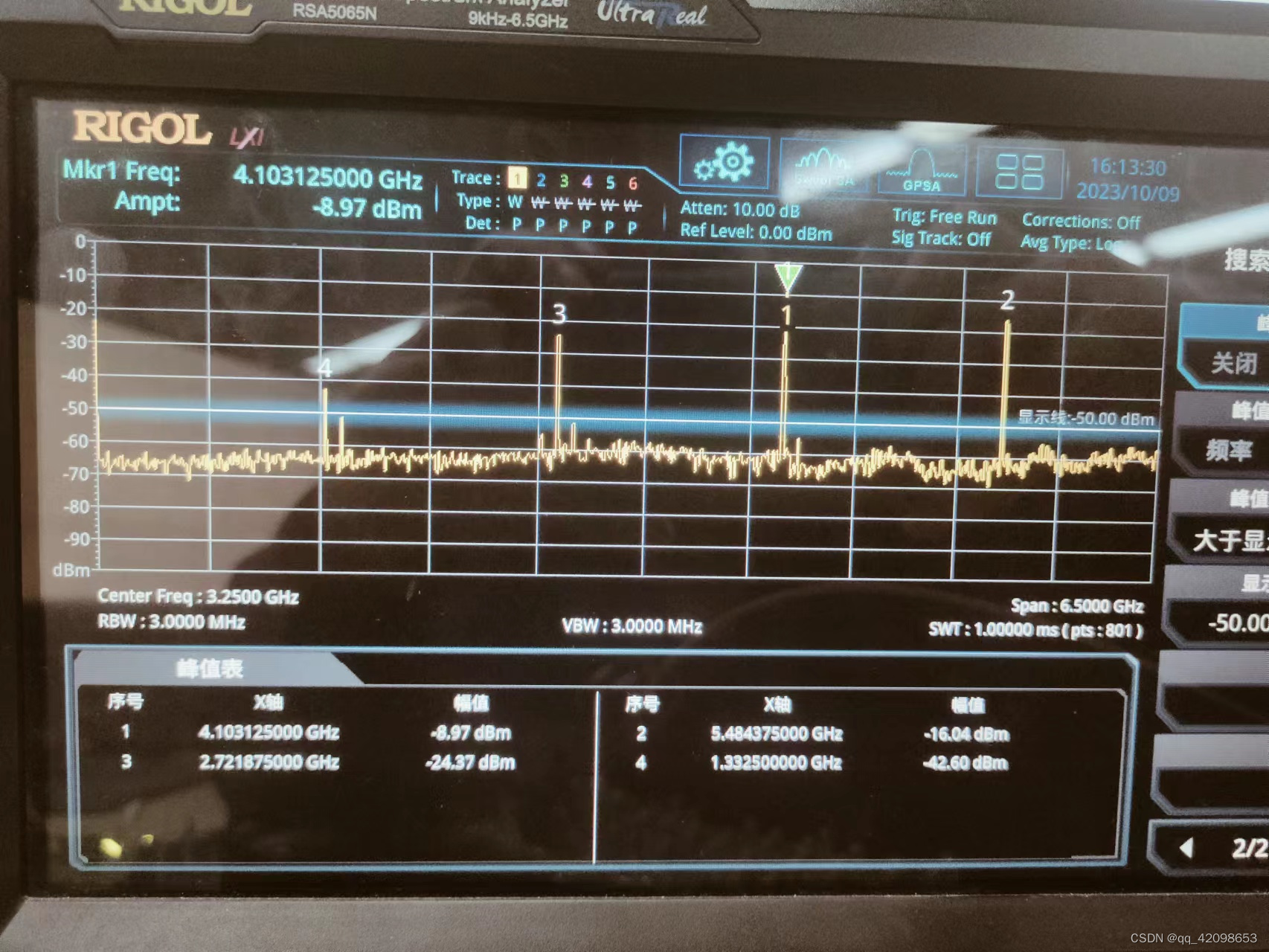

9.58464G采样率,4.1G单音信号,频谱输出,在MARK3,MARK4处,

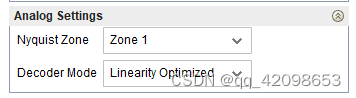

在IP选项中,应该选Linearity Optimized

官方回复:

Based on testing it has been observed that High Linearity mode is generally only beneficial for

Narrow band signals of << 5Mhz

Low carrier frequencies < 2Ghz

Near full scale signals (not backed off)

20mA mode

单音为窄带信号,推荐使用Linearity Optimized

改正后频谱仅显示4.1G单音及对应镜像信号。

3870

3870

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?